《UltraFast 设计方法时序收敛快捷参考指南》提供了以下分步骤流程, 用于根据《UltraFast设计方法指南》( UG949 )中的建议快速完成时序收敛:

1初始设计检查:在实现设计前审核资源利用率、逻辑层次和时序约束。

2时序基线设定:在每个实现步骤后检查并解决时序违例,从而帮助布线后收敛时序。

3时序违例解决:识别建立时间违例或保持时间违例的根源,并解决时序违例。

01

初始设计检查详细介绍

在赛灵思器件上实现设计,是一个自动化程度相当高的任务。但是,要实现更高的性能、解决时序或布线违例带来的编译问题,则是一项复杂且耗时的工作。仅根据简单的日志消息或由工具生成的实现后时序报告,可能难以明确失败原因。因此,按步骤进行设计开发和编译非常必要,其中就包括复查中间结果,以确保设计能继续执行下一个实现步骤。

第一步是确保所有的初始设计检查都已经完成。在下列层次复查检查结果:

由定制 RTL 构成或者由 Vivado HLS 生成的每个内核。注意:检查目标时钟频率约束是否现实。

与子系统逐一对应的每个主要层级,例如有多个内核、IP 块和连接逻辑的 Vivado IP integrator 模块框图。

包括所有主要功能和层级、I/O 接口、完整时钟电路、物理约束和时序约束的完整设计。

如果设计使用布局规划约束, 如超级逻辑区域( SLR )分配或分配给 Pblock 的逻辑,请复查每项物理约束的估算的资源利用率,确保符合资源利用率准则。

02

时序基线设定示例

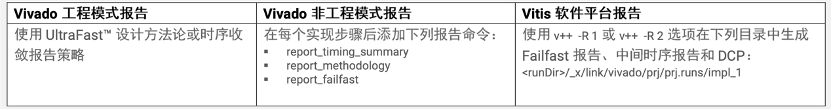

时序基线设定的目的是,通过在每个实现步骤后分析和解决时序问题,确保设计满足时序要求。在编译流程中,尽早纠正设计问题和约束问题能实现更高性能,并带来更广泛的影响。通过创建如下中间报告,在进入下一步前复查并解决时序违例:

03

分析建立时间违例流程

设计性能主要由三个因素决定:一、时钟偏差与时钟不确定性,主要包括时钟如何高效实现;二、逻辑延迟所涉及到每个时钟周期内遍历的逻辑量;三、信号线延迟或布线延迟,如Vivado 如何高效实现设计的布局布线。

使用时序路径或设计分析报告内的信息,有助于识别时序违例主要由哪些因素引发,以及确定如何迭代提升 QoR。

(提示:如果需要,可在每个步骤后打开 DCP 以生成更多报告,详细流程请查看完整版指南。)

04

解决保持时间违例的方法

避免保持时间要求为正值

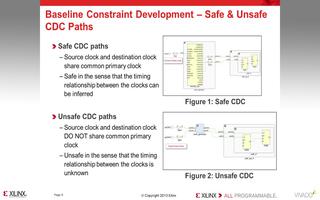

在使用多周期路径约束放宽建立时间检查时,需做到:

调整同一路径上的保持时间检查,以便在保持时间分析中使用相同的发送沿和捕获沿。否则会导致保持时间要求(一个或多个时钟周期)为正值,无法实序收敛。

指定端点管脚, 而不仅仅是单元或时钟。例如, 端点单元REGB有三个输入管脚:C、EN 和 D。只有 REGB/D 管脚需交由多周期路径例外来约束(时钟使能(EN)管脚不用),因为 EN 管脚在每个时钟周期都会发生改变。如果将约束连接至单元而不是管脚,那么所有有效的端点管脚(包括 EN 管脚)都在约束的考虑范围内。

在布线前降低 WHS 和 THS

严重的估算保持时间违例会增大布线难度, 且并非总能通过route_design解决。布局后phys_opt_design 命令提供多种保持时间修复选项:

在时序元件之间插入反向边缘触发寄存器会将时序路径分为两条半周期路径,从而显著减少保持时间违例。这种最优化只能在不劣化建立时序的情况下执行。

插入 LUT 1 缓冲器会导致数据路径延迟, 这样即可减少保持时间违例,而不会造成建立时间违例。

责任编辑:haq

-

Xilinx

+关注

关注

72文章

2174浏览量

123132 -

时序设计

+关注

关注

0文章

21浏览量

43962

原文标题:UltraFast 设计方法时序收敛参考指南

文章出处:【微信号:赛灵思,微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

用于Vivado设计套件的 UltraFast设计方法指南

了解最新的UltraFast设计方法窍门与技巧

全新嵌入式教程、更新的 UltraFast 方法指南,现已上线!

基于MCMM技术IC时序收敛的快速实现

一文知道UltraFast嵌入式设计方法指南

Vivado Design Suite设计套件的UltraFast设计方法的介绍

UltraFAST设计方法指南(适用于Vivado Design Suite)

UltraFast设计方法时序收敛快捷参考指南(UG1292)

UltraFAST设计方法指南(适用于Vivado Design Suite)

UltraFast设计方法时序收敛快捷参考指南

UltraFast设计方法时序收敛快捷参考指南

评论