信号反射现象

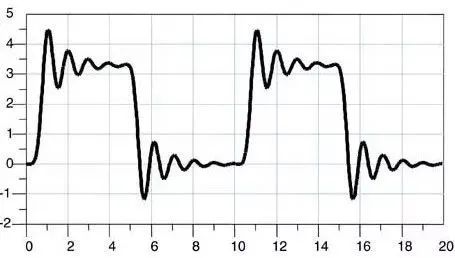

信号传输过程中感受到阻抗的变化,就会发生信号的反射。这个信号可能是驱动端发出的信号,也可能是远端反射回来的反射信号。根据反射系数的公式,当信号感受到阻抗变小,就会发生负反射,反射的负电压会使信号产生下冲。信号在驱动端和远端负载之间多次反射,其结果就是信号振铃。大多数芯片的输出阻抗都很低,如果输出阻抗小于PCB走线的特性阻抗,那么在没有源端端接的情况下,必然产生信号振铃。

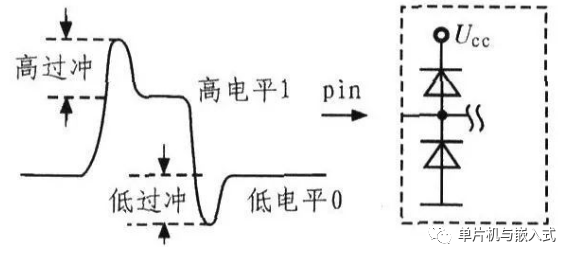

什么是过冲(overshoot):过冲就是第一个峰值或谷值超过设定电压——对于上升沿是指最高电压而对于下降沿是指最低电压。

什么是下冲(undershoot):下冲是指下一个谷值或峰值。过分的过冲能够引起保护二极管工作,导致过早地失效。过分的下冲能够引起假的时钟或数据错误(误作)。

过冲非常相关的是振铃,它紧随过冲发生,信号会跌落到低于稳态值,然后可能会反弹到高于稳态,这个过程可能持续一段时间,直到稳定接近于稳态。振铃持续的时间也叫做安定时间。振荡(ringing)和环绕振荡(rounding)的现象是反复出现过冲和下冲。

抑制信号反射等电路设计技巧

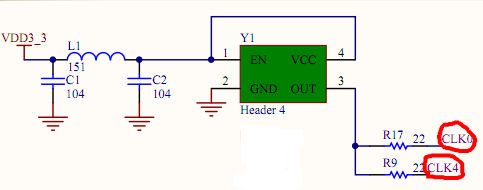

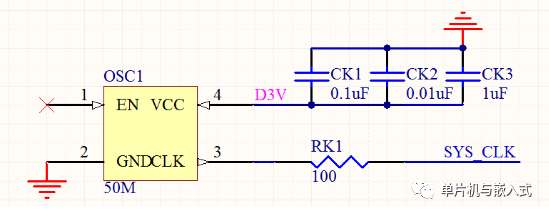

如果时钟信号链路比较长,为了解决信号反射问题,会在时钟输出信号上串接一个比如22或者33欧姆的小电阻。相关文章推荐:认识传输线的三个特性,特性阻抗、反射、阻抗匹配。

而且随着电阻的加大,振铃会消失,然而信号上升沿不再那么陡峭了,串联电阻是为了减小反射波,避免反射波叠加引起过冲。

这个解决方法叫阻抗匹配,阻抗在信号完整性问题中占据着极其重要的地位。

编辑:jq

-

电阻

+关注

关注

86文章

5509浏览量

171936 -

电路设计

+关注

关注

6673文章

2451浏览量

204190 -

欧姆

+关注

关注

0文章

82浏览量

20970

原文标题:信号反射问题与相关电路设计技巧

文章出处:【微信号:c-stm32,微信公众号:STM32嵌入式开发】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

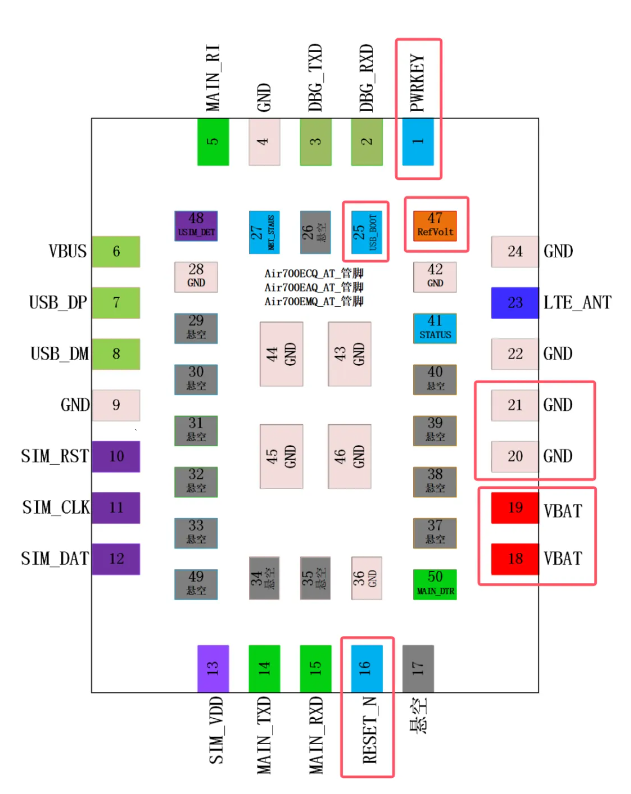

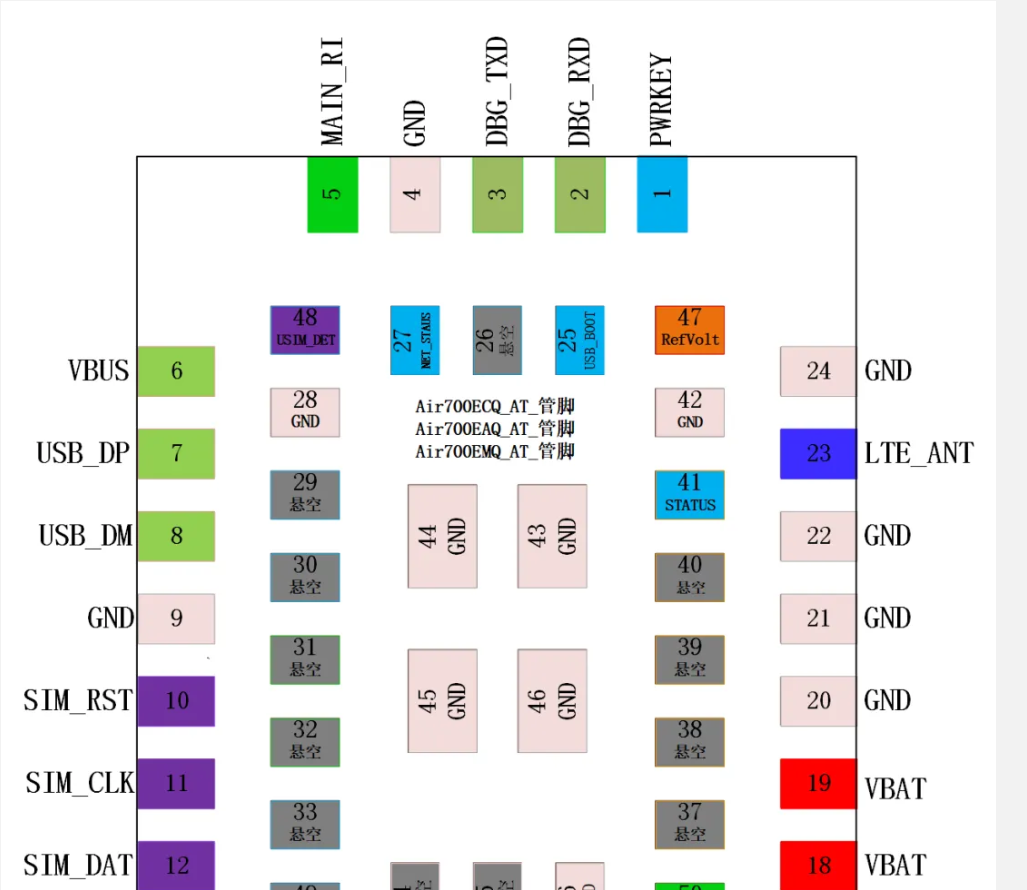

技术分享!蜂窝模组开机电路设计

射频电路设计的基本原则 射频信号干扰的解决方法

接口芯片的译码电路设计一般采用什么方法

高速电路设计与信号完整性分析

有一个信号处理电路要求设计pre-emphasis放大器,怎么操作?

TRF37D73对发送的射频信号可以起放大作用,对接收的射频信号可以起放大作用吗?

相关器抑制干扰信号的原理是什么

伺服电机的使能信号及其相关问题

探讨光耦在微处理器及相关电路中创新应用与实践

宽带放大器在CMUT阵列的超声反射成像研究中的应用

电路设计中的“地”

信号反射问题与相关电路设计相关技巧分享

信号反射问题与相关电路设计相关技巧分享

评论