简介

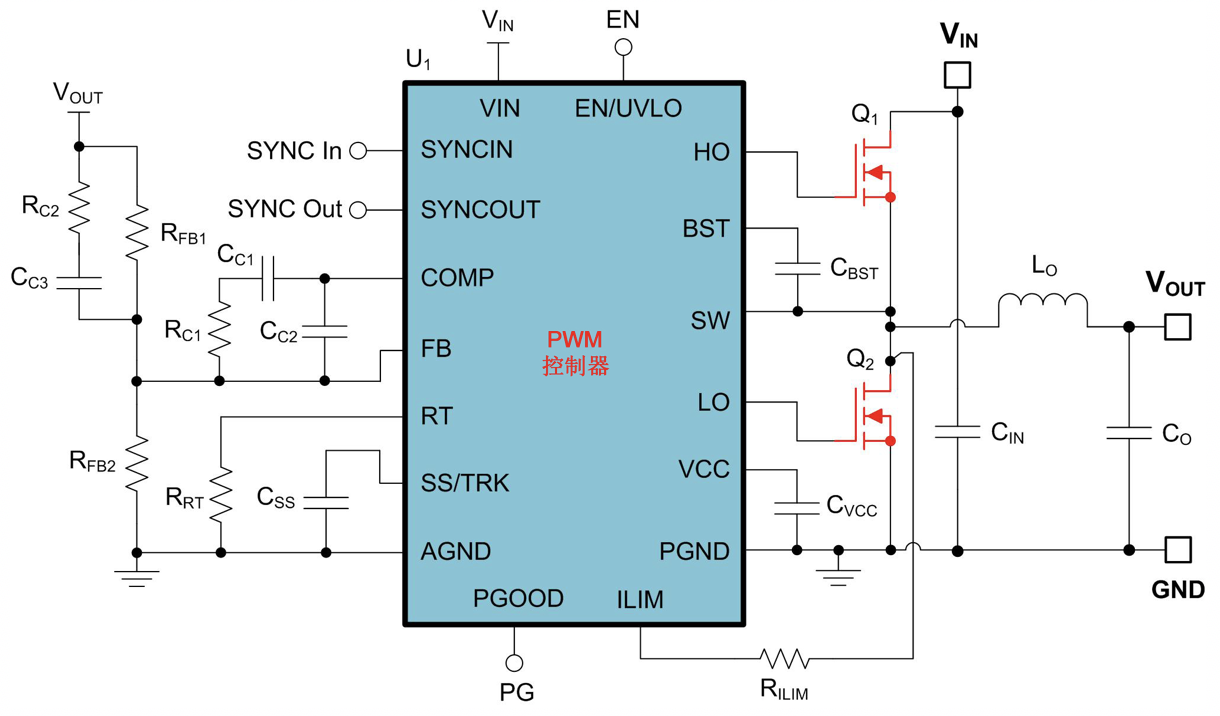

本系列文章的第 1 部分至第 5 部分中,介绍了抑制传导和辐射电磁干扰 (EMI) 的实用指南和示例,尤其是针对采用单片集成功率 MOSFET 的 DC/DC 转换器解决方案进行了详细介绍。在此基础上,本文继续探讨使用控制器驱动分立式高、低侧功率 MOSFET 对的 DC/DC 稳压器电路适用的 EMI 的抑制技术。使用控制器(例如图 1 所示同步降压稳压器电路中的控制器)的实现方案具有诸多优点,包括能够增强电流性能,改善散热性能,以及提高设计选择、元器件选型和所实现功能的灵活性。

图 1:驱动功率 MOSFET Q1 和 Q2 的同步降压控制器的原理图

然而,从 EMI 角度来看,采用分立式 FET 的控制器解决方案与采用集成 FET 的转换器相比,更具挑战性。主要有两方面的考量因素。首先,在紧凑性方面,采用 MOSFET 和控制器的功率级的印刷电路板 (PCB) 布局比不上采用优化引脚布局和内部栅极驱动器的功率转换器集成电路 (IC) 。其次,对于死区时间管理,在 MOSFET 开关时间在额定范围的转换器中通常更精确。因此,体二极管导通时间更短,从而能够改善开关性能并降低与反向恢复相关的噪声。

本文提供与采用 MOSFET 和控制器及半桥设计的多层 PCB 相关指南,以实现出色的 EMI 性能。当务之急是谨慎选择功率级元器件和适合的 PCB 布局,最大程度地减小关键回路寄生电感。布局示例表明,可以在不牺牲效率或热性能指标的情况下减少传导电磁辐射。

迎接EMI相关挑战

产生 EMI 的三个基本要素包括:电噪声源、耦合路径及受扰接收器。应对其中一个或所有基本要素,可以实现干扰抑制,从而实现合电磁兼容性 (EMC)。在实践中,可以采用多种技术中断耦合路径和/或强化可能的受扰电路,例如插入 EMI 滤波器来抑制传导干扰,借助屏蔽来降低辐射干扰等。

对于与降压稳压器的不连续输入电流(或升压稳压器的不连续输出电流)相关的低频 EMI 频谱幅值,采用传统的滤波器级进行处理相对容易。然而,与开关换向期间电压和电流的尖锐边缘相关的高 dv/dt 以及 di/dt 会产生谐波分量,从而导致出现更大的问题。高电流栅极驱动器(在电压低于 100V 时,通常集成在控制器中)可以以极高的速度开关功率 MOSFET。传统硅 FET 的转换率通常大于 10V/ns和 1A/ns,基于氮化镓 (GaN) 的器件转换率可能更高。我对本文第 2 部分中梯形开关波形的时域特性与其频谱成分之间的关系进行了研究,阐述了波形的最陡斜率决定高频频谱的渐近包络,因此,采用降低 dv/dt 和 di/dt 的方法有助于降低产生 EMI 的可能性。

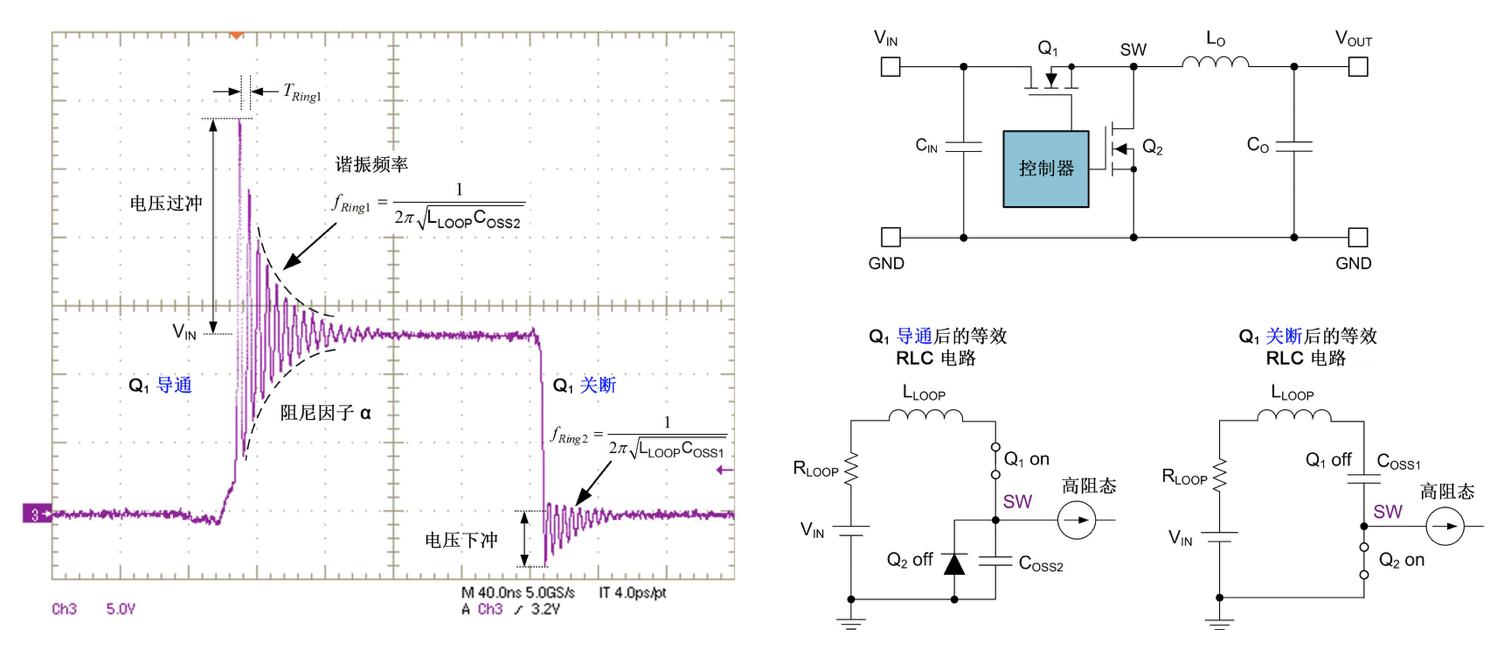

除了电压和电流的尖锐边沿之外,与开关波形相关的过冲/下冲及随后产生的振铃也非常棘手。图 2 显示了硬开关同步降压稳压器的开关节点电压波形。开关节点电压振铃频率范围为 50MHz 至 250MHz,具体取决于寄生功率回路电感的谐振 (LLOOP)及 MOSFET 输出电容 (COSS)。此类高频分量可以通过近场耦合传播到输出总线、周边元器件或输入电源线,并且难以通过传统滤波衰减。同步 MOSFET 体二极管反向恢复存在类似的负面作用,当二极管恢复电流流入寄生回路电感时,振铃电压升高。

图 2:同步降压稳压器在 MOSFET 导通和关断转换期间的开关节点电压波形和等效电路

图 3 的原理图标出了降压调节器电路 [6] 的关键高频功率回路,代表了具有高转换率电流的电路元件。可以对升压、反相降压-升压、单端初级侧电感转换器 (SEPIC) 和其他拓扑进行类似检查。最大限度缩减功率回路的面积至关重要,原因是该参数与寄生电感和相关 H 场传播成正比。主要设计目标是通过减小寄生电感最大程度提升寄生 LC 谐振电路的谐振频率。由此,降低存储的无功能量总值,减少开关节点电压峰值过冲和振铃。此外,达到临界阻尼因子的等效电阻实际上更低,因此任何振铃都会更早衰减 - 在高频时的趋肤效应增大回路的寄生电阻时更是如此。

图 3 中,还显示了导通和关断期间高侧和低侧 MOSFET 的栅极驱动器回路。务必遵从功率级布局期间的特殊注意事项(下文讨论),确保功率回路、栅极回路和共源寄生电感都尽可能低。

实现低EMI的PCB布局设计

以下步骤总结了 DC/DC 稳压器中元器件位置和 PCB 布局的基本准则,以帮助尽可能降低噪声和 EMI 信号。其中一些步骤类似于第 5 部分中针对采用集成 MOSFET 的基于转换器的设计所介绍的步骤。在后续部分,我将提供 PCB 布局案例研究,探讨如何优化降压稳压器 EMI 特性。

布线及元器件排布

将所有功率级元器件排布在 PCB 顶部。

— 避免将开关节点覆铜和电感放在底部,以免对 EMI 测试装置的基准平面产生辐射。

将 VCC 或 BIAS 的旁路电容放置于靠近各自引脚的位置。

— 在将 AGND 引脚与 GND 相连之前,首先电路中连入 CVCC 和 CBIAS 电容。

将临近的自举电容与控制器的 BOOT 和 SW 引脚相连接。

— 利用邻近的接地覆铜屏蔽 CBST 电容和开关节点,降低共模噪声。

GND平面设计

将 PCB 分层板中的第 2 层接地平面尽可能放在靠近顶层功率级元器件的位置,以消除 H 场、降低寄生电感及屏蔽噪声。

使用位于顶层与第二层接地平面之间的低 z 轴间距获得最佳映像平面效果。

— 在 PCB 分层规范中将层间距指定为 6 mil。

输入和输出电容

放置降压稳压器的 CIN,尽量减小将 CIN 连接到功率 MOSFET 所形成的回路面积。对于升压稳压器和 SEPIC 稳压器的 COUT,同样建议如此操作。

— 功率回路分类为横向或纵向,具体取决于电容相对于 MOSFET 的放置位置。

CIN 和 COUT 的接地返回路径应由集中放置的顶层平面组成。

— 使用多个外部或内部 GND 平面连接 DC 电流路径。

使用外壳尺寸为 0402 或 0603 的低等效串联电感 (ESL) 陶瓷电容,并放在 MOSFET 附近,以最大限度地减小功率回路寄生电感。

电感和开关节点布局

将电感放置在靠近 MOSFET 的位置。

— 尽量减小开关节点覆铜多边形面积,从而尽量避免电容耦合及减小共模电流。覆铜区应仅覆盖电感焊盘并仅占用连接 MOSFET 端子所需的最小面积。

使用邻近的接地保护并通过屏蔽限制开关节点噪声。

检查电感点位置,确保与开关节点相连的绕组末端位于绕组几何结构内部的底部,由连接到 VOUT(降压稳压器)或 VIN(升压稳压器)的绕组的外层绕线提供屏蔽。

选择在封装下方设有端子的电感。

— 避免使用可能产生天线辐射效应的大型侧壁式端子。

尽可能使用电场屏蔽电感。将屏蔽端子与 PCB 接地平面相连。

栅极驱动器布线

将控制器放置在尽可能靠近功率 MOSFET 的位置。

— 连接 HO 和 SW 的栅极驱动器时,应分别采用最小的布线长度和最小的回路面积,直接连接到高侧 MOSFET 栅极和源极端子。

— 将 LO 的栅极驱动器直接连接到接地平面上方的低侧 MOSFET 栅极,并尽量减小介电间距。

— 对栅极驱动器进行正交布线,尽量减少功率回路与栅极回路之间的耦合。

EMI管理

连接 EMI 滤波器元器件时,应避免由电感和开关节点辐射产生的电场形成耦合。

— 如果 EMI 滤波器与功率级的分隔距离不足,可将 EMI 滤波器放在电路板上转换器的对侧。

在 EMI 滤波器下方的所有层上开口,以防寄生耦合路径影响滤波器的衰减特性。

根据需要,可添加一个与 CBOOT 串联的电阻(最好小于 10Ω),限制 MOSFET 导通速度,从而降低开关节点电压转换率,减少过冲和振铃。

— 自举电阻会改变驱动电流瞬变率,从而降低 MOSFET 导通期间的开关节点电压和电流转换率。

— 为提高灵活性,可以考虑使用具有栅极驱动器专用源极引脚和漏极引脚的控制器。

任何所需的开关节点缓冲电路都应根据每次开关转换时的瞬态电流峰值,占用最小的回路面积。

— 将封装尺寸最小的元器件连接到 SW(通常是电容),尽量降低其天线效应。

使用具有内部接地平面的多层 PCB,与双层设计相比,其性能得到显著提升。

— 避免阻断 MOSFET 附近的高频电流路径。

考虑采用金属外壳屏蔽优化辐射 EMI 性能。

— 屏蔽外壳可覆盖除 EMI 滤波器之外的所有功率级元器件,外壳与 PCB 上的 GND 相连,基本形成了一个带有 PCB 接地平面的法拉第笼。

DC/DC同步降压控制器案例研究

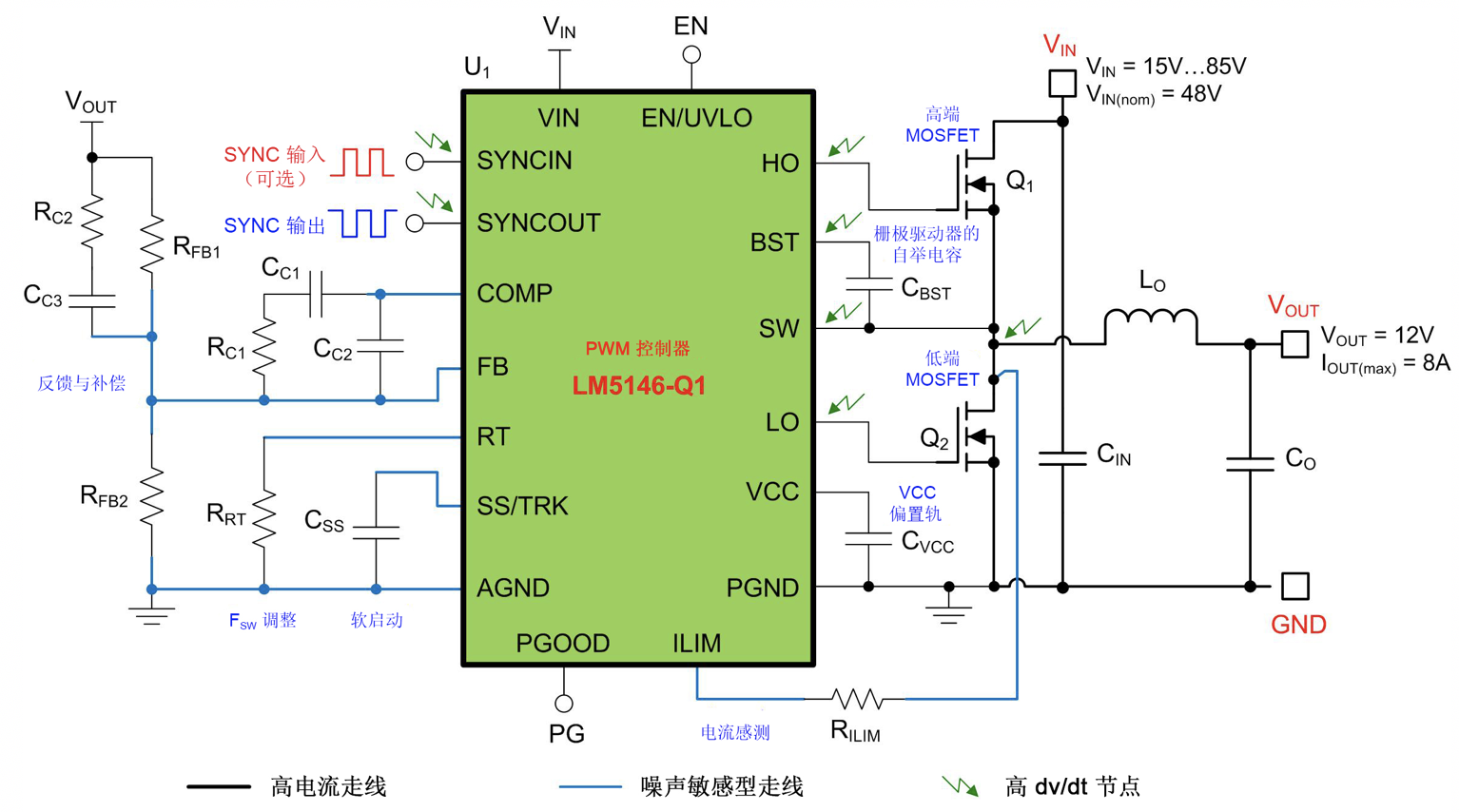

图 4 显示用于汽车应用或噪声敏感型工业应用的同步降压转换器电路 [6] 的原理图。其中融合了有助于改善 EMI 性能的多项特性,包括恒定开关频率操作、外部时钟同步以及通过高侧 MOSFET 受控导通实现的开关节点整形(转换率控制)。为了帮助实现最佳的 PCB 布局,原理图中将高电流走线(VIN、PGND、SW 连接)、噪声敏感型网络(FB、COMP、ILIM)和高 dv/dt 电路节点(SW、BST、HO、LO、SYNC)突出显示。高 di/dt 回路类似于图 3 中标示的回路。

图 4:DC/DC 降压稳压器原理图,其中标示出 PCB 布局的重要节点和走线

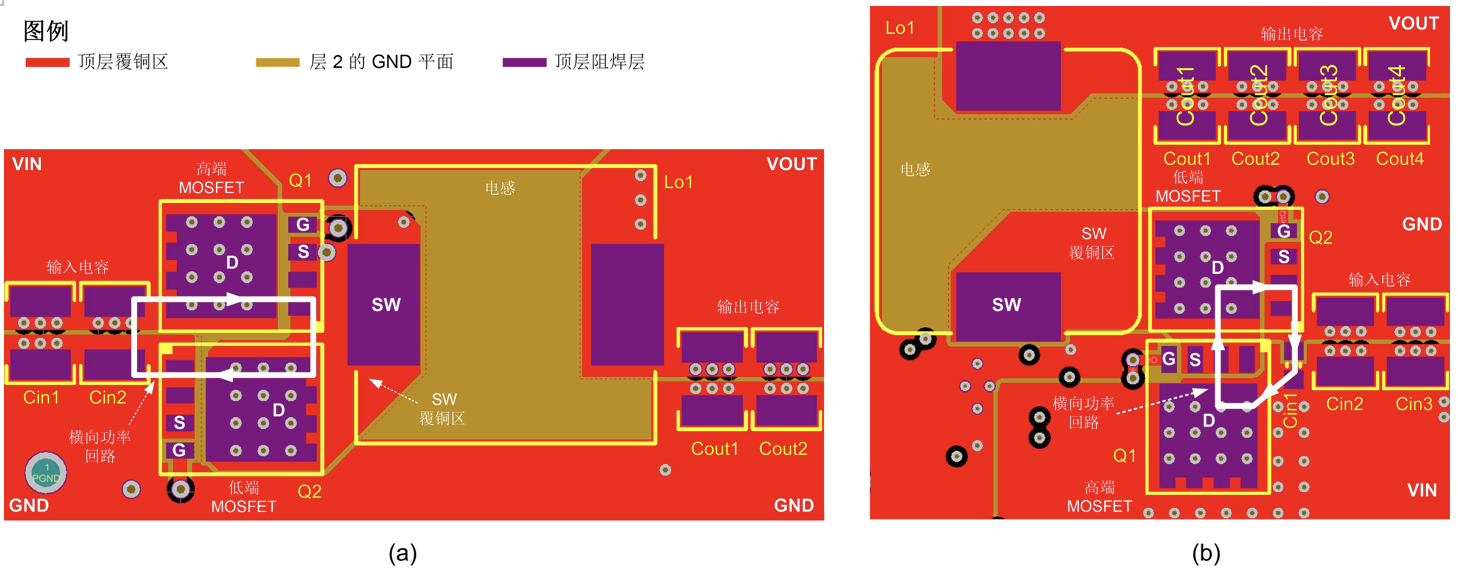

图 5 显示了功率 MOSFET 及输入电容的两种横向回路布局。功率级位于 PCB 顶层,控制器放置于底部。横向回路设计在顶层存在循环电流(图 5 中用白框表示),该电流在第二层接地平面上感应出映像电流,以抵消磁通,从而降低寄生回路电感。

更具体来说,修改图 5b 中的布局,使高侧 FET (Q1) 旋转 90 度。这样可以改善 Q1 的散热效果,从而更好地进行热管理,并可以在 MOSFET 附近方便地放置外壳尺寸为 0603 的低 ESL 电容 (Cin1),以实现高频去耦。考虑到功率级元器件的 U 型布局方向,较短返回连接的输出电容将放置在低侧 MOSFET。

图 5:两种传统的横向回路布局设计

改进后的PCB布局设计

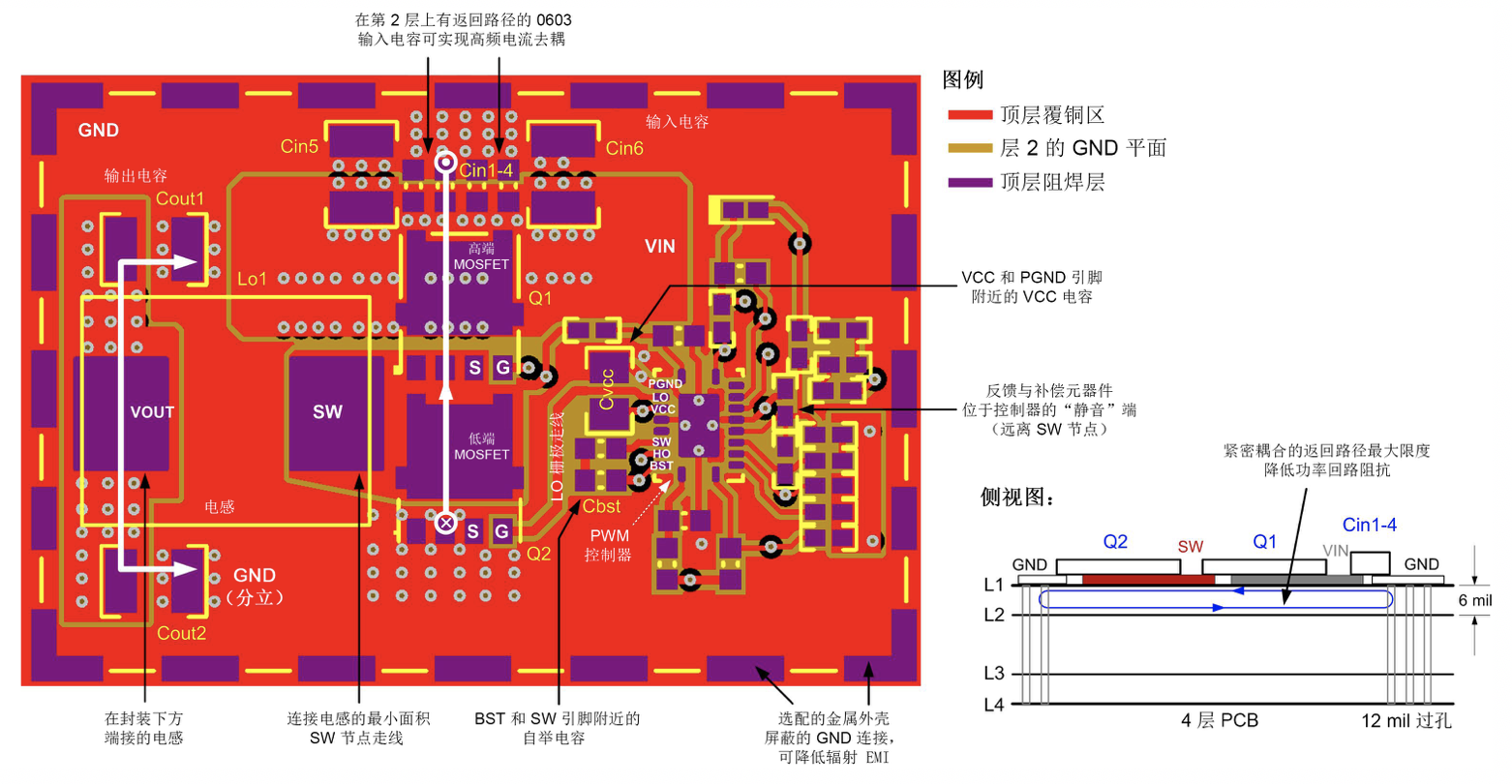

图 6 所示为改进后的布局,其优势是可减小功率回路面积,使多层结构达到高效率。该设计将 PCB 的第 2 层用作功率回路返回路径。该返回路径位于顶层的紧下方,形成小尺寸物理回路。垂直回路中的反向电流可使磁场自行消除,从而进一步减小寄生电感。图 6 中的侧视图展示了在多层 PCB 结构中形成小尺寸自行消除回路的概念。

将四个 0603 输入电容放置在尽可能接近高侧 MOSFET 的位置(位于图 6 中大容量输入去耦电容 CIN1 与 CIN2 之间),这四个电容具有较小的 0402 或 0603 外壳尺寸及较低的 ESL。这些电容的返回连接通过多个 12 mil 的过孔连接到第 2 层接地平面。第 2 层接地平面在 MOSFET 的紧下方提供了至低侧 MOSFET 源极端子的电流返回路径。

图 6:采用垂直功率回路设计的功率级和控制器的布局

此外,开关节点覆铜多边形区域只包含电感焊盘以及连接 MOSFET 所需的最小面积。接地平面覆铜区可屏蔽将 MOSFET 连接到电感端子的多边形覆铜区。SW 和 BST 的单层布局意味着 PCB 的底侧不会有 dv/dt 较高的过孔。这样可以避免在 EMI 测试期间,电场与基准接地平面耦合。最后,在电感两侧各使用一个陶瓷输出电容 COUT1 和 COUT2,优化输出电流回路。在输出端引出两个并联的返回路径可以将返回电流分成两部分,有助于减弱“地弹反射”效应。

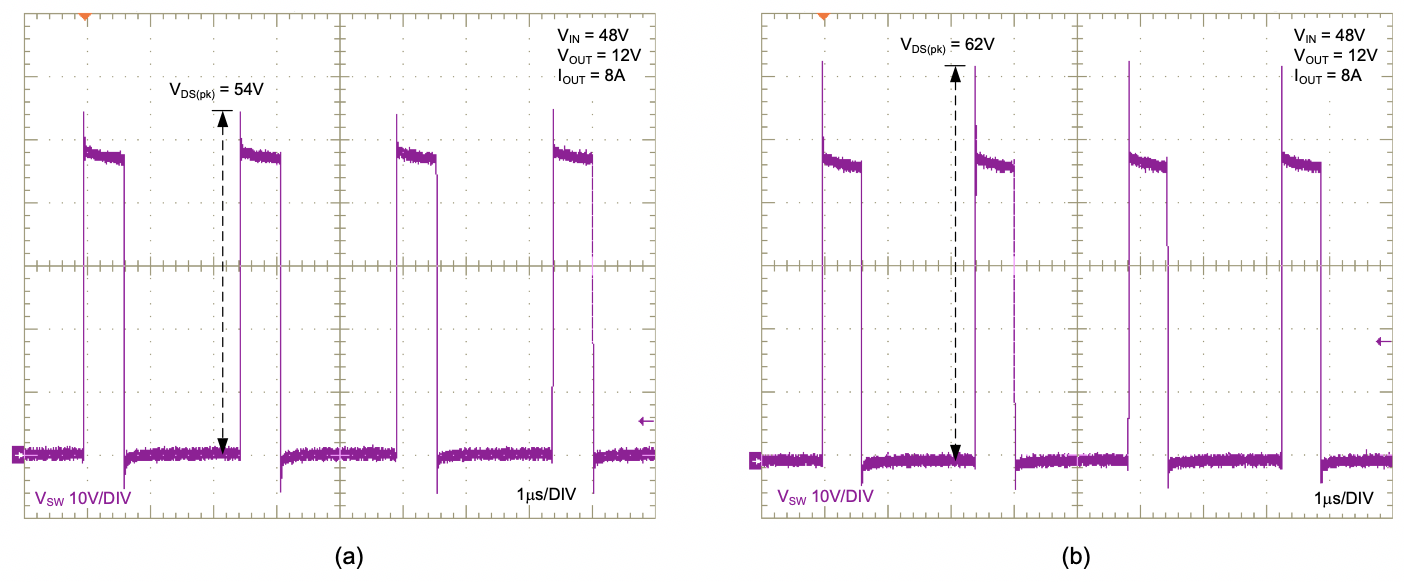

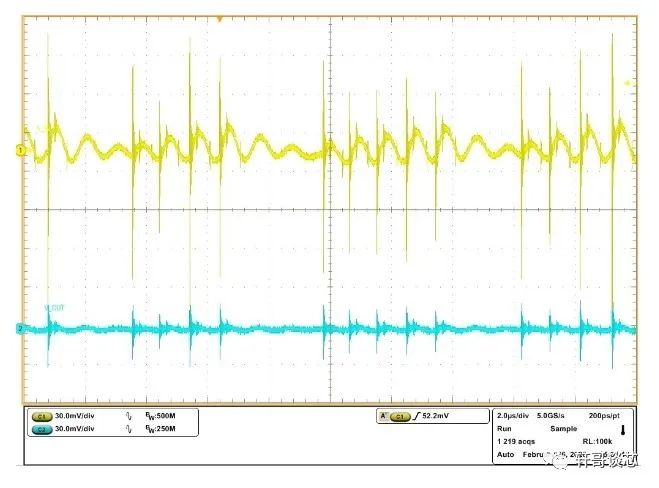

图 7a 所示为,图 4 中的稳压器采用图 6 中的优化布局时,使用宽带探头测得的开关节点电压波形。振铃不明显,只存在低幅度过冲和下冲,表示 50MHz 以上时 EMI 性能良好。为进行对比,图 7b 显示了采用图 5b 所示横向回路布局的类似测量结果。优化布局的峰值过冲降低约 8V。

图 7:VIN = 48V,IOUT = 8A 时的开关节点电压波形,(a) 为优化布局,(b) 为横向回路布局

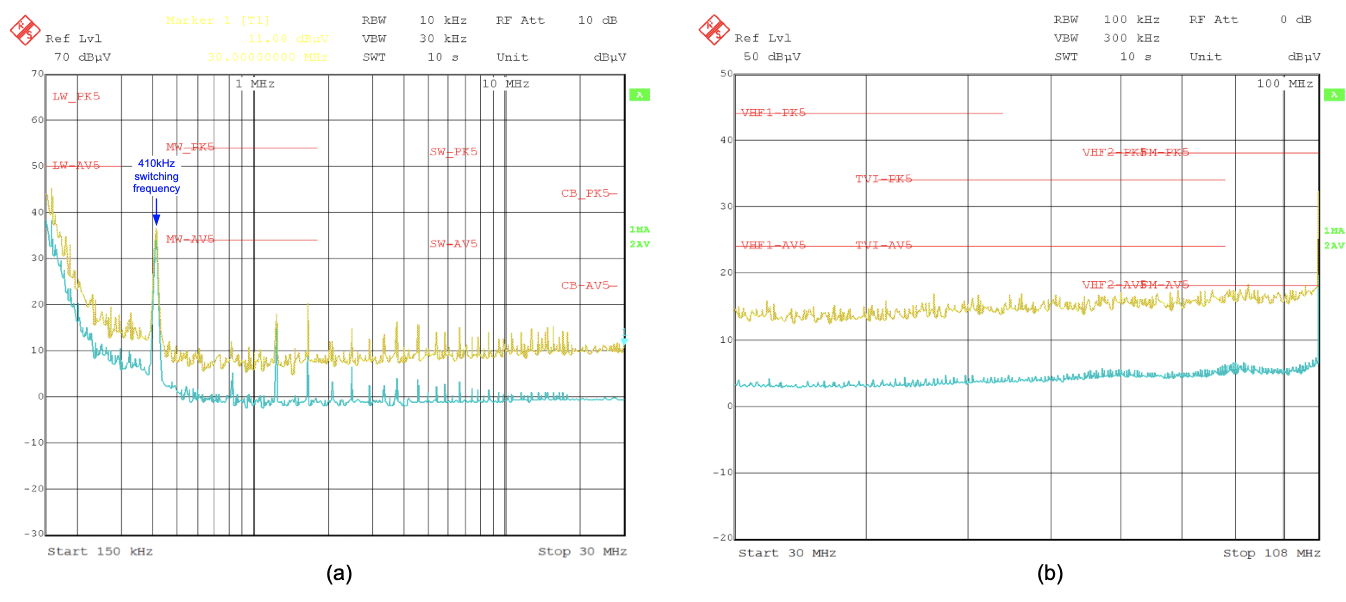

图 8 所示为图 6 中的转换器在 150kHz 至 108MHz 下测得的传导发射。使用 Rohde & Schwarz 的频谱分析仪,所得检测器扫描结果的峰值和平均值分别以黄色和蓝色表示。结果符合国际无线电干扰特别委员会 (CISPR) 25 5 类要求。红色限值图象为 5 类峰值和平均值限值(峰值限值通常比平均值限值高出 20dB)。

图 8:CISPR 25 传导发射测量结果,(a) 频率范围为 150kHz 至 30MHz,(b) 频率范围为 30MHz 至 108MHz

总结

功率半导体器件的开关瞬变是传导 EMI 和辐射 EMI 的主要来源。本文重点介绍在使用控制器和外部 MOSFET 的 DC/DC 稳压器电路中,有助于降低 EMI 的 PCB 布局。关于布局的主要建议包括,尽量减小布局中的电流“热回路”面积,避免阻断电流路径,采用具有内部接地平面的多层 PCB 结构实现屏蔽(性能远超双层 PCB),以差分对形式敷设短而直接的栅极驱动器走线,以及通过尽量减小开关节点覆铜区域面积来降低电场辐射耦合。

优化后的 PCB 布局有助于改善稳压器的 EMI 信号(与降低 EMI 的其他常用“修复”手段不同,不会牺牲效率或热性能)。尽管本文围绕 EMI 敏感的同步降压功率级进行论述,但只要能确定关键回路并实施文中建议采用的布局方法,通常可以将这些概念推广至任何 DC/DC 稳压器。

审核编辑:何安

-

电源管理

+关注

关注

115文章

6183浏览量

144505

发布评论请先 登录

相关推荐

ADI uModule DC/DC稳压器在线直播预告

LM26480应用说明1800评估套件-带双低噪声线性稳压器的双DC/DC降压稳压器

DC-DC Boost电路外围元器件如何选择?

具有休眠模式的高效开关电容降压DC/DC稳压器LM2770数据表

高频2.0A负载-降压DC-DC稳压器LM2832数据表

深刻理解DC-DC和LDO的原理和区别

高效低噪声 PFM DC/DC 升压稳压器FS2113数据手册

为什么DC-DC转换器这么有用?

DC/DC 稳压器电路适用的 EMI 的抑制技术

DC/DC 稳压器电路适用的 EMI 的抑制技术

评论