简介

本系列文章的第 1 部分至第 4 部分详细介绍了开关电源稳压器引起的传导发射和辐射发射,包括噪声产生机制、测量要求、频率范围、适用的测试限值、传播模式和寄生效应。在第 5 部分中,我将基于这一理论基础介绍抑制电磁干扰 (EMI) 的实用电路技术。

一般来说,电路原理图和印刷电路板 (PCB) 对于实现出色的 EMI 性能至关重要。第 3 部分重点强调通过谨慎的元器件选型和 PCB 布局尽量减小“功率回路”寄生电感的重要性。电源转换器集成电路 (IC) 的封装技术及其提供的 EMI 特定功能对此产生了巨大的影响。如第 2 部分所述,必须使用差模 (DM) 滤波方可将输入纹波电流的幅值充分降低至满足 EMI 合规性要求的水平。与此同时,如果需要抑制约 10MHz 以上的发射,通常使用共模 (CM) 滤波。在高频条件下,使用屏蔽也可以获得优异的结果。

本文主要介绍这些方面的内容,专门聚焦于带有集成功率 MOSFET 和控制器的转换器解决方案,提供抑制 EMI 的实例和应用指导。一般来说,转换器应在合理范围内超出传导 EMI 一定的裕度,为达到辐射限值预留空间。幸运的是,多数减少传导发射的步骤对于抑制辐射 EMI 同样有效。

了解EMI的相关挑战

DC/DC 转换器中的 EMI 主要由其快速开关的电压和电流特性所致。与转换器的不连续输入或输出电流相关的 EMI 相对容易处理,但更大的问题是开关电压 dv/dt 和电流 di/dt 中的谐波成分,以及与开关波形相关的振铃。

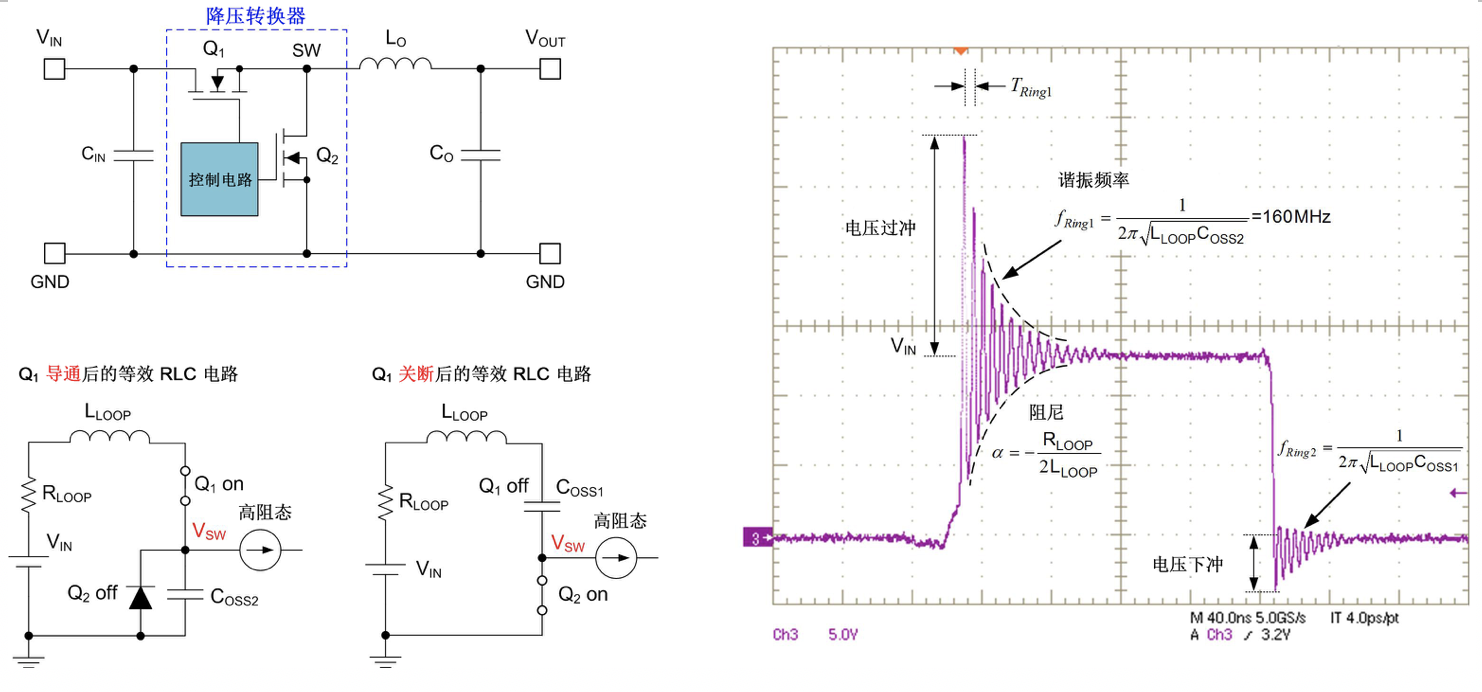

图 1 所示为存在噪声的同步降压转换器的开关 (SW) 电压波形。振铃频率范围为 50MHz 至 200MHz,具体取决于寄生效应。此类高频成分可以通过近场耦合传播到输入电源线、周边元器件或输出总线(如 USB 电缆)。体二极管反向恢复存在类似的问题,随着恢复电流流入寄生回路电感,振铃电压升高。

图 1:同步降压转换器在 MOSFET 导通和关断开关转换期间的开关节点电压波形和等效电路

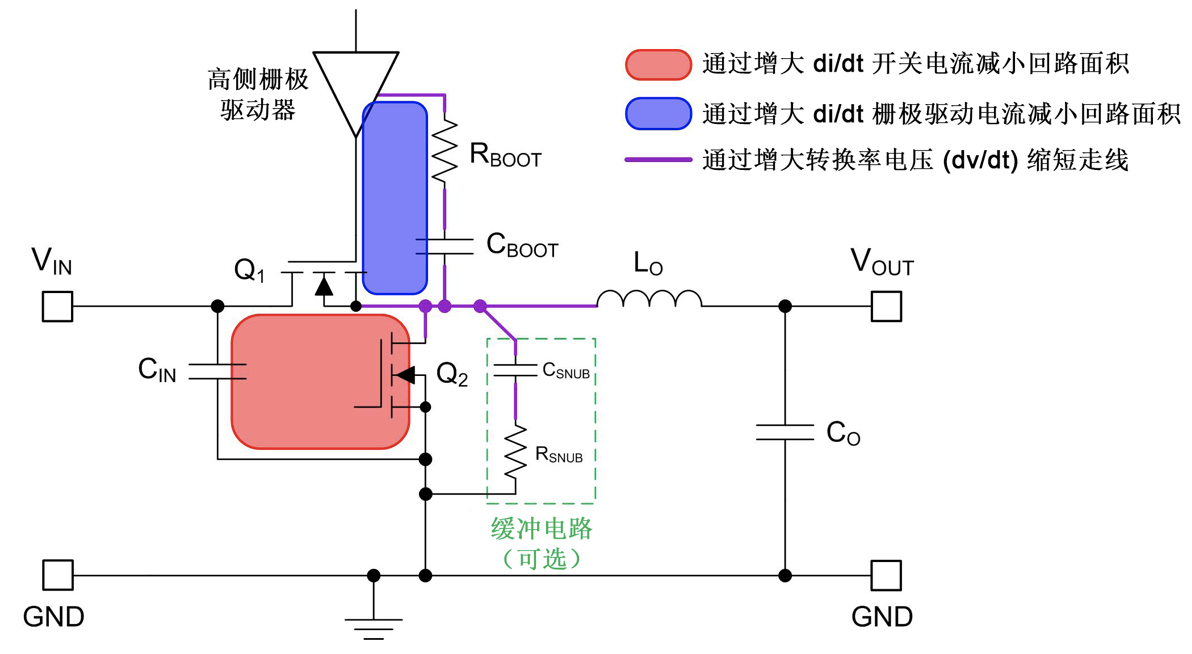

图 2 的原理图标识了降压转换器电路的两条重要回路。最大限度缩减电源回路的面积至关重要,原因是该参数与寄生电感和相关 H 场传播成正比。主要设计目标是通过减小寄生电感最大程度提升寄生 LC 谐振电路的谐振频率。此举可以降低存储的无功能量总值,减少开关电压峰值过冲。

图 2:简化的同步降压转换器原理图(针对 EMI 标出了关键回路和走线)

在图 2 所示的自举电容回路中,高侧 MOSFET 的导通速度由一个标记为 RBOOT 的可选串联自举电阻进行控制。自举电阻会改变驱动电流瞬变率,降低 MOSFET 导通期间的开关电压和电流转换率。另一种方法是在 SW 和 GND 之间添加一个缓冲电路。同理,该缓冲电路应根据每次开关转换时的瞬态电流尖峰,占用最小的回路面积。当然,缓冲电路和栅极电阻会增加开关功率损耗,需要在效率和 EMI 之间进行权衡。如果效率和散热性能同样非常重要,则需要使用其他技术解决 EMI 相关的挑战。

转换器的PCB布局

表 1 至表 5 总结了通过优化 PCB 布局及元器件排布削弱 DC/DC 转换器 EMI 信号的基本准则。我将在本文的后续部分提供一项 PCB 布局案例研究,探讨如何优化降压转换器的 EMI 特性。

表 1:布线及元器件排布。

| 1 |

将所有功率级元器件排布在 PCB 顶部。 - 避免将电感放在底部,以免对 EMI 测试装置的基准平面产生辐射。 |

| 2 |

将 VCC 或 BIAS 的旁路电容(从输出端)放置于靠近各自引脚的位置。 – 在将 AGND 引脚与 GND 相连之前,首先电路中连入 CVCC 和 CBIAS 电容。 |

| 3 |

将自举电容与邻近的 BOOT 和 SW 引脚相连接。 - 利用邻近的接地覆铜屏蔽 CBOOT 电容和开关节点,降低 CM 噪声。 |

表 2:GND 平面设计。

| 1 |

将 PCB 分层板中的第 2 层 GND 平面尽可能固定在靠近顶层的位置。 - 消除 H 场、降低寄生电感并屏蔽噪声。 |

| 2 |

使用位于顶层与第二层之间的低 z 轴间距获得最佳映像平面效果。 - 在 PCB 分层规范中将层间距定义为 6 mil。 |

表 3:输入和输出电容。

| 1 | 放置 CIN,尽量减小将 CIN 连接到 VIN 和 PGND 引脚所形成的回路面积。 |

| 2 |

CIN 和 COUT 的接地返回路径应由集中放置的顶层平面组成。 - 使用多个外部或内部 GND 平面连接 DC 电流路径。 |

| 3 | 在 VIN 和 PGND 附近使用外壳尺寸为 0402 或 0603 的陶瓷输入电容,以便最大限度减小寄生回路电感。 |

表 4.电感和开关节点布局。

| 1 |

将电感放置在 IC 的 SW 引脚附近。 - 尽量减小开关节点覆铜区域的表面积,避免电容过度耦合。 |

| 2 | 使用邻近的接地保护并通过屏蔽限制开关节点噪声。 |

| 3 | 检查电感点位置,确保与 SW 相连的绕组末端位于电感绕组几何结构内部的底部,由连接到 VOUT 的绕组的外层绕线提供屏蔽。 |

| 4 | 尽可能使用电场屏蔽电感。将屏蔽端子与 PCB 接地平面相连。 |

| 5 |

选择在封装下方设有端子的电感。 - 避免使用可能产生天线辐射效应的大型侧壁式端接。 |

表 5.EMI 管理。

| 1 |

将 EMI 滤波器元器件排布在远离开关节点的位置。 - 如果 EMI 滤波器与功率级的分隔距离不足,可将 EMI 滤波器放在电路板上转换器的对侧。 |

| 2 | 在 EMI 滤波器下方的所有层上开口,以防寄生电容路径影响滤波器的衰减特性。 |

| 3 | 根据需要,可添加一个与 CBOOT 串联的电阻(最好小于 10Ω),限制高侧 MOSFET 导通速度,从而降低开关节点电压转换率,减少过冲和振铃。 |

| 4 | 如果需要开关节点 RC 缓冲电路,可将封装最小的元器件与 SW(通常为电容)相连。 |

| 5 |

使用具有内部接地平面的四层 PCB,与双层设计相比,其性能得到显著提升。 - 避免阻断 IC 附近的高频电流路径。 |

EMI输入滤波器

图 3 所示为典型的多级 EMI 输入滤波器。低频和高频部分可提供 DM 噪声衰减,也可选择 p 级,通过 CM 扼流器提供 CM 衰减。标记为 CBULK 的电解电容具有固有的串联电阻 (ESR),可用于设置所需阻尼,降低转换器输入的有效品质因子,保持输入滤波器的稳定性。

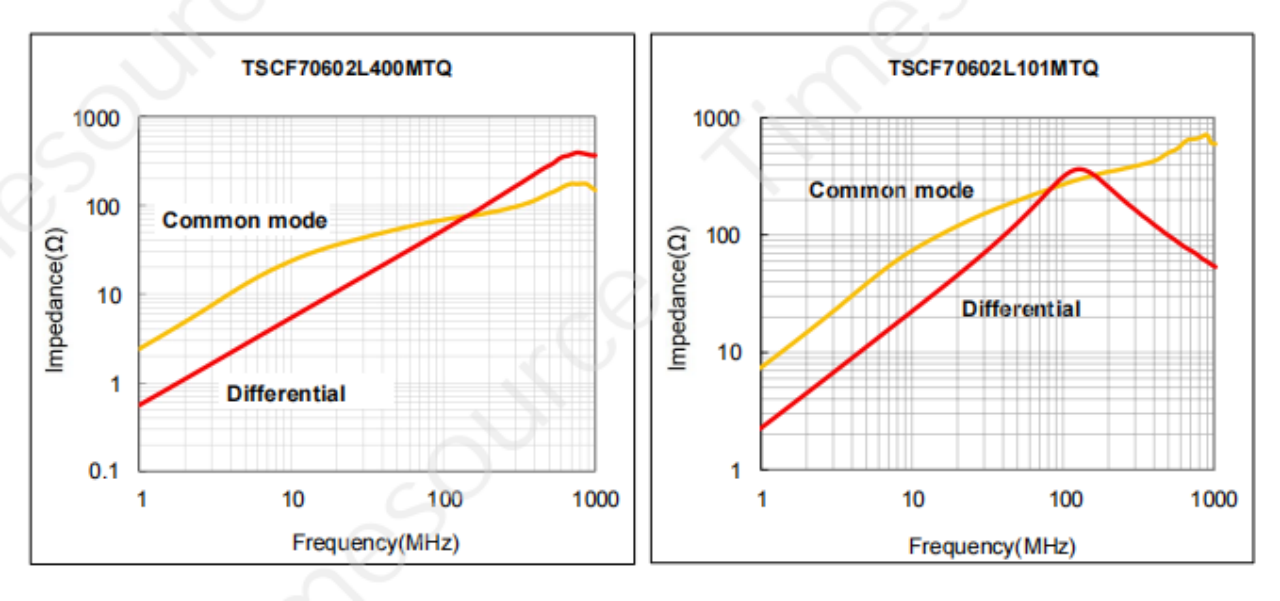

DM 电感的自谐振频率 (SRF) 限制滤波器第一级可实现的高频 DM 衰减。滤波器第二级通常至关重要,其使用铁氧体磁珠在高频条件下提供附加的 DM 衰减,此时额定阻抗通常为 100MHz。标记为 CF1 和 CF2 的陶瓷电容可将噪声分流到接地端。

DM 滤波器的电感一般设置为削弱基波和低频谐波的值。应使用尽可能小的电感来满足低频滤波要求,因为匝数较多的大电感具有较高的等效并联电容 (EPC),导致其 SRF 较高,影响其在高频下的性能。

标记为 LCM 的 CM 扼流器针对 CM 电流提供较高的阻抗,其泄漏电感也可提供 DM 衰减。然而,在部分要求接地连接必须保持完好的应用中,该元器件不适用,这些应用需要更安静的转换器设计,CM 扼流器不再是首选。

为了演示 CM 扼流器的效果,图 4 展示了德州仪器 (TI) LM53603,这是一款采用双层 PCB 的 36V、3A DC/DC 转换器解决方案 [7]。该器件的功率级位于顶层,EMI 输入滤波器则放置于底部。如图 4 中的布局所示,滤波器附近的接地平面覆铜区可借助过孔缝合提供屏蔽效果。此外,在滤波器级以下的所有层中插入敷铜层切口,可避免 VIN 和 GND 走线之间产生寄生电容,从而为噪声电流提供绕过 CM 扼流器的路径并让步于滤波器的阻抗特性。

图 5 所示为国际无线电干扰特别委员会 (CISPR) 25 针对图 4 的转换器设计在 150kHz 至 108MHz 之间进行的传导发射测量。我们提供了使用与不使用 CM 扼流器两种情况下的测量结果。使用 Rohde & Schwarz 的频谱分析仪,所得检测器扫描结果的峰值和平均值分别以黄色和蓝色表示。红色限值图象为 5 类峰值和平均值限值(峰值限值通常比平均值限值高出 20dB)。

金属外壳屏蔽

另一种优化高频 EMI 性能的有效方式是添加金属外壳屏蔽层,从而阻挡辐射电场。外壳通常由铝制成,采用框架(敞开式)或封闭式设计实施方案。屏蔽外壳可覆盖除 EMI 滤波器之外的所有功率级元器件,外壳与 PCB 上的 GND 相连,基本形成了一个带有 PCB 接地平面的法拉第笼。

这使得从开关单元到 EMI 滤波器或长输入线连接(也用作天线)的辐射噪声耦合显著减少。当然,这会产生额外的元器件和装配成本,导致散热管理和散热测试的难度增加。铝电解电容的外壳也可以提供电场屏蔽,为实现此目的,可在电路板上针对性地放置该电容。

DC/DC转换器案例研究

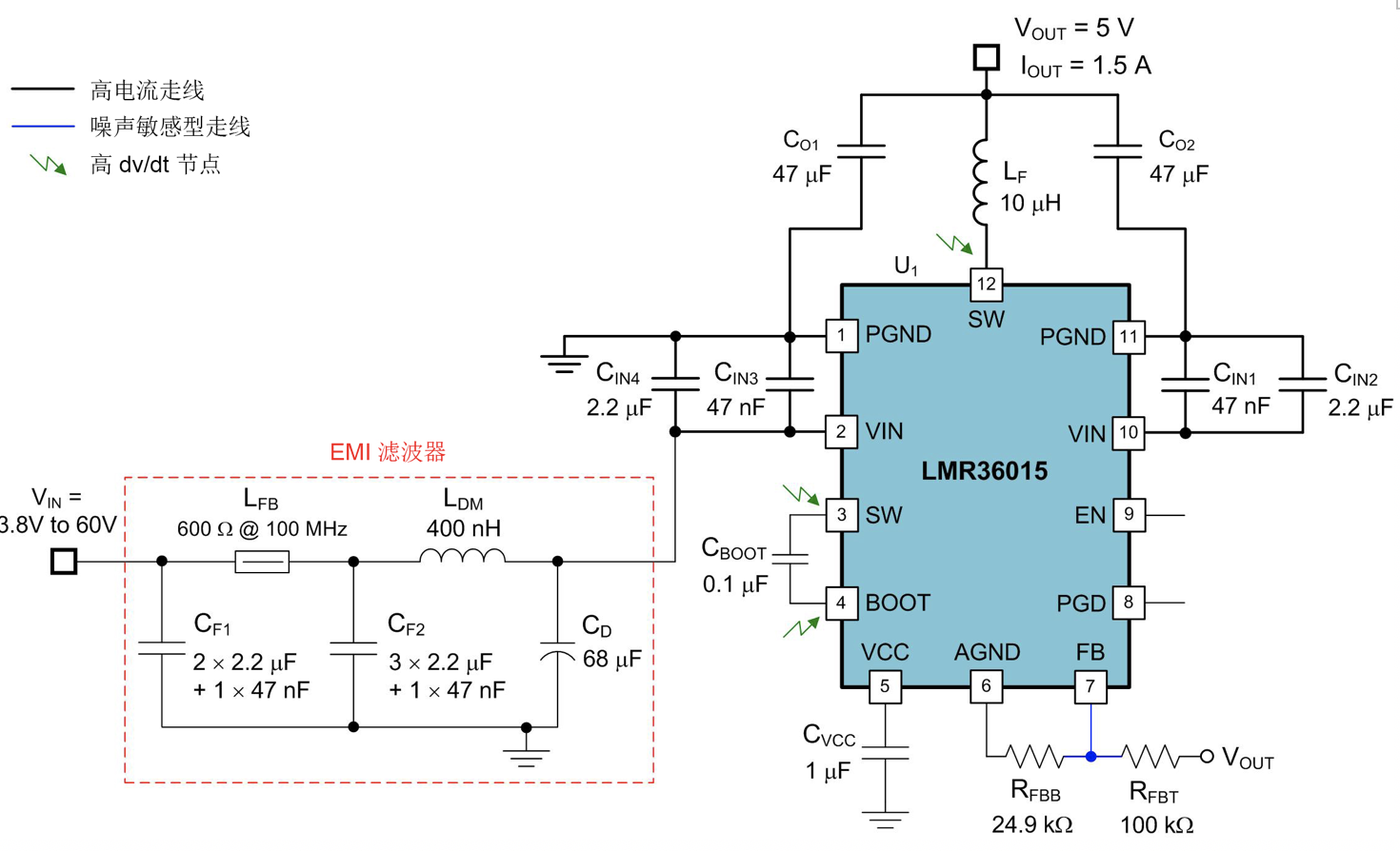

图 6 为 60V、1.5A 单片式集成同步降压转换器电路的原理图,该电路通过多项功能实现最佳 EMI 性能。该原理图还显示了一个两级 EMI 输入滤波器级,旨在满足汽车或噪声敏感型工业应用的 EMI 规范。为了帮助实现最佳的 PCB 布局,原理图中将高电流走线(VIN、PGND、SW 连接)、噪声敏感型网络 (FB) 和高 dv/dt 电路节点(SW、BOOT)突出显示。

图 6:采用 EMI 优化型封装和引脚布局的 DC/DC 转换器。内置一个两级 EMI 输入滤波器

a.引脚布局设计

图 6 所示的转换器 IC 优势在于,其 VIN 和 PGND 采用对称且均衡的引脚排布。该转换器利用两个并联的输入回路使寄生回路电感成功减半。上述回路在 PCB 布局中标记为“IN1”和“IN2”,如图 7 所示。两个外壳尺寸为 0402 或 0603 的小型电容(在图 6 中分别标记为 CIN1 和 CIN3)放置在尽可能靠近 IC 的位置,最大限度减小输入回路面积。两个回路中的环流产生相反的磁矩,消除 H 场并降低有效电感。为了进一步降低寄生电感,PCB 第 2 层(紧靠顶层电源电路的下方)的 IN1 和 IN2 回路下方设有返回电流的连续接地平面,可使场效应自行消除。

在电感两侧各使用一个陶瓷输出电容(COUT1 和 COUT2)同样能够优化输出电流回路。在输出端引出两个并联的接地返回路径可以将返回电流分成两部分,有助于减弱“地弹反射”效应。

图 7:仅部署在 PCB 顶层的功率级布局

SW 引脚位于 IC 中心,因此辐射电场会由 IC 两侧相邻的 VIN 和 PGND 引脚屏蔽。GND 平面覆铜区可对将 IC 的 SW 引脚连接到电感端子的多边形覆层施加屏蔽。SW 和 BOOT 的单层布局意味着 PCB 的底侧不会有 dv/dt 较高的过孔。这样可以避免在 EMI 测试期间,电场与基准接地平面耦合。

b.封装设计

与优化的引脚排布类似,电源转换器 IC 封装设计也是改善 EMI 信号的关键属性。例如,德州仪器 (TI) 的 HotRodÔ 封装技术采用引线框上倒装芯片 (FCOL) 的方式,规避了功率器件线焊导致封装寄生电感过高的情况。如图 8 所示,IC 以上下翻转的形式放置,IC 上的铜柱(也称为凸点或支柱)直接焊接到引线框架。这种构造方法能够提升密度并较薄的外型,因为每个引脚都与引线框架直接相连。从 EMI 角度来看,最重要的一点是,与传统线焊封装相比,HotRod 封装降低了封装的寄生电感。

HotRod 封装不仅可以在开关换向(50MHz 至 200MHz 频率范围)期间减少振铃,还可以降低导通和开关损耗。图 9 所示为开关节点电压振铃随之得到改善的情况。图 8 所示为图 6 中的转换器在 150kHz 至 108MHz 下测得的传导发射。测量结果符合 CISPR 25 5 类要求。

总结

在本文中,我讨论了使用电源转换器 IC 的 DC/DC 稳压器电路可以采用的 EMI 抑制技术。减弱 EMI 的 PCB 布局步骤包括尽量减小布局中的电流“热回路”面积、避免阻断电流路径、采用具有内部接地平面的四层 PCB 结构实现屏蔽(屏蔽效果远超双层 PCB),以及通过尽量减小开关节点覆铜区域面积来降低电场辐射耦合。

转换器封装类型是一项重要的选择标准,新一代器件的开关节点振铃和引脚设计得到显著提升,有助于实现最优的电容放置方案。从输入滤波的角度而言,抑制低频噪声(通常小于 10MHz)相对容易,使用传统的 LC 滤波器级即可实现。然而,抑制高频噪声(10MHz 以上)通常需要额外使用 CM 扼流器和/或铁氧体磁珠滤波器级。焊接到 PCB 接地平面的金属外壳屏蔽层也能有效减轻高频发射。

在本系列文章的下一部分中,我将探讨使用控制器驱动分立式功率 MOSFET 的 DC/DC 稳压器电路适用的 EMI 抑制技术。根据 EMI 进行分析,这些技术更具挑战性。

审核编辑:何安

-

电源管理

+关注

关注

117文章

8664浏览量

148270

发布评论请先 登录

抑制电磁干扰 (EMI) 的实用电路技术

抑制电磁干扰 (EMI) 的实用电路技术

评论