也许你也会跟我一样认为典型数据表中的某些规格难以理解,这是因为其中涵盖了一些你不太熟悉的隐含惯例。对许多RF系统工程师而言,其中一种规格便是锁相环(PLL)中的相位噪声。当信号源被用作本机振荡器(LO)或高速时钟时,相位噪声性能对满足系统要求起到了重要作用。最初从数据表中推断出该规格时似乎就像一个独立的项目。下面我来讲解一下如何通过读取PLL的相位噪声规格来对您的无线电或高速应用可达到的性能进行初步评估。

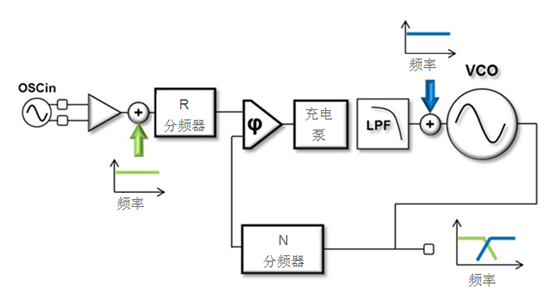

注意,PLL是一种控制回路,这种系统具备频率响应功能。参考路径中生成的噪声受控于回路中对系统输出的低通频率响应,而压控振荡器(VCO)中生成的噪声受控于回路中对系统输出的高通频率响应。参见图1。

图1:锁相环中的两个已建模的噪声源(绿色和蓝色)及其对系统输出的频率响应

环路带宽内部(低通频率响应)PLL产生的噪声分为两个部分——闪烁噪声和白噪声,但环路带宽外部(高通频率响应)的噪声在数据表中通常表示为开环VCO性能。

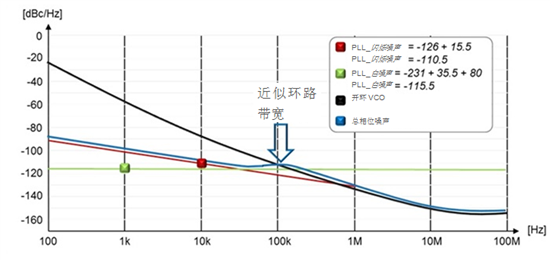

当这些规格被插入动态环路中时,就会对总相位噪声造成影响。图2解释了这三种噪声规格是如何定义一个近似选中环路带宽的总相位噪声的方法。请注意环路带宽上方总相位噪声与VCO的跟踪调谐以及环路带宽下方总相位噪声与PLL的跟踪调谐。

图2:LMX2592预估相位噪声曲线图(带100-MHz相位检测器频率的6-GHz输出),借助(1)闪烁噪声、(2)白噪声和(3)~100-kHz环路带宽用VCO开环数据

让我们简单回顾一下这三种规格:

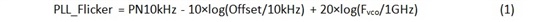

1)闪烁噪声(图2中的红线)是锁相环的一种特性,会在偏移较低时影响相位噪声。这种噪声会随着偏移频率的变化而变化,变化率为每10年10分贝。德州仪器对该噪声进行了规定并将其标准化,使其适用于10-kHz偏移时的1-GHz载波。方程1解除了闪烁噪声规范化:

其中,Fvco指VCO的频率。

闪烁噪声一般不受相位检测器频率的影响,只取决于输出载波频率。因此,输出频率增加一倍,噪声将增加6分贝。

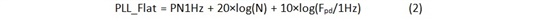

2)白噪声(图2中的绿线)亦称为锁相环的品质因数,为方便对比,对该噪声标准化。与在1 Hz载波时的1-Hz带宽[dBc/Hz]中的输出信号相比,品质因数的单位是分贝。

其中,N指反馈(参见图1)的分频器,Fpd指相位检测器的运行频率。

该规格会影响中段偏移频率的相位噪声。从方程2中可以看出,相位检测器频率越高,环路内部的相位噪声越佳,相位检测器频率每增加一倍,相位噪声会改善3分贝。

3)开环VCO相位噪声(图2中的黑线)与偏移频率之间的关系是每十年变化20分贝,但是距离载波更近时,会变为每十年变化30分贝。白噪声一般通过15或20-MHz的偏移频率传递,被称为噪声源的本底噪声。锁相环中VCO发出的噪声会进入高通频率响应。最后,相位噪声通常会随着输出频率的变化而变化,因此当频率减半时,相位噪声会改善6分贝。

现在,您可得出不同偏移频率和输出频率时PLL的近似相位噪声。您需要从数据表中获得闪烁噪声、白噪声和开环VCO相位噪声。然后利用公式1和公式2解除这些规格的标准化,然后假设尖锐环路滤波器为第一个近似值(如图2中所示),即可得出闭环响应的近似值。

估算PLL相位噪声起初看似很困难,但推断数据表中所需的规格并使用此处概括的公式将有助于选择出满足您系统要求的最佳PLL。通过准确的模拟,德州仪器可以提供两种计算PLL的相位噪声的工具:WEBENCH® Clock Architect和PLLatinum™ Sim。您可以了解LMX2592和德州仪器的其他RF PLL及合成器,也可以在本页查看以上工具。

原文链接:

https://e2e.ti.com/blogs_/b/analogwire/archive/2016/03/02/understanding-datasheet-phase-noise-specifications-of-a-phase-locked-loop

编辑:jq

-

振荡器

+关注

关注

28文章

3857浏览量

139454 -

分频器

+关注

关注

43文章

448浏览量

50109 -

pll

+关注

关注

6文章

781浏览量

135364 -

VCO

+关注

关注

13文章

190浏览量

69391 -

相位噪声

+关注

关注

2文章

181浏览量

22959

发布评论请先 登录

相关推荐

锁相环PLL的噪声分析与优化 锁相环PLL与相位噪声的关系

opa1622 TINA仿真模型相位结果与数据表中不符是怎么回事?

LMK04816具有双环PLL的三输入低噪声时钟抖动消除器数据表

PLL1705/PLL1706双通道PLL多时钟发生器数据表

LMK04208具有双环PLL的低噪声时钟抖动消除器数据表

PLL1707/PLL1708 3.3V双通道PLL多时钟发生器数据表

带双环路PLL且符合JESD204B标准的LMK04832超低噪声时钟抖动清除器数据表

具有双环路PLL的LMK04228超低噪声且符合JESD204B标准的时钟抖动清除器数据表

CDCM7005-SP高性能、低相位噪声和低偏斜时钟同步器数据表

如何根据基本的数据表规格估算出PLL的相位噪声

如何根据基本的数据表规格估算出PLL的相位噪声

评论