简介

数据采集系统的设计人员—特别是需要在过程控制或自动化系统中进行精密测量的设计人员—已经习惯地将他们的系统设计为在第一那奎斯特区域内运行,这只意味着最大输入频率必须被限制在少于一半采样频率的范围内。所以,如果你搭建了一个系统,用于捕捉最大频率为20KHz的音频,那么你必须在40KHz频率以上进行采样,以确保捕获到最高频分量。

混叠

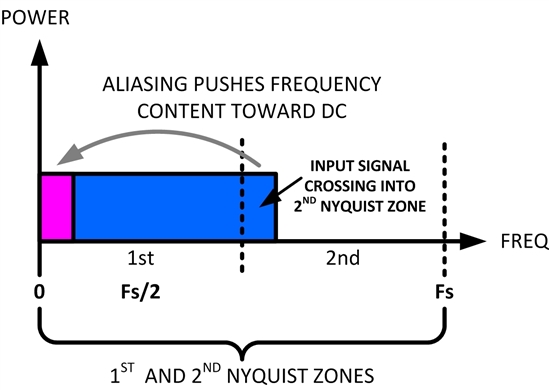

那么,当你不遵循这个规则时,系统会发生什么情况呢?我们假定,你在15kHz上对模拟信号进行采样,此时的频率分量高达20kHz—你将最终遇到“混叠”问题,或者将上部分量折叠进入输入信号的工作频段(请见图1)。这些混叠信号将增加到原始信号上,并且将无法把已混叠频率分量与原始信号区分开来。

图1:输入信号与第二那奎斯特区域产生交叉,并被混叠进入信号的工作频段

在大多数情况下,捕捉模拟信号,并且不遵守那奎斯特采样规则的系统被认为是“不良系统”,并且需要在模数转换器 (ADC) 的输入前放置一个抗混叠滤波器,以防止频率分量交叉进入上部那奎斯特区域。然而,有时候这是一个好事情。

在运行于超高频模式下的射频 (RF) 系统中,处理器(或者一个现场可编程门阵列 [FPGA])与数据转换器之间移动的数据量会是十分可观的—特别是在系统运行在第一那奎斯特区域内更是如此(或者只简单称为“第一那奎斯特”)。例如,运行在第一那奎斯特区域内,输出频率为1GHz的数模转换器 (DAC),为了实现所需的频率内容,它需要将输出设定在2GHz以上。

这对于ADC也用样适用—如果RF子系统的输入的工作频段在900MHz与1GHz之间,那么ADC必须在2GHz以上采样,以便将所有的频率内容置于第一那奎斯特区域内。

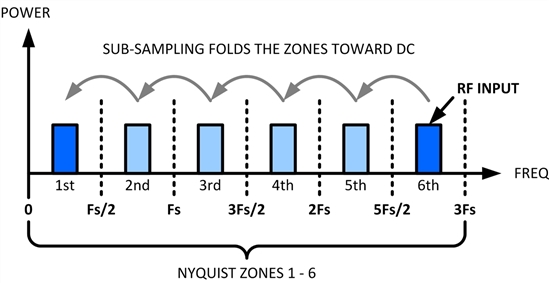

将那奎斯特混叠变为优势

技巧在于将混叠(或者称为频率折叠)为你所用。通过对数据转换器进行欠采样,更高频率内容将混叠进入所有的较低那奎斯特区域(请见图2)。你需要绝对确保没有任何内容在较低频段内终止—较低区域内的任何噪声或频率分量也将被混叠进入第一那奎斯特区域。好消息是,如果这是一个第一那奎斯特系统,那么数据转换器的数据速率只是所需RF输入采样率的几分之一。欠采样极大地减少了被提供给数字信号处理器 (DSP) 或FPGA的采样数据速率。

图2:欠采样时,较高阶频率分量被折叠进入较低那奎斯特区域

ADC唯一一个主要要求就是输入带宽对于输入频率来说必须是充足的,否则的话,信号将失真。例如,ADC12J2700可以采样高达2.7GSPS,但是它具有一个大于3GHz的输入带宽,从而使得输入信号超出最大采样率,因此将它们折叠进入较低区域。还有一些其它注意事项已经超出了本篇博文的范围,不过,总的说来,这个技巧使你不用对付极高数据速率,以及处理要求。

如果你正在设计一个高性能数字RF系统,你也许想使用这个方法,连同合适的DAC或ADC来开展设计工作。在设计正确时,这个方法可以极大地简化这些系统的处理和数据流要求。

其它资源

- 阅读模拟接线 (Analog Wires) 博文,“ADC中的混叠:并不是所有的信号都与它们看起来一样。”

- 在这篇博文中进一步了解RF采样,以及混叠如何成为你的好朋友。

- 在我们的数据转换器学习中内寻找超过100个数据转换器技术资源。

- 阅读TI的白皮书,“为什么在欠采样够用的时候使用过采样?”

- 进一步了解ADC12J2700。

审核编辑:符乾江

-

数据采集

+关注

关注

39文章

6437浏览量

114459 -

模拟信号

+关注

关注

8文章

1151浏览量

52826

发布评论请先 登录

相关推荐

使用50偶输出阻抗的波形发生器产生一个80Mhz的正弦信号,ADS5474采样的数值就出现了饱和削顶的现象,为什么?

AD5474如何配成50欧呢?

为什么DAC5674在external 2×的情况下datarange在直流到200HZ之间?

DAC的高次谐波为什么都会折叠回第一奈奎斯特区间?

ADS1256转换后的数据规律失真的原因?怎么解决?

路特斯发布“路遥”超级混电技术,续航超1100公里

采样频率和信号频率之间的关系

使用单通道ADC+模拟开关结构采样多路信号时,ADC采样率如何选择呢?

求助,关于OPA2828设计抗混叠滤波器的疑惑求解

DAC39RF10、DAC39RFS10 10.24、20.48GSPS 16位双通道和单通道多奈奎斯特数模转换器(DAC)数据表

超越第一奈奎斯特区域,将那奎斯特混叠变为优势

超越第一奈奎斯特区域,将那奎斯特混叠变为优势

评论