在当今世界,互联网数据流量不断上升,移动设备的使用也呈爆炸式的增长,对于处理快速增长的数据和视频数据流量的电信基础设施的需求变得越来与具有挑战性。根据思科可视网络互联指数全球IP流量预测,2014-2019,到2018年,全球将有40亿互联网用户(超过世界人口的51%),以及210亿个联网设备和连接数量。

25千兆以太网 (25GbE) 正在快速发展,并且很多分析人士预计它将在未来4年中呈现指数性的迅速增长。想象一下设计有线网络设备来支持过多标准,以及用最小数据包损失和延迟来快速提升数据速率时的复杂程度!

随着数据速率的增加,链路抖动允许量变得越来越严格。硬件工程师将主要精力放在如何使他们的整个线路卡能够支持最大吞吐量,而为基准时钟产生的随机抖动分配尽可能小的允许量。针对基准时钟,对于一条25GbE的链路(集成范围在12kHz至20MHz之间)来说,可以实现的最大可能均方根 (RMS) 抖动的范围在100fs至300fs之间。

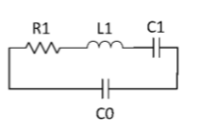

这个12kHz-20MHz的标准相位噪声集成范围包括锁相环 (PLL) 频带内和频带外 (VCO) 噪声的影响。基准时钟发生器的相位噪声性能需要在PLL环路带宽内和带宽外都表现得很出色,以符合更加严格的抖动技术规格要求。

例如,LMK03328在多个集成带宽内提供业内最低相位噪底,一致的RMS抖动。超低相位噪声和抖动转化为串行链路内更好地比特误差率 (BER)。考虑一下对传统高端基于表面声波的示波器的改进。图1显示的是,在一条具有156.25MHz基准时钟的10G链路上,相对于一个SAW示波器,在使用LMK03328时,BER性能提高了3倍。随着进一步的优化,你可以实现更高的性能—最多比传统SAW示波器高9倍。

一个低相位噪声基准时钟转化为串行链路中其它关键块的更高抖动允许量分配。随着数据速率快速爬升到25GbE,并且允许的BER在1e-18时变为标准值,高质量、低抖动基准时钟在保护信号完整性方面的重要性变得不可小觑。

在用一个眼图来解决链路无法正常运行的问题后,你现在需要确保你的设计是稳健耐用的,并且在应力下可以正常运行。使信号完整性变得更加糟糕的常见问题就是电源抖动。将低压降稳压器 (LDO) 集成在内可以极大地帮助克服对电源噪声的敏感度。

具有内置LDO的时钟发生器通过提供稳健耐用的电源噪声抑制和出色的电源抑制比 (PSRR) 来帮助改进无错数据传输。图2显示的是使用LMK03328时对PSRR和TX眼图性能的改进,其原因就在于LMK03328集成了一个LDO。

编辑:jq

-

ldo

+关注

关注

35文章

2193浏览量

154794 -

模拟

+关注

关注

7文章

1432浏览量

84139 -

串行

+关注

关注

0文章

237浏览量

34127 -

时钟发生器

+关注

关注

1文章

204浏览量

67730 -

SAW

+关注

关注

11文章

148浏览量

27461

发布评论请先 登录

相关推荐

时钟发生器的特点和应用

高性能抖动衰减器和时钟发生器的推荐晶体、TCXO和OCXO参考手册(之一)

CDCE421A全集成、宽范围、低抖动晶体振荡器时钟发生器数据表

CDCM61004四路输出、集成VCO、低抖动时钟发生器数据表

CDCM61002两路输出、集成VCO、低抖动时钟发生器数据表

CDCI6214超低功耗时钟发生器(具有PCIe支持、四路可编程输出和EEPROM)数据表

具有两个独立PLL、八路输出、集成EEPROM的LMK03328超低抖动时钟发生器数据表

具有14个可编程输出的LMK03806超低抖动时钟发生器数据表

CDCM6208V2G具有小数分频器的2:8时钟发生器/抖动消除器数据表

超低抖动时钟发生器怎么去优化串行链路系统性能

超低抖动时钟发生器怎么去优化串行链路系统性能

评论