作者:Martin Rowe — 2012 年 2 月 6 日

在本系列第 1 部分《电路测试主要运算放大器参数》一文中,我们介绍了一些基本运算放大器测试,例如失调电压 (VOS)、共模抑制比 (CMRR)、电源抑制比 (PSSR) 和放大器开环增益 (Aol)。本文我们将探讨输入偏置电流的两种测试方法。选择哪种方法要取决于偏置电流的量级。我们将介绍器件测试过程中需要考虑的各种误差源。本系列的下篇文章将介绍一款可配置测试电路,其可帮助您完成本文所介绍的所有测量。

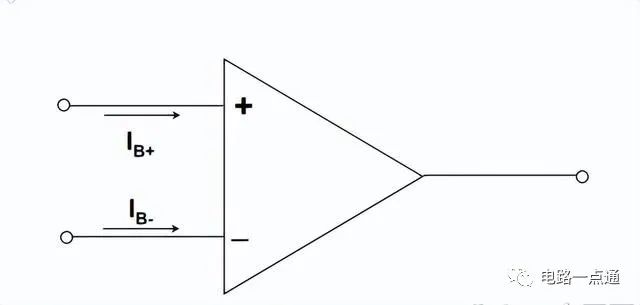

产品说明书通常为运算放大器的非反相输入与反相输入(iB+ 和 iB-)分别提供了一个偏置电流列表。这两个输入的区别就是输入失调电流 IOS。在工作台上,您可能会忍不住使用图 1a 中的电路来测试正输入偏置电流,因为该配置下的放大器很稳定,这种方式有效。

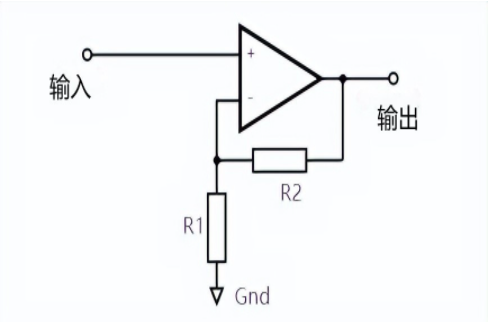

图 1.使用图 (a) 中的电路测量运算放大器非反相输入端的输入偏置电流。在图 (b) 中增加一个环路放大器,可在针对反相输入端进行测量时保持运算放大器的稳定性。图 (c) 中的电路可测量任何输入端的偏置电流。继电器可决定电路配置。

可惜,在测量负输入偏置电流时,没有保持放大器稳定性的简单方法。然而,可增加一个环路放大器保持被测试器件的稳定性,这样可使用静电计测量偏置电流,如图 1b 中的电路所示。这个电路就是在第 1 部分中我们用来测试 VOS 的双放大器测试环路,但有一个不同的连接。

我们将两个放大器的输入颠倒过来,以保持被测试器件的稳定性。虽然这种方法对工作台测试很管用,但静电计的速度太慢,不适合用于高速生产测试。我们在生产测试中使用的方法是 VOS 测试的修改方案。为了测试输入偏置电流 (IB),我们为电路添加了继电器和电阻器(或电容器)。请见图 1c 中的电阻器 RB。

为了讨论起见,我们使用双运算放大器测试环路来描述该测试。不过,本技术同样也适合第 1 部分中介绍的两种测试环路。我们为图 1c 中被测试器件的每个输入都添加了一个继电器和电阻器。

在继电器 K2 和 K3 闭合时,我们可使用第 1 部分介绍的 VOS 测量技术测量和保存 VOUT 值。公式 1 根据 RIN、RF 和 VOS 定义了 VOUT。

公式 1

对公式 1 进行变换后,可得到用于计算 VOS 的公式 2。

公式 2

接下来,我们打开 K2,进行另一项测量,得到 VOUT(IB-)。测得的电压由被测试器件的失调电压以及流过电阻器 RB 的输入偏置电流引起,可表示为公式 3。

公式 3

我们现在可求解 iB-,等式两边同时除以 (RIN+RF)/RIN,得到公式 4。

公式 4

公式 5

然后,在公式 4 两边同时减去被测试器件的失调电压,得到公式 5。

最后,在公式 5 两边同时除以 RB,计算 IB- 的值。

图 2.在测量小于几百微微安的偏置电流时,应在电路中使用电容器,并使用万用表测量一系列样片。

可使用类似的方法测量 IB+。测量 IB- 时,关闭 K3,打开 K2。测量 IB+ 时,关闭 K2,打开 K3。由于我们已经测量出运算放大器的 VOS,因此接下来就只是数学计算了。结果很容易得出,而且只需一个良好的数字万用表 (DMM) 即可。

注意,使用电阻器产生电压差来测量 IB,只对低至几百微微安的偏置电流有效。我们可针对更低的偏置电流使用另一项测量技术。

对于小于几百微微安的 IB 值,我们使用电容器来替换 RB 电阻器。一旦短路继电器被打开,偏置电流就会使环路以 IC = C(dV/dt) * 环路增益的速度结合。您可通过在已知时间间隔内进行测量来计算偏置电流。这种方法可测量小于 1pA 的偏置电流。

PCB 布局对于这些真正的低 IB 电流来说非常重要。要注意减少杂散电容,因为杂散电容可能会消耗一些 IB 电流。PCB 上被测试器件输入引脚的泄漏也会导致误差,因此应在输入引脚周围创建保护环,并将保护环连接至接地。这将减少来自高电压节点的任何泄漏。从拓扑角度来看,应该采用温度稳定的低泄漏电容器替换图 1c 中的 RB 电阻器。

采用电容方法需要良好的时钟。这是因为输入偏置电流测量不仅需要打开各种电容器(连接在被测试器件的输入端)间的继电器,而且还要测量已知间隔的电压变化。我们可通过在精确确定的时间周期内测得的环路输出电压变化来计算输入偏置电流。

当电容器的继电器在 t0 位置打开,输出便开始根据偏置电流的极性以正方向或负方向结合(图 2)。编程的延迟可让电路稳定下来。然后,在 t1 位置,DMM 按已知的采样率进行采样。接下来在 t2 位置,会有另一个延迟。最后,在 t3 位置,DMM 会提取更多样片。

保持采样测量时间不变,这样就能知道 dt 的值。获得第二组样片测量的平均值,并减去第一组样片测量平均值,便可得到 dV 值或者 dt 时间内的电压变化。我们可通过电容器来计算电流,如:

方程式 7

方程式 8

然后,通过以下方程式计算偏置电流:

典型的误差源

如果不讨论测量过程中会遇到的误差源,那么对 VOS 测量的讨论就不完整。明显的误差是那些由 DMM 分辨率以及所选组件(尤其是电阻器)值(噪声和容差)引起的误差。更细微的误差可分为以下三个类型:

A. 热生成电动势 (emf),由继电器接触引起

焊接点

板间引脚连接

自动测试处理器的接触点与插槽

B.下列因素产生的漏电流:

电源

继电器控制和电源线迹

PCB 材料的属性

C. 噪声

环境

测试仪

组件

被测试器件本身

这里讨论的所有被测试器件配置中的典型误差源均为热生成电动势和漏电流。漏电流主要影响偏置电流测量,而热生成电动势则可影响所有低级失调电压测量。最大程度减少这些影响是确保系统功能和测量准确度的必要条件。

漏电流由表面污染以及经过组件或在 PCB 材料中的电阻式路径导致。表面污染通常可通过彻底清洁电路板来控制,但湿度可能会改变表面漏电流。其它电阻式路径可由材料的隔离电阻设置。在电阻式路径连接电源线或继电器控制型电源线时,也可能会出现漏电流。使用保护环以及支持高电平有效驱动器的闭锁继电器,可缓解一部分这类漏电路径影响。

热电动势可在继电器接触、焊点、板间引脚连接点以及其它所有测试处理器接触点和插槽中产生。例如,考虑图 1c 中的双放大器 VOS 测量电路。漏电流不会明显影响该测量。但该电路无法体现多种热电动势来源。

图 3 是热电动势误差源,标记为 VT。在室温下测量时,梯度渐变无异常。但在寒冷或炎热的环境下进行测试时,从被测试器件到电阻器和继电器的热梯度渐变会很明显。

本系列的第 3 部分将讨论测试板的设计注意事项。

其它文献

Dostal, Jiri,《热电电压》,摘自运算放大器第 2 版第 9.3.1 节。Butterworth-Heinermann,1993 年第 266 页。

David R. Baum 是德州仪器 (TI) 的一名模拟 IC 设计工程师,负责开发用于 LCD 和 AMOLED 电视的产品设计。David 拥有超过 27 年的丰富模拟设计经验和至少 7 项专利。他毕业于位于亚利桑那州图森市的亚利桑那大学,以优异的成绩获得电子工程学士学位、MBA 以及德国文学硕士学位。邮件地址:ti_davidbaum@list.ti.com。

Daryl Hiser 是 TI 高精度运算放大器产品部的高级测试工程师,负责制定和执行新产品的测试与特性描述方案,拥有两项专利。他毕业于位于亚利桑那州 Flagstaff 市的北亚利桑那大学,获动物学理学学士学位。邮件地址:ti_darylhiser@list.ti.com。

原文链接:

http://www.edn.com/electronics-news/4389470/The-basics-of-testing-op-amps-part-2-br--Test-op-amps-for-input-bias-current

编辑:jq

-

pcb

+关注

关注

4319文章

23084浏览量

397630 -

电流

+关注

关注

40文章

6852浏览量

132138 -

运算放大器

+关注

关注

215文章

4933浏览量

172871 -

VOS

+关注

关注

0文章

22浏览量

8099

发布评论请先 登录

相关推荐

运算放大器测试基础第2部分:测试运算放大器的输入偏置电流

运算放大器测试基础第2部分:测试运算放大器的输入偏置电流

评论