如果您在通信行业工作,那么您可能很熟悉抖动对系统性能的影响。抖动不仅会降低数据转换器的性能,而且还可在高速数字系统中产生误码。凭直觉判断,给时钟增加噪声会增大系统其它部分的噪声。因此我总是试图通过选择可带来最小附加抖动的组件来最大限度地降低总体抖动。顾名思义,附加抖动就是由位于时钟源(例如合成器或振荡器)与被计时器件之间的组件所增加的噪声。该附加噪声可增大时钟的不确定性,导致抖动增加。

在实际系统中,一个时钟源要驱动多个器件,因此可使用时钟缓冲器(通常称为扇出缓冲器)来复制信号源,提供更高的激励电平。

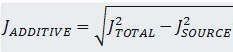

LMK00304 扇出缓冲器就是一个很好的例子。时钟缓冲器产生的附加抖动主要影响时钟的宽频带噪声。它可使用图 2 中所示的方根公式进行计算。

附加抖动的计算方法是:使用信号源 (J1) 测量出总体综合抖动,然后加入缓冲器并在输出端进行相同的测量。不过要小心一点,……如果您使用传统信号发生器,那么时钟的噪声等级可能会误导您,让您以为所产生的附加噪声微不足道。

良好的测量技术可确保测量所使用信号源的噪声远远小于被测量器件。例如,使用一个由 Agilent E5052 信号源分析器和 Wenzel 100 MHz 振荡器(具有信号调节)组成的测试装置,我们将测量到大约 46fs 的综合抖动。而在时钟后面布置一个缓冲器并进行相同的测量,则可得到大约 102fs 的总体综合抖动。使用以下公式计算附加抖动:

我们的测试装置得到了大约 91fs 的附加抖动。如果我们将时钟源改为高质量信号发生器等可能将要装在您工作台上的组件,信号源抖动将升高至 150fs 左右。这就越来越有意思了,……而且也不那么显眼。如果现在我们将相同的缓冲器放在该噪声源的后面并再次测量总体综合抖动,得到的结果将大体相同,会让我们认为附加抖动可以忽略。

因此,您在比较不同厂商时钟缓冲器的产品说明书时,务必要查看参数说明(或者给应用工程师打个电话),了解抖动如何测量。如果时钟源的噪声相对于被测量器件而言比较高,那么抖动数字可能会有误导性。您在自己进行测量时也要牢记这一点,否则您可能会发现寻找附加抖动的地方完全不对!

责任编辑:haq

-

时钟缓冲器

+关注

关注

2文章

274浏览量

51982 -

模拟

+关注

关注

7文章

1447浏览量

85551 -

测量

+关注

关注

10文章

5763浏览量

117070

发布评论请先 登录

利用输出放电解决电源的系统性故障

深度剖析LMK0480x:低噪声时钟抖动清除器的卓越性能与应用实践

深入剖析 LMK04100 系列时钟抖动清理器:性能、应用与设计要点

LMK0482x系列时钟抖动清除器:高性能时钟解决方案解析

LMK61XX高性能超低抖动振荡器:设计与应用指南

LMK61XX高性能超低抖动振荡器:设计与应用指南

LMK60XX高性能低抖动振荡器:特性、应用与设计指南

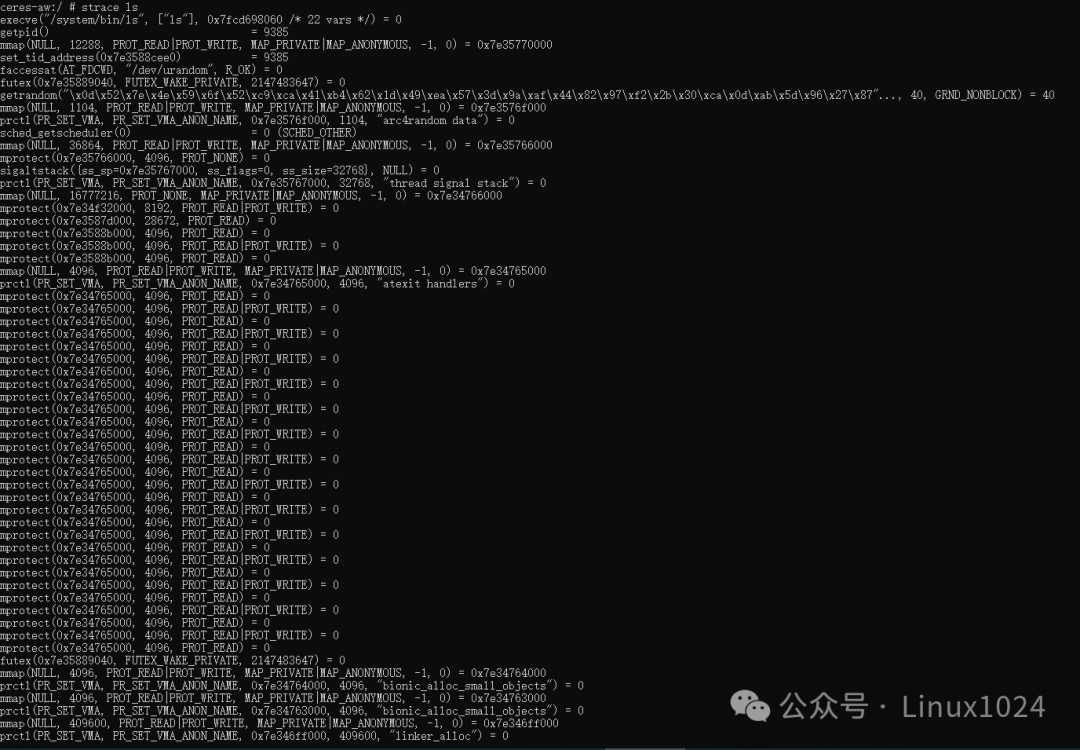

Linux系统性能调试工具—strace

Linux系统性能优化与调试的思路

深度解读Linux系统性能瓶颈定位策略

Linux系统性能优化技巧

Linux系统性能指南

抖动对系统性能的影响

抖动对系统性能的影响

评论