作者:Michael Peffers

欢迎继续阅读《模拟线路》上的《获得连接》系列博客!在上篇《获得连接》博客《串行解串器 XAUI 至 SFI 设计》一文中,我们深入了解了在 XAUI 至 SFI 协议转换器设计中使用 TLK10232 的方法。本文我们将回过头来了解如何在 LVPECL、VML、CML、LVDS 和子 LVDS 接口之间转换。

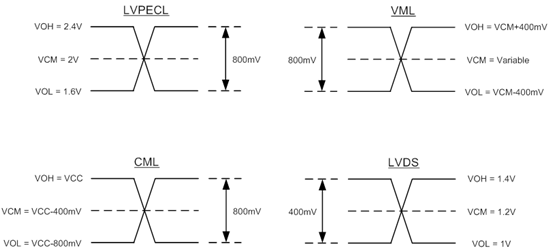

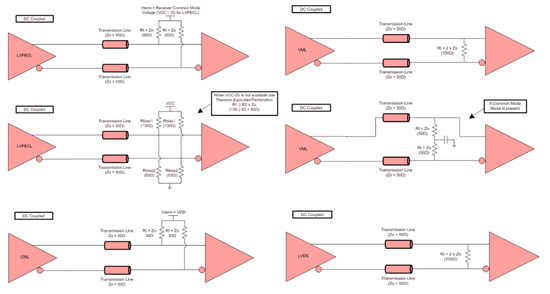

系统当前包含 CML 与 LVDS 等各种接口标准。理解如何正确耦合和端接串行数据通道或时钟通道的传输线路是一项非常重要的技能。我们先来了解一下大多数通用接口的电压等级及所需的端接技术:

图 1:通用接口电压等级

图 2:通用端口端接

接口之间的电压等级不同,而且各种接口需要不同的端接,因而接口之间并不兼容。不过没关系,现在已经有了解决该问题的方案。

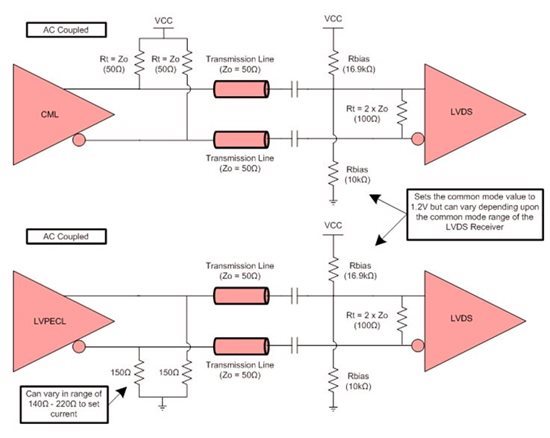

要成功连接两个不同的接口,必须在两个接口之间布置各种 AC 耦合电容器。这些 AC 耦合电容器不仅可除去传输信号中的 DC 分量,而且还允许设置新的 DC 偏置或共模电压。我一般尽可能将 AC 耦合电容器和端接网络布置在靠近接收器的位置,以便帮助我避免任何传输线路影响。不过,如果在您设计的系统中无法对接收器进行控制,那么也可将 AC 耦合与端接设置在发送器附近。

在选择 AC 耦合电容器值时应注意,在比特周期结束前电容器不能完全充满。典型的 AC 耦合电容器值在 0.1uF 至 0.01uF 之间,在有问题时,可计算出 RC 的时间常数 T,并根据比特时间进行检查。在进行 AC 耦合时,还必须具有 DC 平衡数据模式,因为连续不断 1 和 0 的长期运行会导致电容器饱和或完全放电,从而在比特转换过程中产生比特错误。

在下图 3 中,我举了两个实例,用以说明如何在 CML 驱动器、LVPECL 驱动器和 LVDS 接收器之间实施 AC 耦合。

图 3:不同接口的互连

连接任意两个不同接口时可使用这种相同的方法,只要正确端接驱动器和接收器,就可使用 AC 耦合电容器。

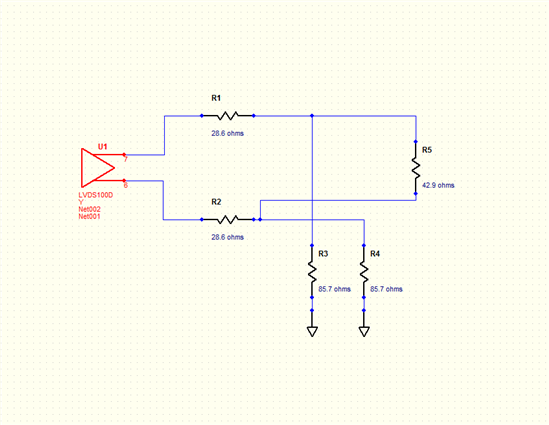

我常听到的一个问题是,“我可不可以通过转换标准 LVDS 驱动器的输出来支持子 LVDS 接收器?”该问题的答案是“可以”,我将使用 SN65LVDS100 的 IBIS 以及 Hyperlynx 来介绍实施方法:

图 4:LVDS 至子 LVDS 的端接方案

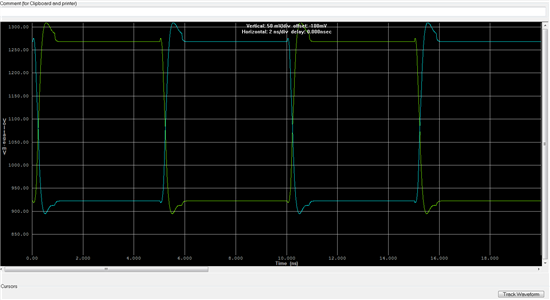

图 5:传输的 LVDS 波形

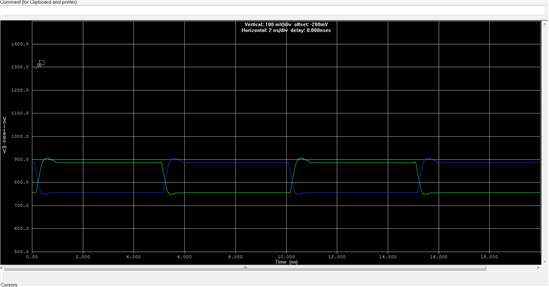

图 6:在端接后接收到的子 LVDS 波形

在这个最后的实例中,我们并非一定要使用 AC 耦合电容器才能复位共模电压,因为 R1 与 R3 以及 R2 与 R4 的比值可以设定适用于共模信号的衰减量。不过如果子 LVDS 接收器需要,在这一点上 AC 耦合仍然是一个选项。

-

转换器

+关注

关注

27文章

8783浏览量

148845 -

数据

+关注

关注

8文章

7223浏览量

90168 -

解串器

+关注

关注

1文章

107浏览量

13504

发布评论请先 登录

相关推荐

【proteus练一练】串行数据转换为并行数据

LVPECL、VML、CML、LVDS 与LVDS之间的接口连接转换

4个高速串行通道的AHCC2001PCI/CPCI

Sync_Header Bits如何从串行数据中获取正确的Header Bits?

如何在LVPECL、VML、CML、LVDS和子LVDS接口之间转换

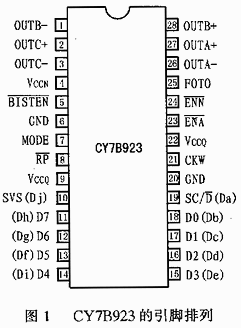

高速串行数据通信发送芯片CY7B923的原理及应用

MATLAB环境下的串行数据通信系统设计

基于Matlab环境的串行数据通信

高速串行数据通信CY7B923芯片的性能特点及设计实例

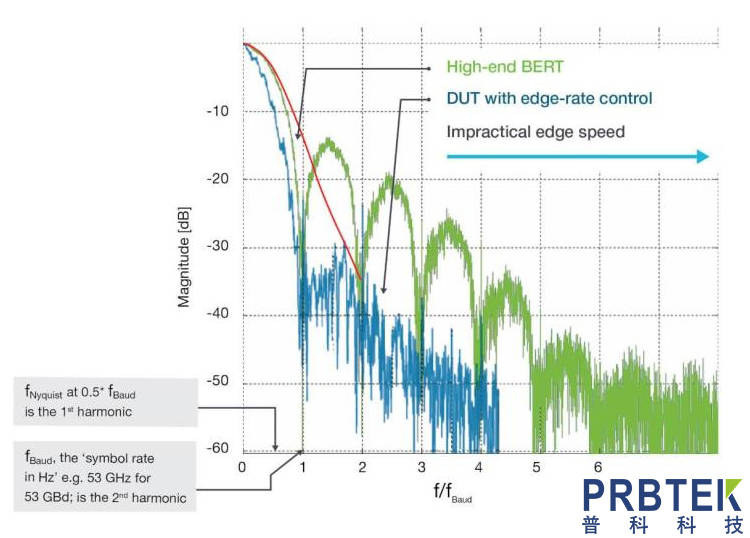

测量串行数据信号:选择合适的示波器带宽

如何正确耦合和端接串行数据通道

如何正确耦合和端接串行数据通道

评论