作者:Collin Wells 德州仪器

最近在做一个项目时,我不得不对几组电子电线进行重新布线,让它们远离越野车的发电机,因为电容耦合产生的噪声可从发电机进入电线。这个项目让我想起了在通过电线、带状线缆或板对板连接器路由相互之间相邻信号时所遇到的类似情况。

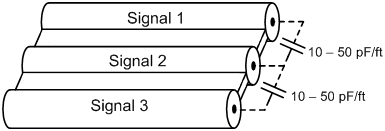

正如采用绝缘体隔离的任何其它导体一样,任何相邻布线的两条电线都会在其之间产生电容。根据所用的线规和绝缘体材料,大部分标准带状线缆及电线会在电线之间产生 10 至 50 pF/ft 的电容,如下图 1 所示。

图 1. 带状线缆中相邻电线间的电容

由于信号会相互干扰,两条信号线之间的电容会引起信号延迟、噪声耦合或瞬态电压。

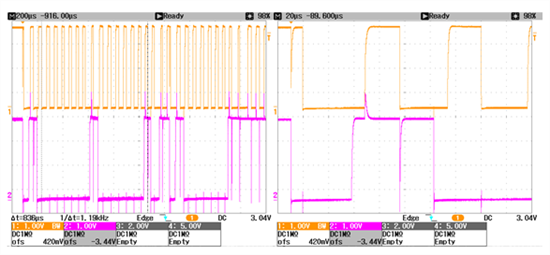

图 2 是电缆电容在通用双线开漏通信总线中引起大量瞬态电压的实例。右图是“开始”命令与左图前几个时钟脉冲的放大图。

图 2. 带状线缆的电容耦合

使用三英尺长的线缆路由两个相邻通信信号时,会出现图 2 中的结果。这会导致两个信号间的电容超过 50pF。

由于该电容的存在,在一个信号产生变化时,可导致另一个信号产生电压瞬变。其产生的原因是,当一个信号电平发生变化时线缆电容需要瞬态电流在信号间流动。

静态信号上出现的瞬态电压强度取决于线缆电感以及信号驱动器提供所需瞬态电流的能力。在这种情况下,由于耦合引起的瞬态电压非常高,超过了可导致数据损坏的逻辑电平阀值,因此通信无法成功进行。

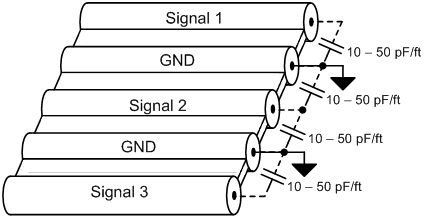

在信号间安放一根或多根 GND 线,会减少其间的电容,如图 3 所示。这种方法可降低信号间的电容,但同时会导致来自每个信号的 GND 电容。GND 电容会引起信号延迟与数字边界环绕,但只要影响不太严重,通常不会导致通信故障。

图 3. 采用 GND 分离信号

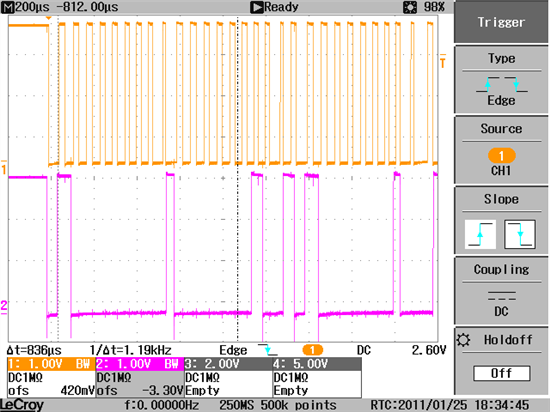

图 4 显示了在我对其进行修改 — 在信号线之间添加两个 GND 信号后的通信信号效果。改动后信号间电容降至约 10pF。这样,瞬态电压得到了显著降低,通信获得了成功。

图 4. 通过降低电容实现成功的通信

总之,在设计线缆、电线以及 PCB 路由设计方案时要注意杂散电容耦合的影响。在需要较长线缆的应用中,应选择电容较低的线缆,并通常需要在两个可能相互耦合的信号间加入一个或多个 ac GND 信号。

如果您希望更深入地了解该主题,敬请查看下列更多参考信息:

《线缆选择实用指南》应用手册;

《LVDS:带状线缆连接》《模拟应用期刊》文章;

《使用不同线缆时的 LVDS 性能》应用报告;

《高速差分连接建议》应用报告;

《支持更低 EMI 的 PCB 设计指南》应用报告。

阅读原文, 请参见: http://e2e.ti.com/blogs_/b/precisiondesignshub/archive/2013/12/12/how-to-minimize-crosstalk-in-cable-designs.aspx

编辑:jq

-

电容

+关注

关注

100文章

6051浏览量

150464 -

电缆

+关注

关注

18文章

2726浏览量

54856 -

发电机

+关注

关注

26文章

1645浏览量

67700

发布评论请先 登录

相关推荐

TAS5630如何才能最大限度地减少电压失调,或者调节为0?

最大限度地减少TRF7964A和TRF7970A省电模式下的电流消耗

最大限度地减少TPS53355和TPS53353系列器件的开关振铃

最大限度地提高GSPS ADC中的SFDR性能:杂散源和Mitigat方法

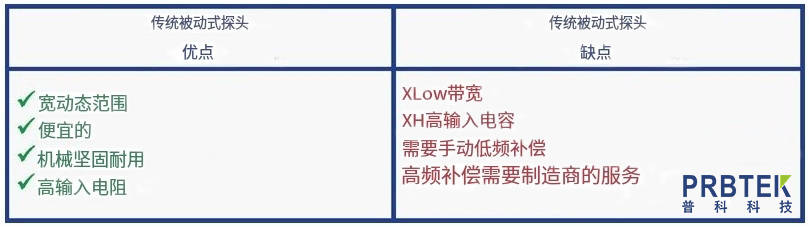

如何使用低电容探头最大限度地减少探头负载

怎么最大限度减少线缆设计中的串扰

怎么最大限度减少线缆设计中的串扰

评论