作者: TI专家 Bruce Trump

翻译: TI信号链工程师 Michael Huang (黄翔)

之前我们看了CMOS和JFET放大器输入偏置电流的来源,发现其主要由一个或几个反向偏置的PN节的漏电流组成。如果没看过该文章,请点击这里查看。文章结尾引出了一个警示,这些漏电流随着温度升高而显著的增大。

PN节的反向偏置漏电流有很强的正温度系数,每升高10℃,漏电流大约增大一倍。在figure1归一化曲线中可以看出,这种指数增长使得漏电流快速增加。到125℃时,漏电流相对室温下增长了约1000倍。

不同的二极管特性使得漏电流增加的速率不一样,两倍的漏电流可能在8℃到11℃左右的范围内发生。这种高温下的漏电流增长在一些电路中将会是重要问题,也可能是一个选择在室温下有着非常低输入偏置电流的FET或CMOS运放很好的理由。某些情况下,为了实现高温度下的低IB ,会使用在高温度下IB没那么夸张增长的BJT运放。

一般我们会假设在低温时,漏电流也继续降低,但是其他的泄漏源也许会改变这种趋势。这些杂散泄露可能会有不同的温度特性。坦率说,低于室温的情况我们知道的较少,因为我们更关注在室温及室温以上的较高的泄露。我们最好不要在远低于室温的情况下对其特性太自信。在低温下更能成为重要问题的是水可能会凝结,这可以使得泄露向上猛增。

之前讨论过CMOS运放的输入偏流主要来自于输入级上分别连接在电源轨上的两个钳位二极管的反向泄露电流的差异。即使一个完全平衡的世界,两个有着几乎相同泄露特性的二极管之间的漏电流残余差值仍然有着相同的指数温度变化,只是初始

值较低。IB 的极性是不确定的,并由于二极管特性的微小不同,净余的电流可能会在某个温度下降到零(对数坐标图上无法显示其绝对数值)。

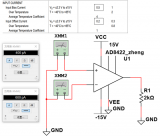

所以,什么结论?如果在您的FET运放电路中极低的输入偏置电流很关键,则认真考虑它随温度上升而增加的特性。学习全部的参数和典型性能图表。避免敏感电路接近热源。如果必要的话,制作您自己的测量。对于真正关键的应用,有特殊用途的超低输入偏置电流的放大器。他们用富有创造性的保护电路和独特的引脚排布,实现室温下3fA范围内的IB,低于通用器件3个数量级。例如:

LMP7721——3fA输入偏置电流CMOS运算放大器

INA116——超低输入偏置电流仪表放大器

阅读原文, 请访问http://e2e.ti.com/blogs_/b/thesignal/archive/2012/11/14/temperature-effects-on-input-bias-current-plus-a-random-quiz.aspx

编辑:jq

-

CMOS

+关注

关注

58文章

5750浏览量

236272 -

放大器

+关注

关注

143文章

13640浏览量

214399 -

运放电路

+关注

关注

38文章

362浏览量

35006

发布评论请先 登录

相关推荐

输入偏置电流仅100fA!思瑞浦推出飞安级运算放大器TPA3530

运算放大器的输入阻抗那么大,为什么还需要输入偏置电流?1000字搞定运放电路设计之输入偏置电流

LMH6401输入端输入阻抗100欧,需要考虑输入偏置电流吗?

运放的偏置电流和失调电流的区别

OPA277输入偏置电流IB和输入失调电流IOS的最大值,常温是多少?

OPAx387超高精度、零漂移、低输入偏置电流运算放大器数据表

TLVx387高精度、零温漂、低输入偏置电流运算放大器数据表

浅析温度对输入偏置电流的影响

浅析温度对输入偏置电流的影响

评论