互联标准之战,CXL正在走向胜利

在上世纪总线大战之下,各大厂商为了自己的开放标准纷纷全力出击,最终只留下PCIe统治着服务器市场。而在高性能计算对延迟、带宽要求越来越高的情况下,互联技术同样开展了类似的大战。CXL、CAPI(OpenCAPI)、CCIX、Gen-Z、AMD的Infinity Fabric与英伟达的NV Link等技术百花齐放,既有开放标准,也有专用标准。

这其中不少开放标准其实也都有对应的厂商在背后支持推动,比如CXL由英特尔主导,CCIX由赛灵思主导,OpenCAPI由IBM主导,Gen-Z由慧与主导。但这种分割的局面自然不是服务器市场内其他厂商想要看到的,他们希望能统一起来,为混合计算架构提供通用的互联方案,而不是一味地提供多种标准支持。好在这种局面似乎离我们不远了,从各种趋势来看,CXL正在走向最终的胜利。

从“言和”到“吞并”

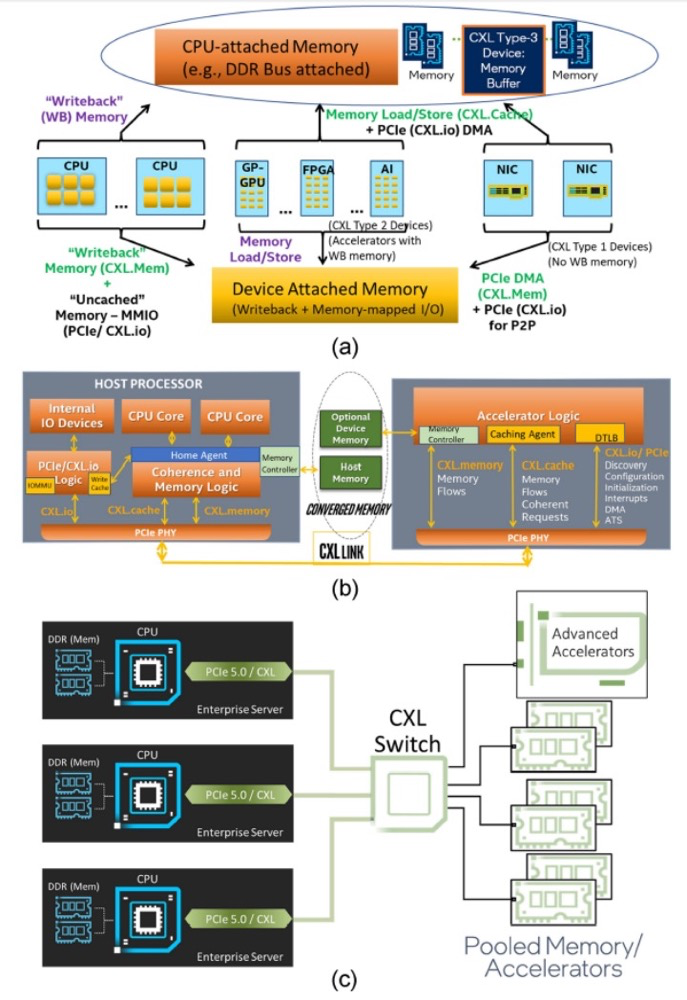

CXL作为开放的行业互联标准,其作用是为主处理器与其他设备之间提供高带宽低延迟的连接,比如加速器、内存扩展和其他智能I/O设备。CXL诞生的时间其实并不长,离第一版规范的发布也才过去两年而已,其联盟创始成员包括阿里巴巴、华为、英特尔和微软等企业。CXL诞生之际,CCIX、OpenCAPI和Gen-Z早就在耕耘服务器市场了,也利用这提前几年的时间召集了不少联盟成员,那么最晚面世的CXL又是如何杀出重围的呢?

首先自然是来自联盟成员的支持,尤其是当前服务器CPU份额遥遥领先的霸主英特尔,像Gen-Z这样的标准要想做CPU互联,必须要CPU端的支持。但英特尔并未加入Gen-Z联盟,更不用谈支持了,GPU、加速器等产品想要在服务器市场继续生存下去,加入英特尔推行的CXL阵营成了一个理所当然的选择。

CXL 1.0与1.1用例 / CXL联盟

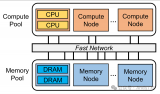

其次,CXL的I/O基于PCIe 5.0,可以充分利用它在速度和带宽上的优势。利用CXL,部分NIC等无本地内存的加速器可以直接使用处理器的DDR内存;而自带DDR或HBM内存的加速器,比如GPU、FPGA和ASIC设备等,可以实现内存互用,大大提高异构工作下的性能。内存扩展之类的产品利用CXL不仅可以省去宝贵的DRAM插槽,还能一并提高内存带宽。

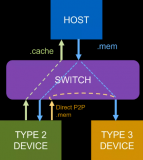

Gen-Z这样的标准虽不愿意服输,但在CXL如此强势的崛起下,内存厂商、IP厂商、处理器厂商和加速器厂商纷纷加入了CXL联盟,甚至慧与也是CXL的创始成员。Gen-Z无奈之下也只能选择“握手言和”。2020年,CXL联盟与Gen-Z联盟达成合作备忘录,强调了两者之间的合作共赢,CXL专注于一致的节点层级计算,也就是机架内CPU、GPU和加速器之间的互联,而Gen-Z负责支持机架之间的互联。

而今年11月10日,Gen-Z联盟与CXL联盟正式发布公告,两者签署了一份意向书,在各方同意后,将把所有Gen-Z规范和资产转移给CXL联盟,双方联盟成员将专注于CXL这唯一的互联标准,减少无意义的重复工作。如此一来,CXL基本正式“吞并”了Gen-Z,加上两者之间互补的特性,CXL已经确立了自己的领先地位。

来自厂商的支持

近几个月内,英特尔、AMD等大厂都相继推出了自己的服务器产品,从他们的产品支持来看,我们也能看出倾向于哪种互联标准。作为CXL的主导者,英特尔自然不会减少对CXL的支持,其公布的Sapphire Rapids处理器将提供PCIe 5.0和CXL 1.1的支持;尽管刚发布的Milan-X并没有CXL支持,但AMD也同时宣布下一代Epyc处理器Genoa将提供CXL支持。

Arm Neoverse路线图 / Arm

Arm的Neoverse N2平台已经提供了对CCIX 2.0和CXL 2.0的支持,Arm也宣布下一代Poseidon平台将支持下一代CCIX与CXL标准;SiFive不久前公布的Performance P550核心也将通过Chip2Chip-Link,支持外部CXL连接。

因此从处理器的支持来看,无论是x86、Arm还是RISC-V似乎都开始在往CXL布局。三星也在今年发布了首个支持CXL的DDR5内存模组,消除了传统DDR内存通道数的限制,可将内存扩展至TB级的同时,还能极大降低由于缓存造成的系统延迟。

小结

CXL仅用了两到三年的时间,就走完了其他标准长途跋涉的路,不过由于支持PCIe 5.0和CXL的服务器处理器普遍都在2022年面世,加速器和内存厂商跟进还需要一定的时间。而Gen-Z也并不会就此成为历史,被并入CXL后,未来内存从TB走向PB级,很有可能仍要用到Gen-Z所代表的互联技术。

在上世纪总线大战之下,各大厂商为了自己的开放标准纷纷全力出击,最终只留下PCIe统治着服务器市场。而在高性能计算对延迟、带宽要求越来越高的情况下,互联技术同样开展了类似的大战。CXL、CAPI(OpenCAPI)、CCIX、Gen-Z、AMD的Infinity Fabric与英伟达的NV Link等技术百花齐放,既有开放标准,也有专用标准。

这其中不少开放标准其实也都有对应的厂商在背后支持推动,比如CXL由英特尔主导,CCIX由赛灵思主导,OpenCAPI由IBM主导,Gen-Z由慧与主导。但这种分割的局面自然不是服务器市场内其他厂商想要看到的,他们希望能统一起来,为混合计算架构提供通用的互联方案,而不是一味地提供多种标准支持。好在这种局面似乎离我们不远了,从各种趋势来看,CXL正在走向最终的胜利。

从“言和”到“吞并”

CXL作为开放的行业互联标准,其作用是为主处理器与其他设备之间提供高带宽低延迟的连接,比如加速器、内存扩展和其他智能I/O设备。CXL诞生的时间其实并不长,离第一版规范的发布也才过去两年而已,其联盟创始成员包括阿里巴巴、华为、英特尔和微软等企业。CXL诞生之际,CCIX、OpenCAPI和Gen-Z早就在耕耘服务器市场了,也利用这提前几年的时间召集了不少联盟成员,那么最晚面世的CXL又是如何杀出重围的呢?

首先自然是来自联盟成员的支持,尤其是当前服务器CPU份额遥遥领先的霸主英特尔,像Gen-Z这样的标准要想做CPU互联,必须要CPU端的支持。但英特尔并未加入Gen-Z联盟,更不用谈支持了,GPU、加速器等产品想要在服务器市场继续生存下去,加入英特尔推行的CXL阵营成了一个理所当然的选择。

CXL 1.0与1.1用例 / CXL联盟

其次,CXL的I/O基于PCIe 5.0,可以充分利用它在速度和带宽上的优势。利用CXL,部分NIC等无本地内存的加速器可以直接使用处理器的DDR内存;而自带DDR或HBM内存的加速器,比如GPU、FPGA和ASIC设备等,可以实现内存互用,大大提高异构工作下的性能。内存扩展之类的产品利用CXL不仅可以省去宝贵的DRAM插槽,还能一并提高内存带宽。

Gen-Z这样的标准虽不愿意服输,但在CXL如此强势的崛起下,内存厂商、IP厂商、处理器厂商和加速器厂商纷纷加入了CXL联盟,甚至慧与也是CXL的创始成员。Gen-Z无奈之下也只能选择“握手言和”。2020年,CXL联盟与Gen-Z联盟达成合作备忘录,强调了两者之间的合作共赢,CXL专注于一致的节点层级计算,也就是机架内CPU、GPU和加速器之间的互联,而Gen-Z负责支持机架之间的互联。

而今年11月10日,Gen-Z联盟与CXL联盟正式发布公告,两者签署了一份意向书,在各方同意后,将把所有Gen-Z规范和资产转移给CXL联盟,双方联盟成员将专注于CXL这唯一的互联标准,减少无意义的重复工作。如此一来,CXL基本正式“吞并”了Gen-Z,加上两者之间互补的特性,CXL已经确立了自己的领先地位。

来自厂商的支持

近几个月内,英特尔、AMD等大厂都相继推出了自己的服务器产品,从他们的产品支持来看,我们也能看出倾向于哪种互联标准。作为CXL的主导者,英特尔自然不会减少对CXL的支持,其公布的Sapphire Rapids处理器将提供PCIe 5.0和CXL 1.1的支持;尽管刚发布的Milan-X并没有CXL支持,但AMD也同时宣布下一代Epyc处理器Genoa将提供CXL支持。

Arm Neoverse路线图 / Arm

Arm的Neoverse N2平台已经提供了对CCIX 2.0和CXL 2.0的支持,Arm也宣布下一代Poseidon平台将支持下一代CCIX与CXL标准;SiFive不久前公布的Performance P550核心也将通过Chip2Chip-Link,支持外部CXL连接。

因此从处理器的支持来看,无论是x86、Arm还是RISC-V似乎都开始在往CXL布局。三星也在今年发布了首个支持CXL的DDR5内存模组,消除了传统DDR内存通道数的限制,可将内存扩展至TB级的同时,还能极大降低由于缓存造成的系统延迟。

小结

CXL仅用了两到三年的时间,就走完了其他标准长途跋涉的路,不过由于支持PCIe 5.0和CXL的服务器处理器普遍都在2022年面世,加速器和内存厂商跟进还需要一定的时间。而Gen-Z也并不会就此成为历史,被并入CXL后,未来内存从TB走向PB级,很有可能仍要用到Gen-Z所代表的互联技术。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

amd

+关注

关注

25文章

5480浏览量

134316 -

英特尔

+关注

关注

61文章

9985浏览量

171972 -

服务器

+关注

关注

12文章

9239浏览量

85678

发布评论请先 登录

相关推荐

内存扩展CXL加速发展,繁荣AI存储

电子发烧友网报道(文/黄晶晶)CXL即Compute Express Link,是一种全新的互连协议,为各种处理器包括CPU、GPU、FPGA、加速器和存储设备提供统一接口标准,可以有效解决内存墙

韩国无晶圆厂初创公司Panmnesia展示第一个支持CXL的AI集群

在2024 OCP全球峰会上,开发CXL交换机SoC和CXL IP的韩国无晶圆厂初创公司Panmnesia展示了第一个支持CXL的AI集群,该集群采用CXL 3.1交换机。 OCP全球

拓展AI数据中心内存,第二代AMD Versal Premium系列自适应SoC,首发支持CXL 3.1、 PCIe Gen6

电子发烧友网报道(文/黄晶晶)在数据中心市场,DDR5和CXL内存正在成为广泛采用的主流趋势。预计2024年到2029年CXL内存的采用将达到212%的年复合增长率。如今,现有出货的半数服务器已经

研华科技推出SQRAM CXL 2.0 Type 3内存模块SQR-CX5N

10月15日最新消息,研华科技(Advantech)于昨日正式揭晓了其最新研发的SQRAM CXL 2.0 Type 3 内存模块——SQR-CX5N。该模块遵循EDSFF E3.S 2T标准,拥有

如何利用CXL协议实现高效能的计算架构

近日我有幸阅读了英特尔公司互联系统领域的权威人物Debendra Das Sharma撰写的一篇开创性文章——《Novel Composable and Scaleout Architectures

三星电子计划2024年下半年推出CXL存储

随着人工智能(AI)领域数据处理需求的爆炸性增长,全球存储厂商正竞相研发下一代存储解决方案,以应对这一挑战。三星电子在这一赛道上尤为亮眼,其在Compute Express Link(CXL)高速互联存储技术上的领先地位尤为显著,并计划于2024年下半年正式推出相关产品,

打造异构计算新标杆!国数集联发布首款CXL混合资源池参考设计

今日,领先的高速互联芯片及方案设计厂商国数集联发布业界首创的CXL混合资源池(Compute Express Link Hybrid Resource Pool ,以下简称“CHRP”)参考设计。该

新思科技CXL 3.1验证解决方案

、内存缓冲区、智能网络接口卡、持久存储器和固态驱动器等设备之间的开放式行业标准互连接口。CXL基于PCIe灵活的数据带宽提供了缓存一致性和存储语义,同时实现比PCIe低得多的延时。

国数集联发布业界首款CXL多级网络交换机,IB时代的颠覆者

今日,领先的高速互联芯片及方案设计厂商国数集联基于自主研发的CXL ( Compute Express Link )协议 IP,成功研发了业界第一款CXL多级网络交换机(CXL

国数集联研发出首款CXL多级网络交换机

今日,全球顶级高速互联芯片及解决方案设计专家——国数集联公司,凭借自主研发的CXL(Compute Express Link)协议IP,引领行业前沿,成功研发出全球首款CXL多级网络交换机(又名

胜利万用表的各个型号

胜利万用表是一款非常受欢迎的电子测量工具,广泛应用于电子、电气、通信、自动化等领域。在选择胜利万用表时,我们需要考虑多个因素,如测量范围、精度、功能、价格等。 胜利万用表的分类 胜利万

三星携手红帽成功构建全球首个CXL认证基础设施

近日,三星电子宣布了一个重要的里程碑事件:其首个经过全球领先的开源解决方案提供商红帽(Red Hat)认证的Compute Express Link(CXL)基础设施已成功构建。这一成果的取得

三星研发CXL混合存储模组,实现闪存与CPU数据直传

据三星展示的图片显示,此模组可以通过CXL接口在闪存部分及CPU之间进行I/O块传输,也可以运用DRAM缓存和CXL接口达到64字节的内存I/O传输。

利用CXL技术重构基于RDMA的内存解耦合

本文提出了一种基于RDMA和CXL的新型低延迟、高可扩展性的内存解耦合系统Rcmp。其显著特点是通过CXL提高了基于RDMA系统的性能,并利用RDMA克服了CXL的距离限制。

发表于 02-29 10:05

•3319次阅读

互联标准之战,CXL正在走向胜利

互联标准之战,CXL正在走向胜利

评论