在硬件加速器应用中,FPGA常被视为最优解,提供极致加速性能的同时,还具备重新编程的能力。尽管其灵活性成了FPGA的一大特色,但大批量生产FPGA的价格可不低。此外,FPGA作为传统的处理器加速方案,工程师必须要解决空间、I/O延迟和带宽之类的问题。

而近些年来,eFPGA(嵌入式FPGA)的概念正在不断兴起。与将芯片与必要的I/O和电源管理电路封装在一起的FPGA不同,eFPGA推行的是卖IP模式。任何厂商都可以将这些eFPGA IP放入自己的定制IC产品内,无论是ASIC、SoC还是SiP。也正因为eFPGA的种种优势,国外不少厂商都想借eFPGA率先抢占市场。

FlexLogic

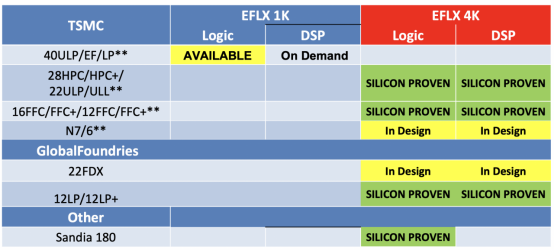

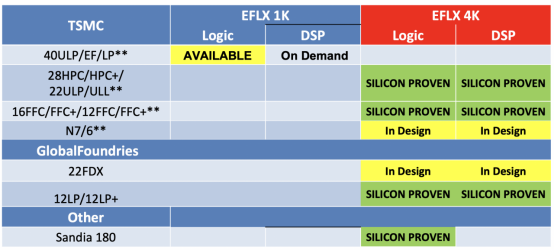

FlexLogic作为最早入局eFPGA的企业之一,已经投入了7年的研发,且eFPGA在2020年正式开始盈利,并与Dialog、大唐电信和波音等企业达成了合作。FlexLogic的EFLX eFPGA IP基本已经覆盖了主流的成熟工艺,比如Sandia美国国家实验室的180nm、格芯的12nm以及台积电的40nm、28/22nm、16/12nm,已完成了十数种芯片的流片。不仅如此,FlexLogic宣称格芯的22FDX和台积电的7/6nm也已经在设计阶段,下一步就是进军5nm。

EFLX eFPGA工艺节点 / FlexLogic

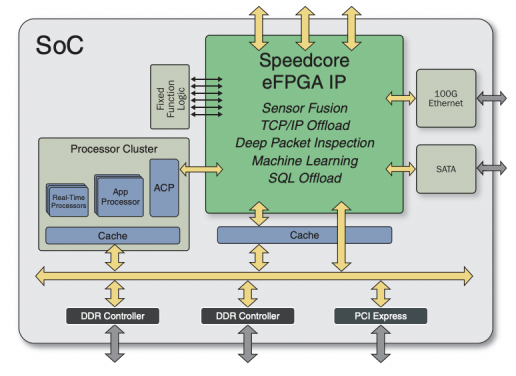

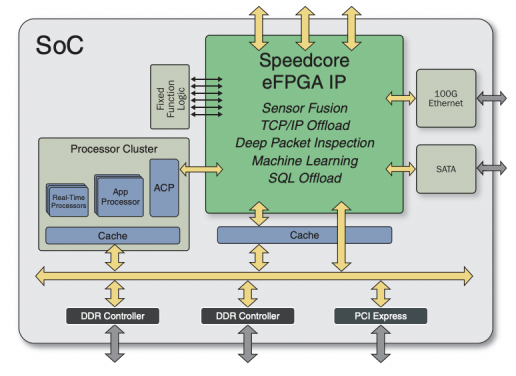

在FlexLogic看来,传统独立FPGA芯片+SoC的方案所需的功率太大,且多数需要高速SERDES或PCIe与其他芯片进行I/O互联。这种方案不仅功率过大,也因为SERDES/PHYS的存在带来了一定的面积成本,而eFPGA却可以做到低功耗、低成本和小面积,并将100K LUT塞入复杂的SoC设计中。而且在继承了FPGA可编程的特性后,即便是已经安装完成的产品,EFLX核心也可以用来升级I/O协议、改变加密算法等等。

InferX X1 / FlexLogic

eFPGA在重构时间上同样具备优势,因而在复杂的神经网络模型中更为适用。比如FlexLogic的AI推理芯片,InferX X1,在测试中,神经网络模型层级的动态重构只需6微秒。这使得InferX X1在具备ASIC性能的同时,也能对新的模型做出动态化处理,非常适合作为主处理器的加速器或协处理器,用于要求低功耗高性能的边缘AI市场。

这样的动态重构也为eFPGA带来了更多的应用方向,比如自动驾驶中的传感器融合方案,针对激光雷达、毫米波雷达和视觉等不同传感器数据进行处理。还有不同的PWM频率要求的多电机方案,在其中提供电机控制器支持。亦或是需要多不同指令集架构的CPU进行动态切换,比如ARM、RISC-V和ARC等。

Achronix

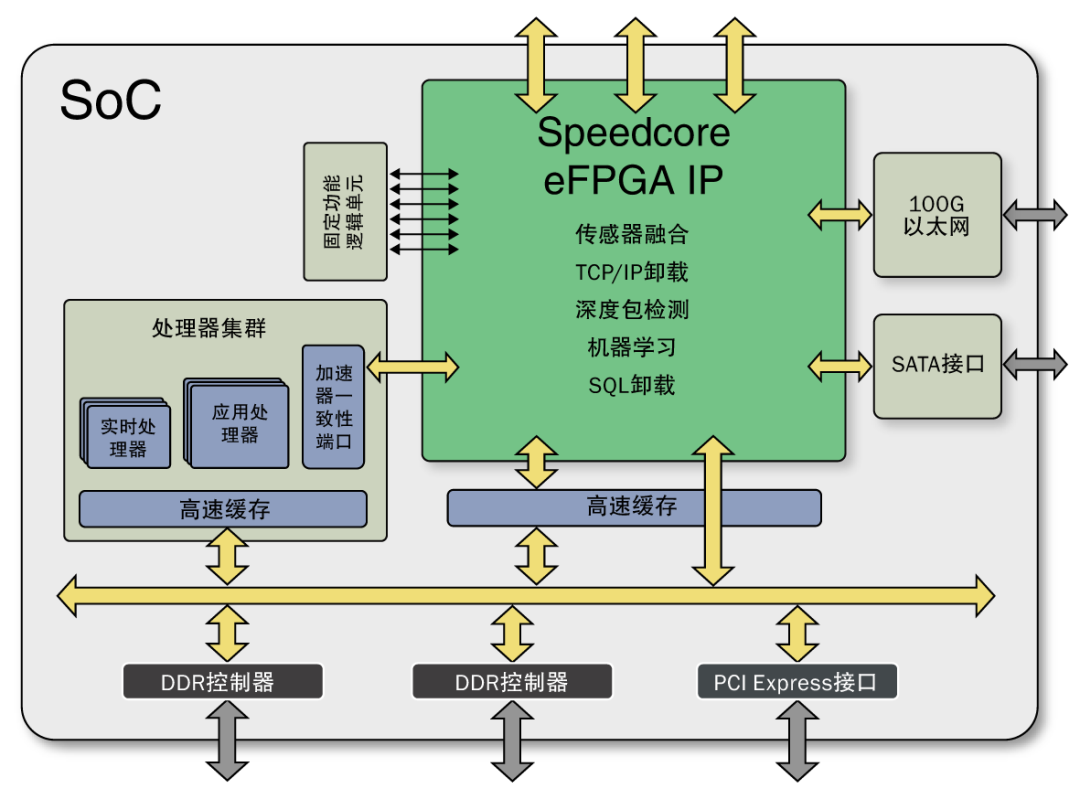

同样踏足eFPGA市场的还有美国公司Achronix。Achronix的Speedcore可以做到750MHz的峰值频率,且已经支持了台积电16nm、12nm和7nm三个成熟制程节点,也可以移植到其他节点上。

Speedcore/ Achronix

Achronix非常看好eFPGA在汽车市场的机遇,尤其是当下汽车开发周期缩短,又要支持10年以上的生命周期。我们以特斯拉这种开始走自研ASIC方向的厂商为例,与其他现成组件相比,虽然需要投入一定的开发成本,但ASIC提供的整体成本和性能都是最优的。与此同时,选择ASIC路线也带来了一定的风险。

首先,ASIC方案必须要对自己的方案有着清楚的认知。特斯拉的FSD ASIC开发历时近三年,如果这之后摄像头ISP需要更新,GPU需要支持浮点而不是FP32,都需要对ASIC架构的大改,很可能会进一步延长后续车型的生产,这也是为何少有汽车厂商选择该技术路线的原因。而将eFPGA IP集成在ASIC中,就为这些厂商提供了FPGA的嵌入式硬件编程能力,又不会像独立FPGA那样加大成本和功率。

小结

eFPGA还有不少优势,比如在加密和保护上,不仅可以支持各种加密算法,也可以保护IP资产被逆向工程。虽然几年前刚面世之际,eFPGA还是一个不成熟的技术,并没有在芯片设计领域产生多大的吸引力。随着几年的发展下来,经过晶圆厂的生产认证,设计流程和软件的完善,加上AI和自动驾驶的兴起,eFPGA已经成了一个可行的方案。但在ARM的IP厂商的前人经验下,eFPGA能否真正崛起,还需要等待更多的市场验证。

而近些年来,eFPGA(嵌入式FPGA)的概念正在不断兴起。与将芯片与必要的I/O和电源管理电路封装在一起的FPGA不同,eFPGA推行的是卖IP模式。任何厂商都可以将这些eFPGA IP放入自己的定制IC产品内,无论是ASIC、SoC还是SiP。也正因为eFPGA的种种优势,国外不少厂商都想借eFPGA率先抢占市场。

FlexLogic

FlexLogic作为最早入局eFPGA的企业之一,已经投入了7年的研发,且eFPGA在2020年正式开始盈利,并与Dialog、大唐电信和波音等企业达成了合作。FlexLogic的EFLX eFPGA IP基本已经覆盖了主流的成熟工艺,比如Sandia美国国家实验室的180nm、格芯的12nm以及台积电的40nm、28/22nm、16/12nm,已完成了十数种芯片的流片。不仅如此,FlexLogic宣称格芯的22FDX和台积电的7/6nm也已经在设计阶段,下一步就是进军5nm。

EFLX eFPGA工艺节点 / FlexLogic

在FlexLogic看来,传统独立FPGA芯片+SoC的方案所需的功率太大,且多数需要高速SERDES或PCIe与其他芯片进行I/O互联。这种方案不仅功率过大,也因为SERDES/PHYS的存在带来了一定的面积成本,而eFPGA却可以做到低功耗、低成本和小面积,并将100K LUT塞入复杂的SoC设计中。而且在继承了FPGA可编程的特性后,即便是已经安装完成的产品,EFLX核心也可以用来升级I/O协议、改变加密算法等等。

InferX X1 / FlexLogic

这样的动态重构也为eFPGA带来了更多的应用方向,比如自动驾驶中的传感器融合方案,针对激光雷达、毫米波雷达和视觉等不同传感器数据进行处理。还有不同的PWM频率要求的多电机方案,在其中提供电机控制器支持。亦或是需要多不同指令集架构的CPU进行动态切换,比如ARM、RISC-V和ARC等。

Achronix

同样踏足eFPGA市场的还有美国公司Achronix。Achronix的Speedcore可以做到750MHz的峰值频率,且已经支持了台积电16nm、12nm和7nm三个成熟制程节点,也可以移植到其他节点上。

Speedcore/ Achronix

Achronix非常看好eFPGA在汽车市场的机遇,尤其是当下汽车开发周期缩短,又要支持10年以上的生命周期。我们以特斯拉这种开始走自研ASIC方向的厂商为例,与其他现成组件相比,虽然需要投入一定的开发成本,但ASIC提供的整体成本和性能都是最优的。与此同时,选择ASIC路线也带来了一定的风险。

首先,ASIC方案必须要对自己的方案有着清楚的认知。特斯拉的FSD ASIC开发历时近三年,如果这之后摄像头ISP需要更新,GPU需要支持浮点而不是FP32,都需要对ASIC架构的大改,很可能会进一步延长后续车型的生产,这也是为何少有汽车厂商选择该技术路线的原因。而将eFPGA IP集成在ASIC中,就为这些厂商提供了FPGA的嵌入式硬件编程能力,又不会像独立FPGA那样加大成本和功率。

小结

eFPGA还有不少优势,比如在加密和保护上,不仅可以支持各种加密算法,也可以保护IP资产被逆向工程。虽然几年前刚面世之际,eFPGA还是一个不成熟的技术,并没有在芯片设计领域产生多大的吸引力。随着几年的发展下来,经过晶圆厂的生产认证,设计流程和软件的完善,加上AI和自动驾驶的兴起,eFPGA已经成了一个可行的方案。但在ARM的IP厂商的前人经验下,eFPGA能否真正崛起,还需要等待更多的市场验证。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

efpga

+关注

关注

1文章

33浏览量

15728

发布评论请先 登录

相关推荐

使用IP核和开源库减少FPGA设计周期

/prologue-the-2022-wilson-research-group-functional-verification-study/),70% 的 FPGA 项目落后于计划,12% 的项目落后计划 50% 以上。 为此,很多FPGA厂商都在自己EDA工具里嵌入

Achronix与BigCat Wireless建立战略合作伙伴关系

高性能FPGA和嵌入式FPGA(eFPGA)IP行业的领导者Achronix Semiconductor Corporation宣布与BigCat Wireless公司建立战略合作伙伴

Achronix Speedcore eFPGA的特性和功能

Speedcore嵌入式FPGA(embedded FPGA,eFPGA)知识产权(IP)产品是Achronix公司于2016年推出的颠覆性技术,并于当年开始向最终客户交付,目前出货量

Primemas选择Achronix eFPGA技术用于Chiplet平台

高性能 FPGA 和嵌入式FPGA (eFPGA) IP 的领导者 Achronix Semiconductor Corporation 和使用Chiplet 技术开发创新 SoC H

FPGA的IP软核使用技巧

FPGA的IP软核使用技巧主要包括以下几个方面:

理解IP软核的概念和特性 :

IP软核是指用硬件描述语言(如VHDL或Verilog)描述的功能块,但并不涉及具体的电路实现细节。它通

发表于 05-27 16:13

关于FPGA IP核

对于深入学习使用FPGA的小伙伴们,特别是一些复杂的、大规模的设计应用,适宜的IP核对开发能起到事半功倍的作用。IP核的概念与我们sdk里库的概念相似。IP即电路功能模块,用户可以直接

发表于 04-29 21:01

FPGA开发如何降低成本,比如利用免费的IP内核

FPGA开发过程中,利用免费的IP内核可以显著提高开发效率,减少设计成本。以下是一些关于如何利用免费IP内核进行FPGA开发的建议:

选择适合的IP

发表于 04-28 09:41

AMD FPGA中MicroBlaze的固化流程详解

AMD FPGA在配置了适当的启动模式后,上电即会按该模式去加载配置文件。以7系列FPGA为例,假设设置模式引脚M[2:0]=3’b001,

发表于 04-25 12:49

•673次阅读

中高端FPGA如何选择

随着国产FPGA的崛起,中低端产品中,很多国产FPGA都是不错的选择,性价比很高。高端FPGA中,往往还是以AMD和Intel为主,但最近这几年,Achronix公司的FPGA

发表于 04-24 15:09

芯璐科技数千万元天使轮投资,系FPGA芯片设计企业

芯璐科技作为一家以设计为主业的嵌入式FPGA及可编程SoC(PSoC)芯片供应商,拥有全面的EDA软件与FPGA硬件研发实力,专注于为工业、消费电子、通信以及汽车应用等各行各业提供优质的嵌入式FPGA(

Achronix与Bluespec联合宣布推出一款支持Linux的RISC-V软处理器

高性能FPGA芯片和嵌入式FPGA(eFPGA)硅知识产权(IP)领域的领先企业Achronix半导体公司,以及RISC-V工具和IP领域的

Achronix以创新FPGA技术推动智能汽车与先进出行创新

全球领先的高性能现场可编程门阵列(FPGA)和嵌入式FPGA(eFPGA)半导体知识产权(IP)提供商Achronix Semiconductor公司宣布,该公司将参加由私募股权和风

eFPGA异军突起,IP模式才是未来?

eFPGA异军突起,IP模式才是未来?

评论