Integrity 3D-IC 是 Cadence 新一代多芯片设计解决方案,它将硅和封装的规划和实现,与系统分析和签核结合起来,以实现系统级驱动的 PPA 优化。

原生 3D 分区流程可自动智能创建逻辑内存器件的 3D 堆叠配置,优化 3D 堆叠设计的 PPA 结果。

客户可以放心采用 Cadence Integrity 3D-IC 平台和 Samsung Foundry 的多 Die 实现流程,打造新一代超大规模计算、移动、汽车和人工智能应用。

中国上海,2021 年 11 月 18 日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS),作为 Samsung Advanced Foundry Ecosystem(SAFE)的紧密合作伙伴,Cadence 公司于宣布,Samsung Foundry 已经对 Cadence Integrity 3D-IC 平台的 2D-to-3D 原生 3D 分区流程进行了工艺认证。

利用新流程,客户可以将现有的 2D 设计分割成 3D 逻辑内存器件(Memory-on-logic)配置,与原来的 2D 设计相比,可以通过同构 3D 堆叠获得更好的功耗、性能和面积(PPA)结果。该流程还为分区设计提供了强大的 3D-IC 系统规划、实现和早期分析能力,是客户打造复杂的新一代超大规模计算、移动、汽车和人工智能应用的理想选择。

由于内存墙限制,RAM 的访问速度跟不上 CPU 的执行速度,导致整个系统因内存延迟而变慢。克服这个问题的方法之一是采用同构的堆叠配置,并将存储器放在逻辑之上。这种配置安装在同一封装中时,可以减少导线长度和面积,加快内存访问速度,因此有助于提高 CPU 核心的性能。

Integrity 3D-IC 平台的 3D 分区功能使用户能够分离出内存宏和标准单元,并将它们放置在 3D 同构堆叠内的两个不同裸片上。自动流程在宏和标准单元之间建立连接的同时,进行 3D 堆栈的分区和完整实现。最终确定每个裸片的内容之后,系统和封装就可以在 Integrity 3D-IC 平台上实现,进行凸点规划、实现、与其他裸片的协同设计,以及热、功耗和静态时序分析(STA)的早期分析。

“对于在 3D-IC 配置方面具有不同自动化分区要求的客户,可以利用 Samsung Foundry MDI 参考流程的这种独特功能来探索芯片堆叠的效果,该流程基于 Cadence 新款 Integrity 3D-IC 平台中的原生 3D 分区功能。”Samsung Electronics 工艺设计技术副总裁 Sangyun Kim 表示,“Cadence 和 Samsung 之间的这种成功合作为客户提供了 3D 堆叠设计的分区、实现和分析流程,使他们能够减小功耗和面积,同时提高整体系统性能。”

“通过与 Samsung Foundry 的持续合作,我们在多裸片设计实现领域进行了合作创新,并提供了自动化的原生 3D 分区流程。”Cadence 公司数字与签核事业部产品工程副总裁 Vivek Mishra 表示,“Samsung Foundry 用于多裸片设计实现的先进封装技术,结合 Cadence 集成化的 Integrity 3D-IC 平台,为我们的共同客户提供了强大的多裸片解决方案。”

Integrity 3D-IC 平台为客户提供了通用的控制面板和数据库、完整的规划系统、无缝集成的设计实现工具、集成化的系统级分析能力和易于使用的界面,并允许用户使用 Virtuoso Design Environment 和 Allegro 封装技术实现协同设计。该平台还包括更广泛的 Cadence 3D-IC 解决方案组合,包括用于电源分配网络(PDN)分析的 Voltus IC Power Integrity Solution、用于 3D 热分析的 Celsius Thermal Solver、用于 3D 签核时序的 Tempus Timing Signoff Solution 和用于电路布局验证(LVS)的 Pegasus Verification System。

责任编辑:haq

-

3D

+关注

关注

9文章

2878浏览量

107532 -

驱动

+关注

关注

12文章

1840浏览量

85289 -

Cadence

+关注

关注

65文章

921浏览量

142127

原文标题:Cadence Integrity 3D-IC平台通过Samsung Foundry 5LPE工艺设计堆叠的原生3D分区流程认证

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

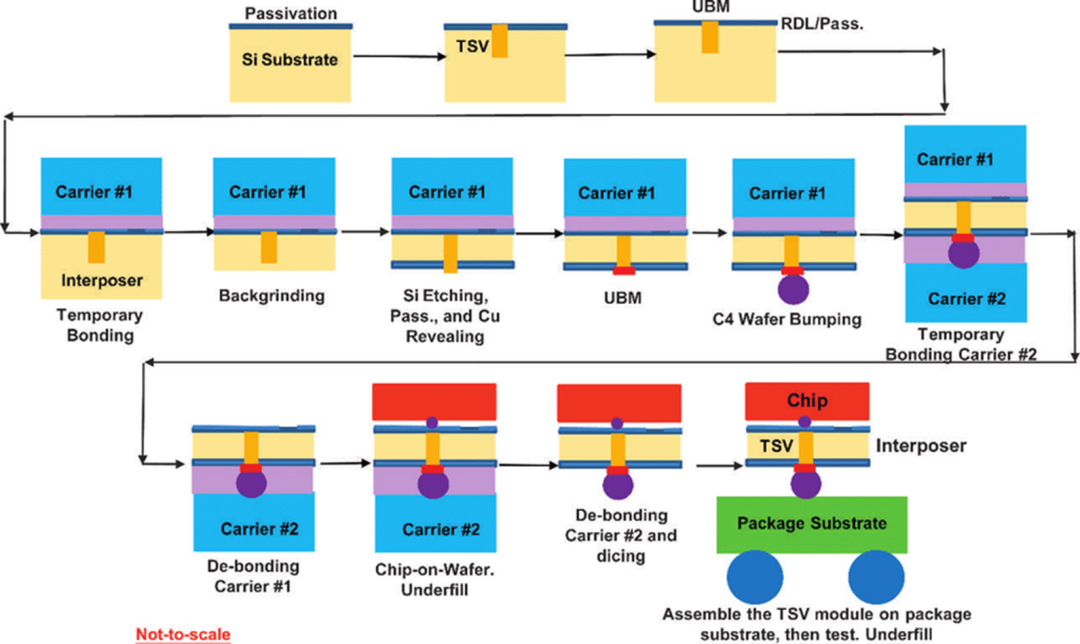

CoWoS工艺流程说明

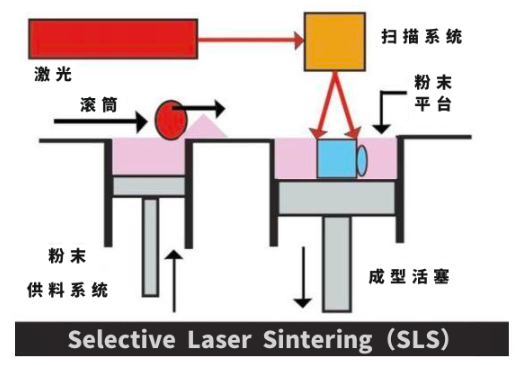

物联网行业中3D打印工艺——SLS(选择性激光烧结)工艺

物联网行业中3D打印工艺——FDM(熔融沉积成型技术)工艺

Cadence与Samsung Foundry开展广泛合作

剖析 Chiplet 时代的布局规划演进

Samsung 和Cadence在3D-IC热管理方面展开突破性合作

西门子推出Innovator3D IC,用于 3D IC 设计、验证和制造的多物理场集成环境

Cadence与Intel Foundry的战略合作取得重大成果

借助云计算加速3D-IC可靠性的机械应力模拟

Cadence与台积电深化合作创新,以推动系统和半导体设计转型

积木易搭通过亚马逊SPN服务商认证,成为平台指定3D商品展示服务商

3D-IC 以及传热模型的重要性

Cadence Integrity 3D-IC平台进行工艺认证

Cadence Integrity 3D-IC平台进行工艺认证

评论