摘要

本文深入探讨了跳频(FH)的概念,以及如何通过灵活设计 ADRV9002SDR 收发器的锁相环(PLL)架构来实现四大跳频特性。这些特性可为用户提供强大的跳频功能,让他们能够处理单通道和双通道操作模式下的Link 16和快速实时载波频率负载等应用。此外,跳频与多芯片同步(MCS)和数字预失真(DPD)技术的结合使ADRV9002 SDR收发器成为一种非常有吸引力的解决方案,可满足当今复杂通信系统中的更高要求。

简介

与传统的无线电通信不同,跳频(FH)定义了一种通过快速改变载波频率1来发送无线电信号的方法,Nikola Tesla在1903年的美国专利"信号传输方法"中首次提到了这种方法。后来,在1942年,女演员Hedy Lamarr和作曲家George Antheil进一步巩固了这一概念,他们从钢琴的按键数量得到启发,在88个频率之间切换,以防止鱼雷的无线电控制受到干扰。一百多年来,从第一次世界大战中固定指挥点之间的非实时、低速通信,到当代飞机、舰船和陆地系统之间的实时、高速多媒体通信,跳频在军事领域的应用已进入了一个崭新的时代。此外,跳频已广泛应用于许多无线个人通信网络,如蓝牙®个人局域网(PAN),以及消费电子和业余无线电领域,如对讲机、汽车模型和无人机。

什么是跳频?

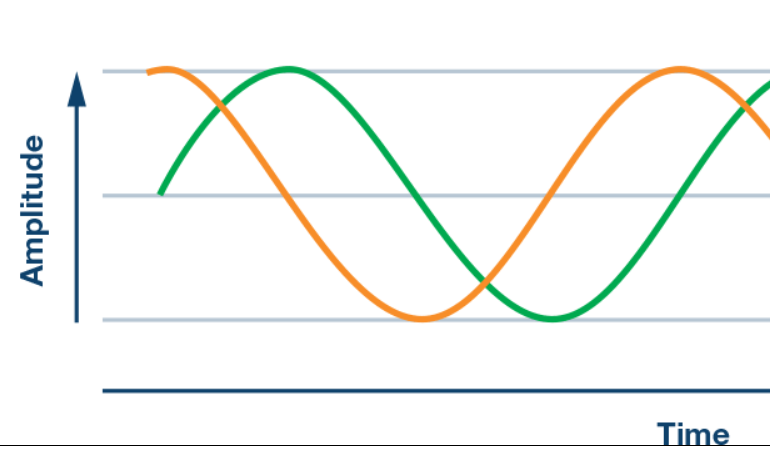

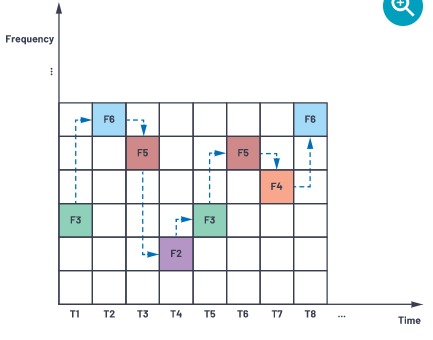

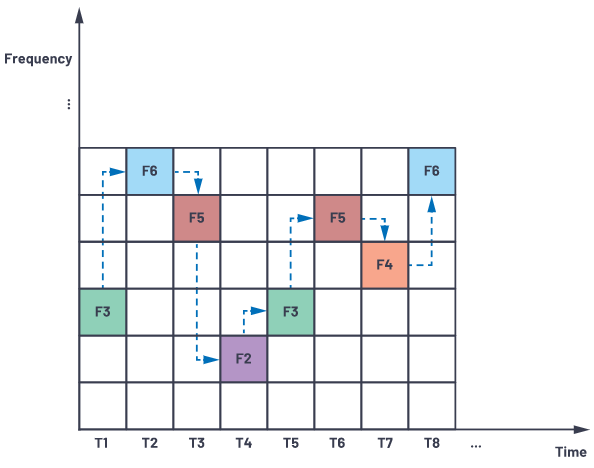

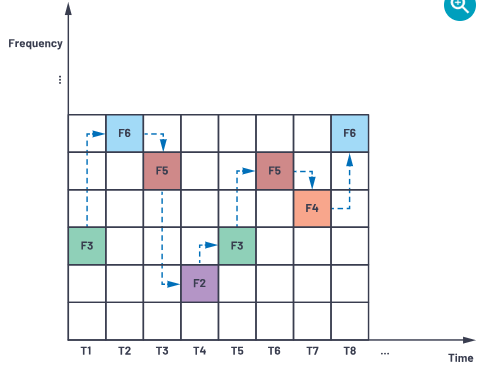

跳频的概念如图1所示。如果将整个频带和持续时间划分为二维网格,那么在任何给定的时隙,将会使用不同的频率子带进行通信。跳频模式的随机性相当于增加了另一个只能在发送器和接收器之间解码的安全层,使其具有较高的抗窄带干扰能力和较强的抗恶意拦截和封锁的能力。此外,跳频信号相互干扰小,可以和其他传统通信共享带宽,实现更高的频谱效率。随着跳频速率加快且使用更多的子频带,跳频的优势变得更加突出,成为对许多不同应用有吸引力的解决方案。

图1. 跳频的概念。

下一代SDR收发器

ADRV9002是一款双窄带和宽带SDR收发器,提供出色的RF性能和先进的系统功能,例如DPD和跳频。ADRV9002的工作频率为30 MHz至6 GHz,覆盖超高频(UHF)频带;特高频(VHF)频带;工业、科学和医疗(ISM)频带和蜂窝频段。可以支持窄带(kHz)和不超过40 MHz的宽带操作。图2显示了ADRV9002的简化示意框图。其中包括发送和接收双通道,以及一组高级数字信号处理算法。许多其他收发器都是将一个PLL专用于接收数据路径,另一个专用于发送数据路径,而以红色方框中显示的ADRV9002 PLL结构则比较独特,它在器件中使用两个RF PLL,并且可以选择将两个PLL提供给任何接收器或发送器使用,两个一起用或一个都不用。这种灵活性是在各种TDD应用中支持跳频的关键,例如单通道和双通道操作,包括仅发送模式(1T/2T)、仅接收模式(1R/2R)和发送/接收模式(1T1R/2T2R)。双通道操作支持通道分集和通道多路复用。此外,可以在乒乓模式下使用两个PLL,以满足严格的跳频时序要求。

图2. 采用灵活的PLL设计的ADRV9002简化示意框图。

ADRV9002的四大跳频特性

通过两个PLL多路复用和PLL快速重新调谐实现特快速跳频

跳频是通过在切换到不同频率之前重新调谐PLL来实现的。ADRV9002根据PLL的使用情况提供不同的跳频模式。2图1中的每个时隙代表一个跳帧,可以分为一个转换时间段和一个停留时间段,如图3所示。

图3. 跳帧结构。

在较慢的跳频模式下,如果频率变化之间的转换时间足够长(比通道设置时间和所需的PLL调谐时间长),则TDD操作中的一对发送和接收通道只需要一个PLL(称为一个PLL重新调谐模式)。为了实现更快的跳频和更短的转换时间(比通道设置时间和所需的PLL调谐时间短),在器件中则可以使用两个锁相环(称为两个PLL多路复用模式)。两个PLL以乒乓方式相互协调:当一个PLL用于当前频率时,另一个PLL则重新调谐至下一个频率。这样就可以实现快速跳频,从而大大缩短不同频率变化之间所需的转换时间。表1总结了这两种模式。

| 跳频模式 | 转换时间 | 通道对的PLL | 允许的PLL 重新调谐时间 |

| PLL多路复用 | 重新调谐时间<> | 两个PLL | <两次转换 + 一次停留时间 |

| PLL重新调谐 | >PLL重新调谐时间 | 一个PLL | <一次转换时间 |

如表1所示,要选择两种模式中的哪一种,由用户定义的转换时间决定。

图4进一步解释了PLL多路复用模式概念。如前所述,每个时隙代表一个跳帧,它由一个转换时间段和一个停留时间段组成。当一个PLL在停留时间内使用时,另一个PLL从同一跳帧的转换时间开始时即开始进行调谐。它可以一直进行调谐,直到下一个跳帧的转换时间段结束为止。所以,只要所需的PLL调谐时间比一次停留时间和两次转换时间的总和短,PLL多路复用模式就是成功的。

图4. 用于快速跳频的PLL多路复用模式。

PLL多路复用模式下的跳频对军事应用来说至关重要,例如Link 16。Link 16被认为是北大西洋公约组织(NATO)使用的最重要的战术数据链路标准之一,它使用960 MHz至1.215 GHz射频频段的抗干扰高速数字数据链路。3通过在初始化时准确校准整个跳频范围,ADRV9002采用快速PLL重新调谐模式来满足严格的时序要求。PLL重新调谐时间取决于ADRV9002 PLL参考时钟速率。表2显示在不同的PLL参考时钟速率下所需的快速PLL重新调谐时间。PLL参考时钟速率为300 MHz时,快速PLL重新调谐时间约为15 μs。Link 16的跳帧长度为13 μs时,如果转换时间大于2 μs,在使用PLL多路复用模式时使用15 μs的PLL重新调谐时间即可满足时序要求,具体如表1所示。

| PLL参考时钟(MHz) | 快速PLL重新调谐时间(μs) |

| 30 | 91 |

| 38.4 | 77 |

| 50 | 56 |

| 100 | 27 |

| 150 | 21 |

| 200 | 20 |

| 250 | 17 |

| 300 | 15 |

正如论文"在存在窄带干扰的情况下,通过缓慢、平坦的Nakagami 衰减通道传输的JTIDS/Link 16型波形的性能分析"3中所述,Link 16消息数据可以作为单脉冲或双脉冲发送,具体由打包结构决定。单脉冲结构包含6.4 μs开启时间和6.6 μs关闭时间,总持续时间为13 μs。双脉冲结构由两个单脉冲组成,它们传输相同的数据,但使用不同的载波频率,如图5所示。所以,转换时间大致为6.6 μs (>2 μs),因此使用ADRV9002实现Link 16跳频是完全可行的。

图5. 标准的Link 16双脉冲结构。

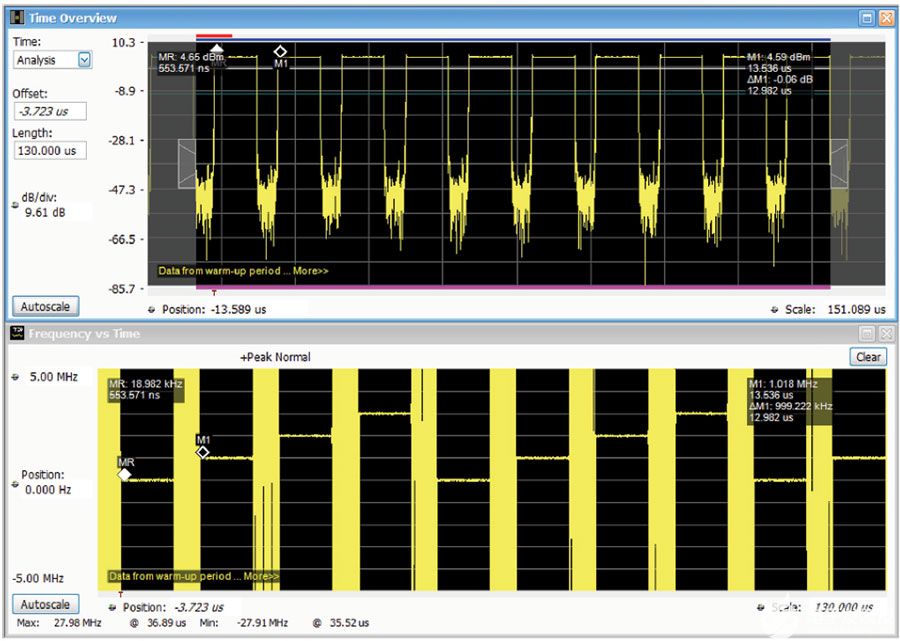

图6显示ADRV9002发送输出(功率与时间以及频率与时间之间的关系),采用Link 16型跳帧(为简化起见,仅使用发送跳频)。注意,为了显示ADRV9002可实现的最短转换时间,实验未使用图5中所示的标准Link 16脉冲结构,而是开启时间从6.4 μs增加到11 μs,关闭时间从6.6 μs缩短到2 μs。将Tektronix RSA306B频谱分析仪连接至ADRV9002评估板的发送输出端口,以进行观察。上方的图显示功率与时间的关系。从图中可以看出,每隔13 μs就会进行发送跳频,连续发送跳帧之间的转换时间大约为3 μs。下方的图显示频率与时间的关系。在这个实验中,发送载波频率以1 MHz的步长在四个不同的频率之间循环。正如预期的一样,下方的图证实了发送输出也以1 MHz的步长在四个不同的频率之间循环,并且在整个停留时间段内都具备出色的频率精度。

图6. Link 16 Tx跳频的发送输出。

通过使用更先进的测试设备(例如Keysight E5052B和R&S FSWP)可以进一步测量Link 16跳频的频率精度。在表3所示的测量示例中,发送载波频率在400 MHz、400.1 MHz、400.2 MHz和400.3 MHz时跳频。发送输入信号也相应的同步变换频率从而使所有跳帧生成400 MHz的频率输出。测量持续时间设置为100 μs,其中包括7个完整的跳帧。每隔128 ns测量一次频率。可以看出,在停留时间开始时,PLL已经完全锁定。停留时间期间的频率误差取决于相位噪声性能。表3显示这7个连续跳帧的平均、最大和最小频率偏移(输出频率和400 MHz之间的绝对差值)性能。在大多数帧中,平均频率误差低于1 ppm。数十次实验显示出同样的结果。注意,测量值可能因设备和测试配置而异。

| 跳帧编号 | 平均频率误差(Hz) | 最大频率误差(Hz) | 最小频率误差(Hz) |

| 1 | 348 | 730 | 46 |

| 2 | 424 | 997 | 4 |

| 3 | 267 | 563 | 20 |

| 4 | 327 | 892 | 7 |

| 5 | 253 | 569 | 2 |

| 6 | 394 | 903 | 12 |

| 7 | 253 | 677 | 17 |

ADRV9002还提供了用户微调PLL环路滤波器带宽的能力。当PLL环路滤波器带宽配置为1200 kHz时,可以实现表3所示的性能。较大的PLL滤波器带宽可以减少PLL重新调谐时间,确保在停留时间开始前PLL完全锁定。建议用户进一步评估其应用中所需的相位噪声性能来选择最合适的环路滤波器带宽。

使用静态和动态的方式加载高达128个不同频率的跳频表

ADRV9002针对所有跳频模式使用跳频表概念。2跳频表中的每一项包含了跳帧的频率和其他操作参数。跳频表可以是静态加载的,这表示它在初始化期间加载,之后不允许即时更改。它也可以是动态加载的,即在执行跳频期间加载;在这种情况下,用户可以即时更改表的内容。此外,还使用了类似乒乓的概念,因此用户可以选择性地加载两个不同的表,每个表包含最少1个、最多64个项。在一个表用于当前跳帧时,加载另一个表,准备用于下一个跳帧。每个项都会通知ADRV9002关于某个跳帧的配置。可以通过自动递增索引方式(如果是两个跳频表,则是从第一个表的第一项开始,到第二个表的最后一项,然后重新回到第一个表的第一项,如果是一个跳频表,则是连续循环),或通过数字GPIO指示的特定项对跳频表进行随时索引。

图7显示跳频表A和B,每个包含N个项(1 ≤ N ≤ 64)。表中的每个项包含4个重要参数:跳频、中频(仅用于接收IF模式)、接收增益表的索引,以及发送衰减。在TDD操作中,用户必须通过专用的通道设置信号(每个发送通道一个,每个接收通道一个)来通知ADRV9002为每个跳帧启用了哪个通道(发送或接收)。所以,尽管跳频表中的每个项都同时包含接收和发送参数,但只会使用相关参数。

图7. ADRV9002跳频表内容和索引方法。

在进一步探讨如何在跳频模式中使用跳频表之前,需要先了解ADRV9002和基带集成电路(BBIC)之间的大体的通信方式。

如图8所示,BBIC作为跳频操作的主要部分,会设置跳频模式、通道设置信号(Rx1_ENBALE、Rx2_ENABLE、Tx1_ENABLE和Tx2_ENABLE)、HOP信号(HOP1和HOP2),以及静态或动态跳频表(包含跳频、接收IF频率、接收增益表的索引和发送衰减)。BBIC通过SPI接口或DGPIO与ADRV9002通信。ADRV9002作为一个节点接收来自BBIC的信号,然后相应地配置数据路径和LO进行跳频。

图8. ADRV9002和BBIC如何在跳频期间互相通信的大概框图。

图9所示为一个动态表示例,每个跳频表A和B仅加载一个频率。这是一种极端情况,允许用户即时更改每个帧的跳频。本示例使用PLL多路复用模式。如图8所示,跳频信号的上升沿和下降沿定义跳帧的时序边界,如之前所述,每个跳帧由转换时间和停留时间组成。通道设置信号上升沿定义一个帧延迟(在PLL多路复用模式下,这种延迟是必要的)之后的跳帧类型。

图9. 在PLL多路复用模式下,动态的使用跳频表加载一个频率的示例。

注意,通道设置信号既可以表示发送设置信号,也可以表示接收设置信号。图9显示了该信号的简化版本示意图。由于TDD操作同时涉及发送和接收,用户需要分别配置发送设置信号和接收设置信号。除了指示跳帧类型,通道设置信号还可以用来触发BBIC进行跳频表加载。跳频表加载应在通道设置信号下降沿之后的那个跳频信号沿之前完成,然后PLL在同一跳频信号边沿开始调谐到该频率,并为由下一个跳频边沿指示的下一个跳帧做好准备。表A和表B以乒乓模式运行,这样加载完成后,一个表的频率用来进行跳频操作,同时对另一个表的频率实施调谐。

图10显示通过动态方式使跳频表每次加载4个项和8个项时发送输出频率与时间之间的关系。发送输入具有0 kHz、–100 kHz、–200 kHz和–300 kHz频率的4个帧,并通过连续循环这些帧将其馈送到ADRV9002。它与跳帧完全匹配和同步,所以0 kHz输入帧对应3.1 GHz LO。跳频期间,当LO变更为下一频率,发送输入频率也变更为下一频率。

图10. 用动态加载跳频表的方法每次载入4项和8项的跳频结果比较。

在执行跳频时,动态加载表A和表B(为了简化和便于观察,每次加载时表内容不改变)。对于每次加载4项,在3.1 GHz输出频率会看到四个连续的发送输出帧,然后在3.1004 GHz输出频率也会看到四个连续的发送输出帧,然后以这种模式循环往复。对于每次加载8项,在3.1 GHz输出频率会看到四个连续的发送输出帧,在3.1004 GHz输出频率4个连续帧,在3.1008 Hz输出频率四个连续帧,以及3.1012 GHz输出频率四个连续帧,然后以这种模式循环往复。图8所示的发送输出证实动态表加载操作如预期完全一致。

使用双通道来实现通道分集与通道多路复用

如图2所示,ADRV9002支持发送和接收双通道。可以对两个通道应用跳频,以实现通道分集或通道多路复用。

要实现分集,需使用同样的PLL(一个或两个)、同样的跳频表和TDD时序配置使两个通道同时跳频。用户可以启用ADRV9002提供的MCS功能,确保同一个或不同ADRV9002器件上的多个通道彼此完全同步,以保证确定性延迟。还可以通过MCS实现相位同步,但必须在每次PLL重新调谐频率时执行相应操作。通过MCS,实现了多个通道在跳频期间的同步,使ADRV9002成为 对涉及跳频的MIMO分集应用来说非常有吸引力的解决方案。了解在跳频期间使用MCS的要求和限制的更多详细信息,请参阅 ADRV9001系统开发用户指南。2

对于通道多路复用,每对发送和接受通道使用一个PLL,彼此独立地执行跳频。其中一个限制是特快跳频(要求为一个发送和接收通道对配备两个PLL)无法用于使一个ADRV9002器件的两对通道进行多路复用。

除了2T2R模式,还值得一提的是:ADRV9002还支持1T2R和2T1R的跳频操作,因而可以更灵活地满足用户的特定要求。

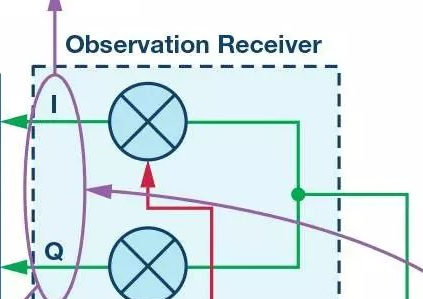

支持跳频与DPD操作同时进行

ADRV9002还支持窄带和宽带应用的DPD操作。它在实现符合标准的相邻通道功率泄漏比(ACPR)性能的同时,修正功率放大器(PA)的非线性,从而显著提高功率放大器的效率。

ADRV9002的一个高级功能是DPD可以和跳频一起执行。在这种情况下,ADRV9002允许用户配置多达8个频率区域,而DPD算法为每个频率区域创建一个优化解决方案。针对每个区域,DPD解决方案作为一组系数,可以分别在传输开始和结束时进行存储和加载。这可以确保在整个跳频范围内保持PA线性度。

由于DPD是一个自适应滤波过程,必须周期性地捕获一组样本进行系数计算,因此跳帧长度需要足够长才能满足DPD捕获长度要求。但是,如果用户只使用初始加载的DPD系数,无需进行DPD更新,则不存在这种限制。

ADRV9002的跟踪校准通常不会在快速跳频期间进行。但是,会根据用户的跳频配置,基于多个频率区域执行初始校准,以实现最佳性能。

使用ADRV9002收发器评估软件(TES)进行跳频性能评估

用户可以通过ADRV9002 TES软件在评估板上充分测试跳频性能。TES支持Xilinx® ZC706和ZCU102 FPGA评估板。2如图11所示,可以轻松使用跳频配置页面来配置跳频参数,包括跳频操作模式、跳频表、GPIO设置和TDD时序等。TES内置FPGA同步功能,因此用户能够准确控制TDD时序,确保发送或接收帧能完全与跳帧同步。TES中还提供许多跳频示例,供用户进一步分析研究。

图11. 通过TES配置跳频。

结论

跳频是下一代SDR收发器ADRV9002的先进系统特性之一。ADRV9002使用两个PLL、多种跳频模式,以及通过灵活加载和索引跳频表的方法,为用户提供出色的跳频能力,以便应对各种应用并满足更高系统要求。所有功能都可以通过ADRV9002 TES和软件开发套件(SDK)进行全面评估。

参考电路

1 John G. Proakis。数字通信,第3版。McGraw-Hill,1994年3月。

2 UG-1828:ADRV9001系统开发用户指南。ADI公司,2021年10月。

3Kao Chin-Han。 “在存在窄带干扰的情况下,通过缓慢、平坦的Nakagami 衰减通道传输的JTIDS/Link 16型波形的性能分析”。美国海军研究生院,2008年。

作者

Michelle Tan

Mizhou (Michelle) Tan是ADI公司的产品应用工程师。3年来,她一直为RF收发器产品和应用的设计和开发提供支持。在加入ADI公司之前,她获得了四川大学电气工程学士学位和硕士学位,并于2004年获得了新泽西理工学院电气和计算机工程博士学位。从2004年至2018年,她分别在Agere Systems、LSI Logic和Intel Corp.担任算法、系统和软件工程师。她在技术会议和期刊上发表论文15余篇,在无线通信和数字信号处理领域拥有9项已授权专利。

编辑:fqj

-

收发器

+关注

关注

10文章

3424浏览量

105961 -

锁相环

+关注

关注

35文章

584浏览量

87739 -

SDR

+关注

关注

7文章

233浏览量

50461 -

pll

+关注

关注

6文章

776浏览量

135131 -

无线电

+关注

关注

59文章

2139浏览量

116439

发布评论请先 登录

相关推荐

基于软件无线电的高速QPSK调制器的设计与实现

射频转换器为下一代无线基站提供高效的多波段无线电

Maxim推出下一代多协议收发器芯片组

软件定义无线电的应用

提供显著跳频(FH)优势的下一代软件定义无线电收发器

提供显著跳频(FH)优势的下一代软件定义无线电收发器

评论