引言

Preface

随着SoC设计规模呈指数级增长,芯片设计团队原型验证需求也变的越来越复杂。单通过增加系统容量的方式,还是会遇到诸多困难和挑战。设计团队需要有一个成熟的面向大规模SoC设计的高密原型验证系统的软硬件通用解决方案,来解决关键困难点的突破,降低项目风险。

本次国微思尔芯白皮书《高密原型验证系统解决方案》主要分析了用户在进行大规模SoC设计原型验证过程中在全局时钟及复位同步,大规模设计分割以及高速接口和先进Memory控制器IP验证等方面遇到的困难,并提出了相应的解决方案来帮助用户来克服这些困难。

三大核心问题

Main Point

大规模设计分割挑战及解决方案

Partition

由于大规模复杂SoC设计规模庞大,把设计映射到多个FPGA组成的网络(也称设计分割)是大规模原型系统实现过程中必不可少的重要环节。然而大规模设计分割也给用户的原型验证带来了不少的难题。

全局时钟及复位方案挑战及解决方案

Clock reset

全局时钟和复位的解决方案是构建一个大规模复杂SoC原型验证系统首先要考虑的问题。SoC原型验证系统需要保证系统的全局时钟和复位能够同步的送到原型验证系统的每一个FPGA节点,这是大规模SoC原型验证系统能够正常工作的先决条件。随着用户的SoC设计规模的增大,对原型验证系统的全局时钟和复位的同步方案的要求也会变得复杂。

高速接口和先进Memory控制器验证方案

Speed bridge

大规模复杂SoC设计原型验证时一些高速接口,如PCIe Gen3/Gen4接口,对应的PCIe控制器IP在FPGA里跑的速度都很低,无法对接外部实际PCIe主机或者设备。另外,一些先进的Memory控制器IP,如DDR5,LPDDR4/5,HBM2/3缺少FPGA 厂商提供的PHY解决方案,无法在FPGA原型验证系统中运行起来。遇到这些棘手的问题,有些用户甚至选择放弃这些高速接口及Memory IP在原型验证系统中的验证,但也因此会给用户的SoC设计原型验证带来风险。

原文标题:一文读懂 I 如何解决高密原型验证系统的三大核心问题?

文章出处:【微信公众号:国微思尔芯】欢迎添加关注!文章转载请注明出处。

审核编辑:彭菁

-

FPGA

+关注

关注

1629文章

21734浏览量

603113 -

芯片

+关注

关注

455文章

50756浏览量

423353 -

控制器

+关注

关注

112文章

16346浏览量

177905

原文标题:一文读懂 I 如何解决高密原型验证系统的三大核心问题?

文章出处:【微信号:S2C_Corporation,微信公众号:思尔芯S2C】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Omdia与华为共发布NPS管理白皮书

紫光同芯参编《智能底盘操作系统白皮书》发布

华为发布天线数字化白皮书

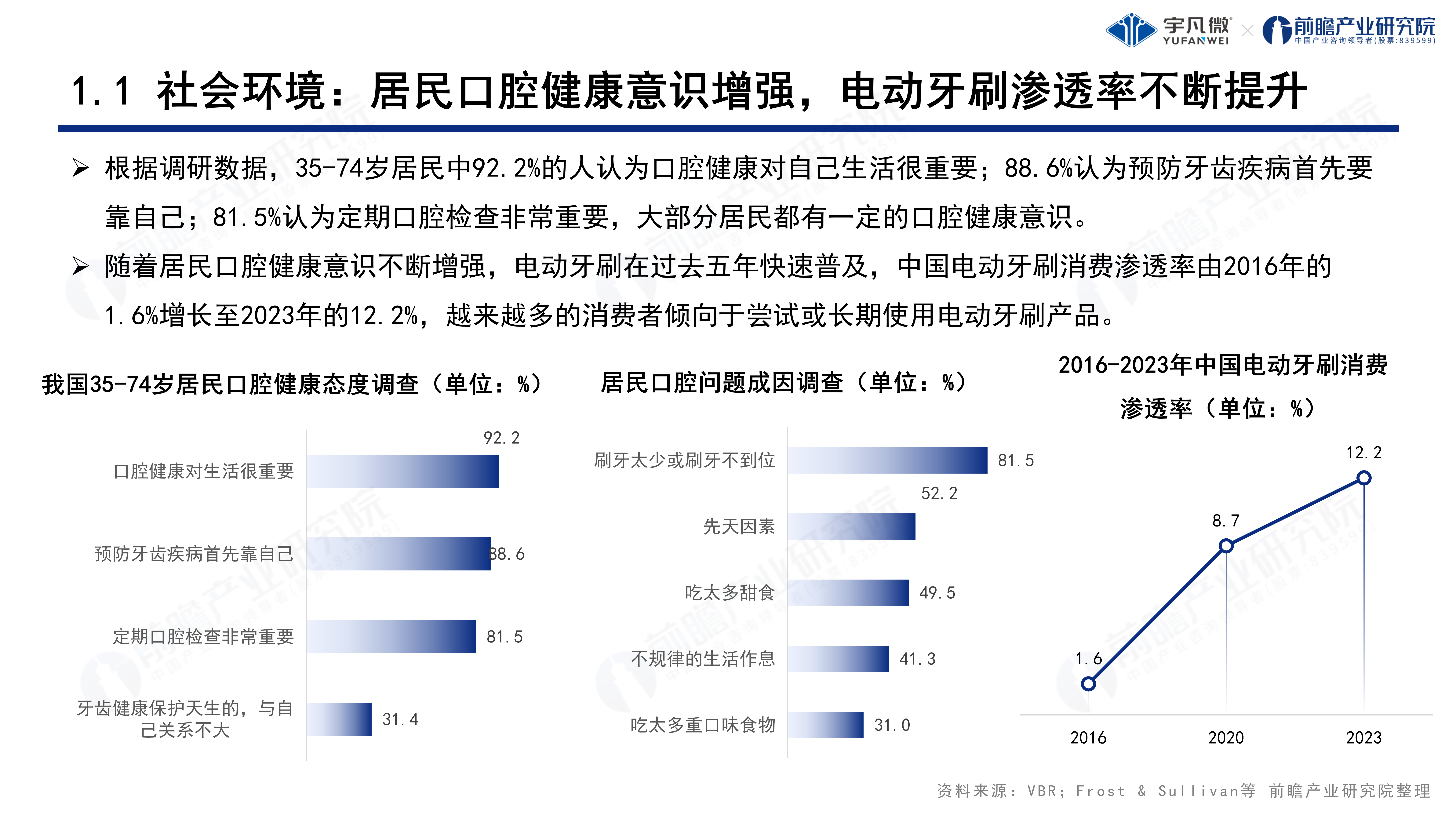

解锁电动牙刷方案新玩法!宇凡微联合前瞻研究院发布业内首份《电动牙刷伺服电机洞察白皮书》

美通社推出《智能科技行业媒体概况》白皮书

中科曙光联合发布《智能算力产业发展白皮书》

移远通信《5G RedCap技术发展及应用白皮书》重磅发布

Wi-Fi 7射频IP验证系统发布!思尔芯EDA助力Sirius Wireless加速芯片设计

国微思尔芯发布高密原型验证系统解决方案白皮书

国微思尔芯发布高密原型验证系统解决方案白皮书

评论