RISC-V在云端、数据中心、汽车与网络技术中的频繁创新和亮相,已经让这一成长中的ISA一只脚迈入了高性能计算场景。然而缺少强大的性能监测工具让RISC-V的应用优化成了问题,尤其是在RISC-V如今不少软件源于从非原生移植的情况下,运算性能不能发挥出百分百的实力成了令人头疼的问题。

与此同时,英特尔和ARM都拥有自己专用的性能监控方案,让开发者可以发挥出其硬件的全部效力,但RISC-V仍然依靠定制或厂商特定的方案,而缺少通用性能监控软件工具的完整支持。

Perf对RISC-V的支持

系统级的性能优化往往是靠性能剖析和代码优化来实现的,前者是为了寻找性能瓶颈,后者则是为了改善软件性能,因此这类性能分析/监控工具成了处理器开发时必不可少的软件。尽管RISC-V的ISA规范已经定义了硬件性能监控(HPM),但总体支持程度上仍未完善。

就以Linux上的性能分析工具Perf为例,该工具可以借助PMU(性能监控单元)、tracepoint和内核计数器来分析程序中的硬件事件,比如处理器时钟周期、指令计数器等,也可以分析一些软件事件,比如Page Fault等。

Perf分为两种模式,一种是perf stat,一种是perf record。如今上游Linux的perf虽然已经对RISC-V有了支持,但仅对perf stat有一些基本的支持。比如mcycle这一CSR用于处理器运行的时钟周期计数,而minstret这一CSR则用于退休指令计数。

RISC-V privileged规范中,RISC-V定义了几种特权模式,分别是U-mode(用户模式)、S-mode(管理员模式)和M-mode(机器模式)。但目前只有在机器模式下才能对这些寄存器进行读写,管理员模式下缺乏可写入的寄存器。

计数器却又是每时每刻运行中的,所以现在可以做到周期和指令计数,却无法启用、禁用和暂停计数器,无法使用任何可编程计数器和事件采样。不仅如此,RISC-V的perf不仅无法处理计数器溢出,也不支持溢出中断。虽然市面上很多RISC-V处理器已经考虑到了这一点,采用定制的形式来完成部分任务,比如Esperanto就为自己的ET-SoC-1千核RISC-V处理器加入了商业级的芯片除错与性能监控能力,但RISC-V规范本身缺少这些支持,这也就不利于当下RISC-V的开源生态。

完整的Perf支持缺少了什么?

于是我们现在发现管理员模式下无法写入计数器,也无法改变mcountinhibit来直接开启或停止计数器,也无法改变mhpmcountern来开启或禁用直接读取。接着就是没有中断指示器,我们不知道哪一个计数器出现了数值溢出,也没有事件筛选功能。那么针对这些问题的解决方案是什么,哪些措施才能实现完整的Perf支持呢?来自西部数据的Atish Patra在近期的RISC-V峰会上提出了他以及开发社区所青睐的答案——SBI PMU扩展和sscofpmf ISA扩展。

SBI PMU扩展将作为一个接口,让管理员模式下的软件发现硬件计数器的细节,针对特定的perf事件来配置硬件计数器,在请求下开始或停止计数器。除此之外,SBI PMU扩展还引入了固件性能计数器来监控固件事件,比如未对齐的存取指令数、RFENCE和IPI数等等。如今在RISC-V的SBI 1.0版本中我们也可以看到,PMU扩展已经成了该规范的一部分。

接着是sscofpmf扩展,ss代表的是特权架构和管理员级的扩展,cofpmf代表的是溢出计数和特权模式筛选。该扩展新增了一个32位的scountovf只读寄存器,该寄存器存储的是29个mhpmcounter的第63位(OF),如此一来就能准确快速地判断究竟是哪个事件的计数器溢出了。这一扩展已经冻结,目前处于审查状态,预计不久的将来就会批准,来自Linux内核的支持工作也在推进中。

小结

RISC-V作为一个尚处于发展初期的架构,在某些方面确实还有不及其前辈x86和ARM的地方,我们这次从性能监控上就能看出一些端倪,但RISC-V自身的特性也为它带来了不小的优势。

首先,RISC-V是站在巨人的肩膀上发展的,它可以有效地规避以上那些架构走错的老路。其次,开源开放让RISC-V有了庞大的社区支持,像以上这些解决方案,其实已经被多次提及,来自社区的力量势必可以让RISC-V走得更远。

审核编辑:何安淇

-

监测

+关注

关注

2文章

3525浏览量

44435 -

RISC-V

+关注

关注

44文章

2228浏览量

46007

原文标题:优化的关键,RISC-V中的性能监控

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

官方,buildroot文件系统支持gstreamer吗?

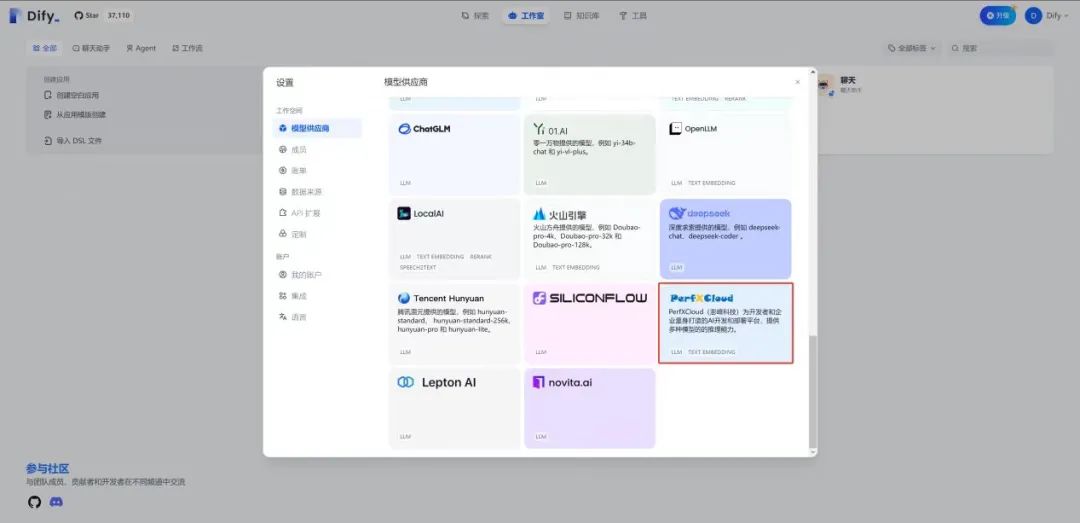

在Dify中使用PerfXCloud大模型推理服务

完整的Perf支持缺少了什么

完整的Perf支持缺少了什么

评论