作为一种高速总线接口技术,PCIe具有很多优势,比如大带宽和模块化,采用标准独特连接时可以优化成本及可靠性等。随着PCIe的应用日渐普及,越来越多的平台开始过渡到更新的PCIe标准。

PCIe 5.0作为最新一代的PCIe的标准,理所当然地成了数据中心高速计算处理持续演进的关键。不仅是作为CPU与AI加速器之间的纽带,越来越多的存储方案也开始从SAS/SATA转向PCIe,包括固态硬盘。不仅如此,在AI/ML这样的工作负载转变下,PCIe在PC、工作站、数据通信乃至汽车上的出镜率也越来越高,异构计算等架构也对带宽提出了更高的需求。

除了最小的PCIe系统以外,几乎所有系统中都需使用PCIe时钟分配器件,也就是缓冲器。 器件有限的引脚数目限制了单个器件中可以生成的PCIe时钟数量。某些情况下,电路板布线要求也会限制可在单个区域中可分配的时钟数量。

扇出缓冲器可将单个时钟从拥挤的电路板区域引出至需要多份拷贝的区域,然后缓冲器在本地扇出时钟。此外,在只有来自连接器的单PCIe时钟,却需要多份拷贝的情况下,也得靠扇出缓冲器来解决问题。

TI

TI的LMK00334就是一款经典的4路输出HCSL扇出缓冲器,具备两组双差分输出。该缓冲器采用了3:1输入多路复用器,其中两个通用输入工作频率高达400MHz,接受LVPECL、LVDS、CML、SSTL、HSTL、HCSL或单端时钟,另一个晶振输入则可以接受10MHz到40MHz的晶振或单端时钟。

LMK00334 / TI

该缓冲器兼容PCIe Gen1至Gen5的标准,在100MHz PCIe 5.0下的附加相位抖动低至30fs RMS。LMK00334的输入和性能特性,让其成了替代固定输出缓冲器的不二之选,如此低的附加抖动在服务器、射频拉远单元和基站单元可以说是一大优势。

瑞萨

瑞萨的9DBL0255和9DBL0455是针对PCIe 1到5应用的PCIe时钟扇出缓冲器,分别为2输出和4输出,其中9DBL0455的工作频率可高至267MHz。根据瑞萨在规格书上提供的数据,该系列在PCIe 5.0下可以做到小于15fs RMS的附加抖动值,在156.25MHz的高频下典型附加抖动为46fs RMS。

9DBL0255/0455原理图 / 瑞萨

该系列最大的特点在与集成了一个开漏信号丢失(LOS)输出电路,用于指示是否存在输入时钟。瑞萨也有内置PLL的PCIe缓冲器,不过在需要扩频的情况下,基本都要用到纯扇出缓冲器。而且在没有旁路mux的情况下,也进一步降低了传播延迟。

Skyworks

Skyworks在今年收购Silicon Labs基础设施和汽车业务后,Silicon Labs的部分产品全部归到了Skyworks旗下,扇出缓冲器也是其中之一。Si53212、Si53208 和 Si53204 是Skyworks高性能、附加抖动低的低功耗 PCIe 时钟缓冲器产品系列,分别可以获得 12、8 或 4 路 100 MHz 的 PCIe 时钟输出,均为非PLL的扇出缓冲器。

SI53212 原理图 / Skyworks

除了100MHz以外,该系列还支持10MHz到200MHz的输入频率。该系列所有差分时钟输出均符合 PCIe Gen1/2/3/4/5 公共时钟和单独参考时钟规格。该缓冲器产品系列支持扩频,可以用于对输入时钟进行扩频直通,进一步降低EMI以保证信号完整性。不过该系列的附加抖动没有做到极致,在PCIe 4.0下的附加抖动典型值为0.04ps。

随着越来越多的数据中心硬件设计正在使用1.5V或1.8V电源,以最大限度地降低整体功耗,比如网络接口控制器(NIC)、PCIe总线扩展器和高性能计算(HPC)加速器等。Si532xx系列缓冲器支持单个1.5V-1.8V电源供电,非常适合在这样的低功耗设计中提供低抖动PCIe时钟分发。除了支持PCIe通用时钟外,该系列也支持分离参考无展频(SRNS)和分离参考独立展频(SRIS)架构,能够满足各种应用需求。

极景微半导体

为突破高性能时钟芯片上“卡脖子”的困境,南京极景微半导体也在近日推出了两款支持PCIe 5.0接口标准的4/8输出时钟扇出缓冲器,分别是US5D334和US5D338,前者可为输入时钟创建4个缓冲副本,后者可产生8个缓冲副本。

虽然没有给出具体的数据,但极景微半导体称US5D334和US5D338可以直接以PIN2PIN的方式替代TI的LMK00334和LMK00338,而且能与未来极景微自研的US6S208时钟发生器结合,提供国产的高性能时钟树方案。极景微指出,这两款扇出缓冲器与同类竞争器件相比,支持锐降70%的附加抖动,而且支持显著提高的电源噪声抑制。

小结

其实不只是数据中心,移动互联网和汽车电子也在推动更高性能的时钟解决方案,不少厂商也都推出了车规级的PCIe缓冲器。在PCIe 5.0从今年年底正式开始铺开的情况下,扇出缓冲器市场也将迎来新一轮的爆发。

PCIe 5.0作为最新一代的PCIe的标准,理所当然地成了数据中心高速计算处理持续演进的关键。不仅是作为CPU与AI加速器之间的纽带,越来越多的存储方案也开始从SAS/SATA转向PCIe,包括固态硬盘。不仅如此,在AI/ML这样的工作负载转变下,PCIe在PC、工作站、数据通信乃至汽车上的出镜率也越来越高,异构计算等架构也对带宽提出了更高的需求。

除了最小的PCIe系统以外,几乎所有系统中都需使用PCIe时钟分配器件,也就是缓冲器。 器件有限的引脚数目限制了单个器件中可以生成的PCIe时钟数量。某些情况下,电路板布线要求也会限制可在单个区域中可分配的时钟数量。

扇出缓冲器可将单个时钟从拥挤的电路板区域引出至需要多份拷贝的区域,然后缓冲器在本地扇出时钟。此外,在只有来自连接器的单PCIe时钟,却需要多份拷贝的情况下,也得靠扇出缓冲器来解决问题。

TI

TI的LMK00334就是一款经典的4路输出HCSL扇出缓冲器,具备两组双差分输出。该缓冲器采用了3:1输入多路复用器,其中两个通用输入工作频率高达400MHz,接受LVPECL、LVDS、CML、SSTL、HSTL、HCSL或单端时钟,另一个晶振输入则可以接受10MHz到40MHz的晶振或单端时钟。

LMK00334 / TI

该缓冲器兼容PCIe Gen1至Gen5的标准,在100MHz PCIe 5.0下的附加相位抖动低至30fs RMS。LMK00334的输入和性能特性,让其成了替代固定输出缓冲器的不二之选,如此低的附加抖动在服务器、射频拉远单元和基站单元可以说是一大优势。

瑞萨

瑞萨的9DBL0255和9DBL0455是针对PCIe 1到5应用的PCIe时钟扇出缓冲器,分别为2输出和4输出,其中9DBL0455的工作频率可高至267MHz。根据瑞萨在规格书上提供的数据,该系列在PCIe 5.0下可以做到小于15fs RMS的附加抖动值,在156.25MHz的高频下典型附加抖动为46fs RMS。

9DBL0255/0455原理图 / 瑞萨

该系列最大的特点在与集成了一个开漏信号丢失(LOS)输出电路,用于指示是否存在输入时钟。瑞萨也有内置PLL的PCIe缓冲器,不过在需要扩频的情况下,基本都要用到纯扇出缓冲器。而且在没有旁路mux的情况下,也进一步降低了传播延迟。

Skyworks

Skyworks在今年收购Silicon Labs基础设施和汽车业务后,Silicon Labs的部分产品全部归到了Skyworks旗下,扇出缓冲器也是其中之一。Si53212、Si53208 和 Si53204 是Skyworks高性能、附加抖动低的低功耗 PCIe 时钟缓冲器产品系列,分别可以获得 12、8 或 4 路 100 MHz 的 PCIe 时钟输出,均为非PLL的扇出缓冲器。

SI53212 原理图 / Skyworks

除了100MHz以外,该系列还支持10MHz到200MHz的输入频率。该系列所有差分时钟输出均符合 PCIe Gen1/2/3/4/5 公共时钟和单独参考时钟规格。该缓冲器产品系列支持扩频,可以用于对输入时钟进行扩频直通,进一步降低EMI以保证信号完整性。不过该系列的附加抖动没有做到极致,在PCIe 4.0下的附加抖动典型值为0.04ps。

随着越来越多的数据中心硬件设计正在使用1.5V或1.8V电源,以最大限度地降低整体功耗,比如网络接口控制器(NIC)、PCIe总线扩展器和高性能计算(HPC)加速器等。Si532xx系列缓冲器支持单个1.5V-1.8V电源供电,非常适合在这样的低功耗设计中提供低抖动PCIe时钟分发。除了支持PCIe通用时钟外,该系列也支持分离参考无展频(SRNS)和分离参考独立展频(SRIS)架构,能够满足各种应用需求。

极景微半导体

为突破高性能时钟芯片上“卡脖子”的困境,南京极景微半导体也在近日推出了两款支持PCIe 5.0接口标准的4/8输出时钟扇出缓冲器,分别是US5D334和US5D338,前者可为输入时钟创建4个缓冲副本,后者可产生8个缓冲副本。

虽然没有给出具体的数据,但极景微半导体称US5D334和US5D338可以直接以PIN2PIN的方式替代TI的LMK00334和LMK00338,而且能与未来极景微自研的US6S208时钟发生器结合,提供国产的高性能时钟树方案。极景微指出,这两款扇出缓冲器与同类竞争器件相比,支持锐降70%的附加抖动,而且支持显著提高的电源噪声抑制。

小结

其实不只是数据中心,移动互联网和汽车电子也在推动更高性能的时钟解决方案,不少厂商也都推出了车规级的PCIe缓冲器。在PCIe 5.0从今年年底正式开始铺开的情况下,扇出缓冲器市场也将迎来新一轮的爆发。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

PCIe

+关注

关注

15文章

1235浏览量

82597 -

扇出缓冲器

+关注

关注

0文章

3浏览量

5913

发布评论请先 登录

相关推荐

LMK00725低电压正射极耦合逻辑(LVPECL)扇出缓冲器数据表

电子发烧友网站提供《LMK00725低电压正射极耦合逻辑(LVPECL)扇出缓冲器数据表.pdf》资料免费下载

发表于 08-23 11:16

•0次下载

LMK00804B低偏移1到4多路复用差动/LVCMOS到LVCMOS/TTL扇出缓冲器数据表

电子发烧友网站提供《LMK00804B低偏移1到4多路复用差动/LVCMOS到LVCMOS/TTL扇出缓冲器数据表.pdf》资料免费下载

发表于 08-23 10:33

•0次下载

具有通用输入的LMK00101超低抖动LVCMOS扇出缓冲器/电平转换器数据表

电子发烧友网站提供《具有通用输入的LMK00101超低抖动LVCMOS扇出缓冲器/电平转换器数据表.pdf》资料免费下载

发表于 08-22 11:48

•0次下载

LMK00105具有通用输入的超低抖动LVCMOS扇出缓冲器和电平转换器数据表

电子发烧友网站提供《LMK00105具有通用输入的超低抖动LVCMOS扇出缓冲器和电平转换器数据表.pdf》资料免费下载

发表于 08-22 11:47

•0次下载

LMK00334-Q1四路输出PCIe第1代至第5代时钟缓冲器和电平转换器数据表

电子发烧友网站提供《LMK00334-Q1四路输出PCIe第1代至第5代时钟缓冲器和电平转换器数据表.pdf》资料免费下载

发表于 08-21 10:49

•0次下载

LMK00334四路输出PCIe第1代至第5代时钟缓冲器和电平转换器数据表

电子发烧友网站提供《LMK00334四路输出PCIe第1代至第5代时钟缓冲器和电平转换器数据表.pdf》资料免费下载

发表于 08-20 10:03

•0次下载

具有通用输入和输出的CDCUN1208LP 400MHz低功耗2:8扇出缓冲器数据表

电子发烧友网站提供《具有通用输入和输出的CDCUN1208LP 400MHz低功耗2:8扇出缓冲器数据表.pdf》资料免费下载

发表于 08-20 09:18

•0次下载

SN65EL11 5v PECL/ECL 1:2扇出缓冲器数据表

电子发烧友网站提供《SN65EL11 5v PECL/ECL 1:2扇出缓冲器数据表.pdf》资料免费下载

发表于 07-10 11:22

•0次下载

SN65LVEL11 3.3V ECL 1:2扇出缓冲器数据表

电子发烧友网站提供《SN65LVEL11 3.3V ECL 1:2扇出缓冲器数据表.pdf》资料免费下载

发表于 07-08 11:52

•0次下载

SN65LVEP11 2.5 V/3.3V PECL/ECL 1:2扇出缓冲器数据表

电子发烧友网站提供《SN65LVEP11 2.5 V/3.3V PECL/ECL 1:2扇出缓冲器数据表.pdf》资料免费下载

发表于 07-08 11:37

•0次下载

DS25MB200双通道信号调理多路复用器和扇出缓冲器数据表

电子发烧友网站提供《DS25MB200双通道信号调理多路复用器和扇出缓冲器数据表.pdf》资料免费下载

发表于 07-04 09:50

•0次下载

缓冲器是干嘛的

缓冲器是干嘛的 缓冲器是一种广泛应用于电子、电气、通信、计算机、自动化控制等领域的电子元件。它的作用是在电路中起到稳定电压、电流、信号等参数的作用,以保证电路的正常工作和性能。本文将详细介绍缓冲器

电源瞬态缓冲器的作用是什么

电源瞬态缓冲器的作用是什么 电源瞬态缓冲器是一种电子设备,用于保护电源系统免受瞬态电压尖峰、浪涌和其他电气干扰的影响。这些瞬态事件可能导致设备损坏、性能下降甚至系统故障。本文将详细介绍电源瞬态缓冲器

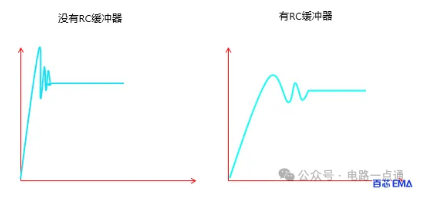

rc缓冲器的原理和作用

RC缓冲器是一种利用电阻(R)和电容(C)组合来控制或改变电路中信号的电路。它的主要功能是对信号进行整形、延时、滤波或降低噪声等。RC缓冲器广泛应用于数字和模拟电路中,以改善电路的性能。 工作原理

PCIe 5.0推行下再迎爆点的扇出缓冲器

PCIe 5.0推行下再迎爆点的扇出缓冲器

评论