从目前的芯片制程技术上来看,1nm(纳米)确实将近达到了极限!为什么这么说呢?芯片是以硅为主要材料而制造出来的,硅原子的直径约0.23纳米,再加上原子与原子之间会有间隙,每个晶胞的直径约0.54纳米(晶胞为构成晶体的最基本几何单元)!1纳米只有约2个晶胞大小。

1纳米单位到底有多小?

纳米也属于长度单位,可能很多人不了解它到底有多小?毫米(mm)、厘米(cm)、米(m)大家都比较熟悉,10mm=1cm,100cm=1m,1mm=1/1000m。单位长度由大到小排列依次为:米(m)、分米(dm)、厘米(cm)、毫米(mm)、微米(μm)、纳米(nm),1m=1000mm,1mm=1000μm,1μm=1000nm,即1nm=10^-9m,相当于1米平均分成10亿份!每一份为1nm。

XX nm制造工艺是什么概念?

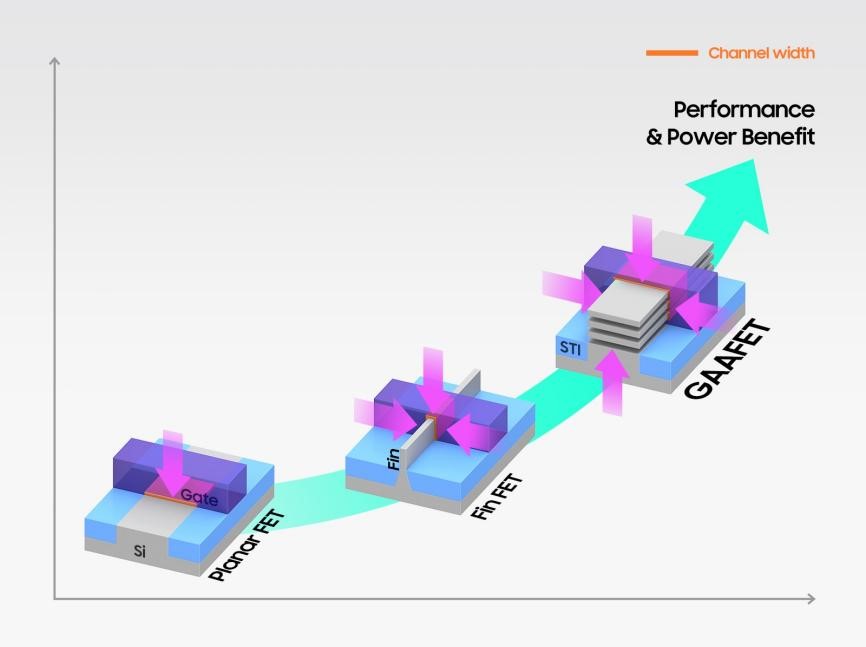

芯片的制造工艺常常用90nm、65nm、40nm、28nm、22nm、14nm来表示,比如Intel最新的六代酷睿系列CPU就采用Intel自家的14nm制造工艺。现在的CPU内集成了以亿为单位的晶体管,这种晶体管由源极、漏极和位于他们之间的栅极所组成,电流从源极流入漏极,栅极则起到控制电流通断的作用。

所谓的XX nm其实指的是,CPU上形成的互补氧化物金属半导体场效应晶体管栅极的宽度,也被称为栅长。栅长越短,则可以在相同尺寸的硅片上集成更多的晶体管——Intel曾经宣称将栅长从130nm减小到90nm时,晶体管所占面积将减小一半;在芯片晶体管集成度相当的情况下,使用更先进的制造工艺,芯片的面积和功耗就越小,成本也越低。

本文整合自:电工之家、电科技

审核编辑:符乾江

-

芯片

+关注

关注

455文章

50732浏览量

423275 -

半导体

+关注

关注

334文章

27305浏览量

218183

发布评论请先 登录

相关推荐

台积电1nm进展曝光!预计投资超万亿新台币,真有必要吗?

使用双TPA3118做双声道,负芯片无法识别同步,发热厉害怎么解决?

调试THS4021,频率上到1M以上之后,输入会衰减的很厉害,为什么?

4nm!小米 SoC芯片曝光!

三星将为DeepX量产5nm AI芯片DX-M1

2024年全球与中国7nm智能座舱芯片行业总体规模、主要企业国内外市场占有率及排名

什么是芯片底部填充胶,它有什么特点?

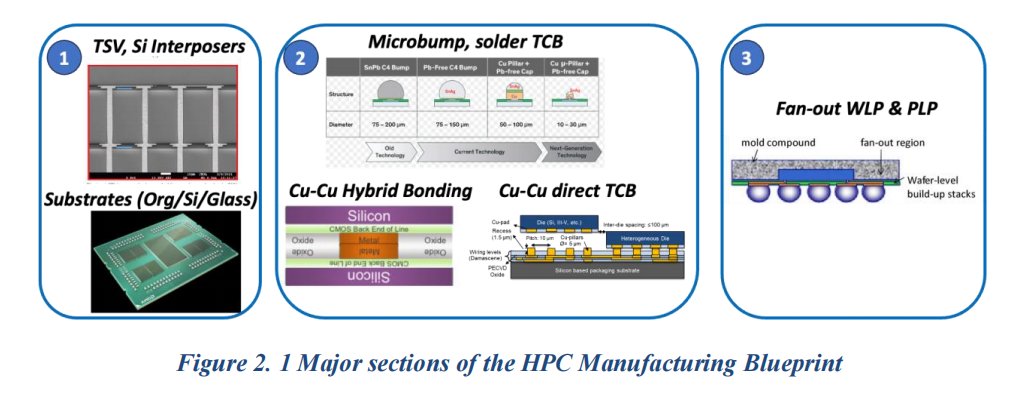

1nm后的芯片,靠什么?

1nm芯片是什么概念,它有多厉害

1nm芯片是什么概念,它有多厉害

评论