缓冲区其实就是一个存储区域,它是由专门的硬件寄存器所组成的。

缓冲区根据其对应的输入设备和输出设备,分为输入缓冲区和输出缓冲区。

使用硬件作为缓冲区的成本较高,容量也较小,一般仅用在对速度非常高的场合(存储器管理寄存器,有对页表访问的频率较高,因此使用速度很快的联想寄存器来存放页表项的副本)。

一般情况下更多的是使用内存作为缓冲区,缓冲区就是一块内存区。

缓冲区的作用

减少对CPU的中断频率,放宽对CPU中断相应的时间限制;

解决数据粒度不匹配的问题;

提高CPU和IO设备之间的并行性;

缓和CPU和IO设备之间速度不匹配矛盾。

缓冲区的作用就是为了解决速度不匹配的问题,高速的cpu与内存,内存与硬盘,cpu与io等速度不匹配的问题。

还有在一些厂商资料中还被写为CacheBuffer。缓冲区的基本作用是平衡内部与外部的DTR。

本文综合整理自百度百科、雪V歌、亓旎豆晗琴

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

缓冲区

+关注

关注

0文章

33浏览量

9211 -

寄存器

+关注

关注

31文章

5390浏览量

121891 -

缓冲

+关注

关注

0文章

53浏览量

17893

发布评论请先 登录

相关推荐

RTOS的流缓冲区机制解析

SAFERTOS中的流缓冲区(Stream buffer)机制,可以实现任务到任务或中断到任务之间的通信。字节流是由发送方写入缓冲区,接收方读取缓冲区数据。流缓冲区作为队列的轻量级级替

AMD Zen 4处理器悄然禁用循环缓冲区

近日,AMD在更新BIOS后,对Zen 4架构的处理器进行了一项未公开说明的更改:禁用了循环缓冲区(Loop Buffer)功能。这一变化引发了业界和用户的广泛关注。 循环缓冲区作为CPU前端的一个

单片机中的几种环形缓冲区的分析和实现

单片机中的几种环形缓冲区的分析和实现一、简介环形缓冲区(RingBuffer)是一种高效的使用内存的方法,它将一段固定长度的内存看成一个环形结构,用于存储数据,能够避免使用动态申请内存导致的内存碎片

esp32-s3 uvc摄像头缓冲区溢出是什么原因呢?

板子是esp32-s3 n8r8

使用的是ESP IDF VSCode 扩展版本 v1.8.0

遇到的问题是,在改变分辨率时候(增大or减小)都会遇到提示缓冲区溢出的情况,我尝试过增大缓冲区的内存分配,然而问题还是没有得到解决。

请问这是什么原因呢

发表于 07-19 07:35

ESP8266是否可以添加AT命令并使接收缓冲区大小可调?

是否可以添加 AT 命令并使接收缓冲区大小可调?

在Arduino上,我总是丢弃数据字节,而arduino硬件串行只有64字节的缓冲区,看起来ESP8266有256个字节。

发表于 07-17 07:36

ESP8266有双缓冲区吗?

我想实时传输一些信号的测量数据。信号的采样周期为 1 ms。我想每 500 毫秒发送 2048 字节(一个数据包)。ESP8266有双缓冲区(2x 2048字节)吗?其想法是计数填充一个缓冲区(周期

发表于 07-16 07:29

创建DMA通道时,能否将DMA缓冲区的大小指定为8字节,并将DMA缓冲区的编号指定为1?

创建 DMA 通道时,能否将 DMA 缓冲区的大小指定为 8 字节,并将 DMA 缓冲区的编号指定为 1?

发表于 05-31 07:46

stm32野火开发板上做USB通信,PC端USB的缓冲区和串口缓冲区的大小是多少?

ADC采集的波形还原,也就是画图。

我就不明白,安装的驱动作用是?修改了PID和VID。

还有PC端的USB作用不是太明白?是一下那种情况:

1、stm32端传过来的数据根本没有经过USB的缓冲区,而是

发表于 05-17 14:02

实现稳健的微控制器到FPGA SPI接口: 双缓冲区!

在介绍双缓冲器之前,我们将简要探讨Verilog 脉宽调制器 (PWM) 的工作原理。这一点很重要,因为双缓冲区最好被看作是硬件模块 (如 PWM) 的可寻址接口。

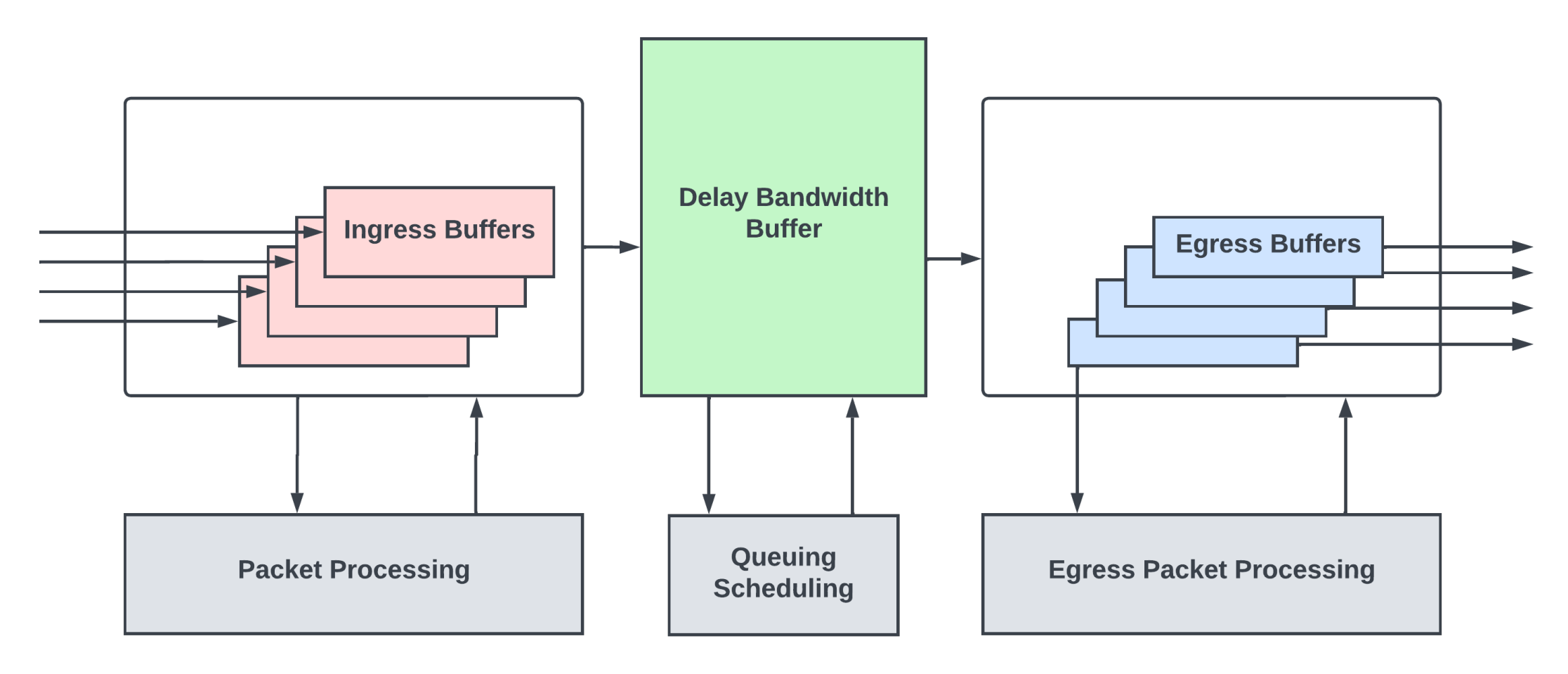

交换机与路由器缓冲区:寻找完美大小

*本文系SDNLAB编译自瞻博网络技术专家兼高级工程总监Sharada Yeluri领英 在路由器和交换机中,缓冲区至关重要,可以防止网络拥塞期间的数据丢失。缓冲区到底要多大?这个问题在

交换芯片缓冲区大小是什么

交换芯片缓冲区大小并不一定是固定的。缓冲区的设计和实现会根据芯片的具体型号、规格以及应用场景的不同而有所差异。一些交换芯片可能具有固定大小的缓冲区,以满足特定的性能需求或成本限制。然而,随着技术

什么是缓冲区?有什么作用

什么是缓冲区?有什么作用

评论