并非所有放大器设计都是平等的,在使用高速放大器进行设计时,熟悉常见规格并理解某些概念非常重要。在本文中,高速放大器是指增益带宽积 (GBW) 大于或等于 50 MHz 的运算放大器 (op amps),但这些概念也适用于低速设备。以下是设计人员在使用高速放大器时遇到的一些常见问题。

问:为什么有些高速运算放大器有最小增益规格?

答:去补偿运算放大器具有闭环最小增益稳定规范,但在相同的电流消耗下提供更宽的 GBW 和更低的噪声 - 与单位增益稳定的同类产品一样。

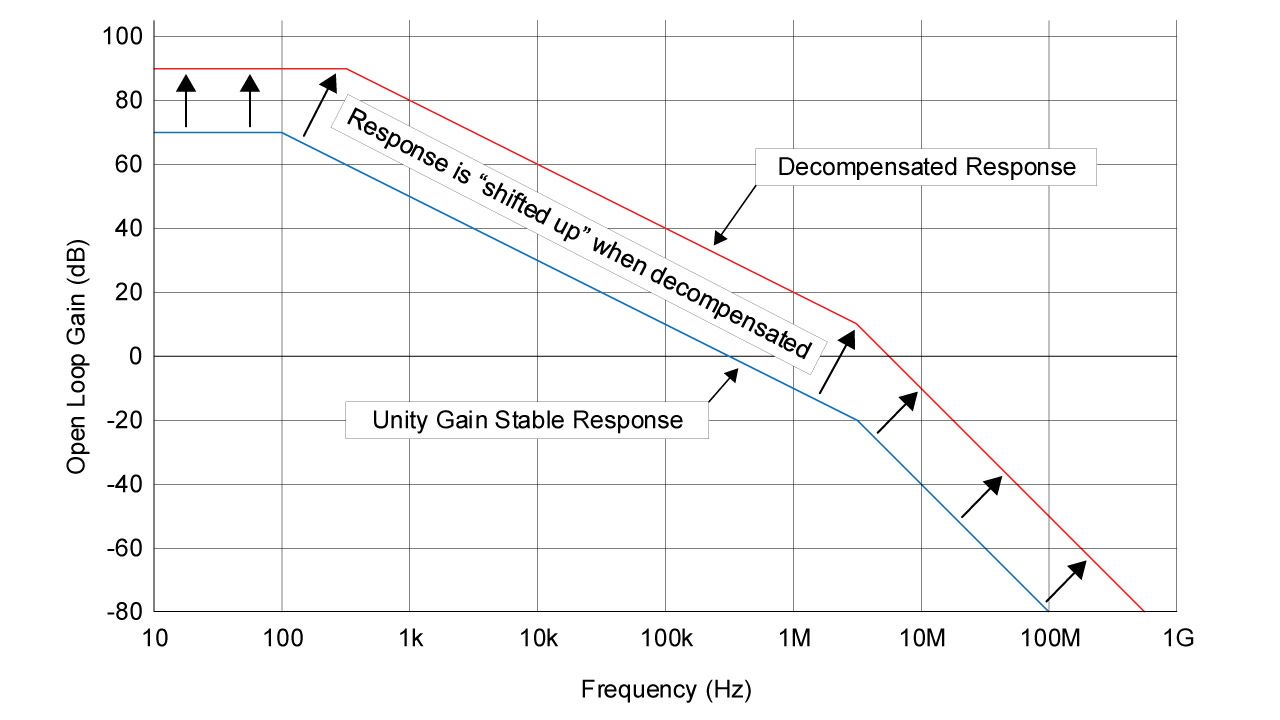

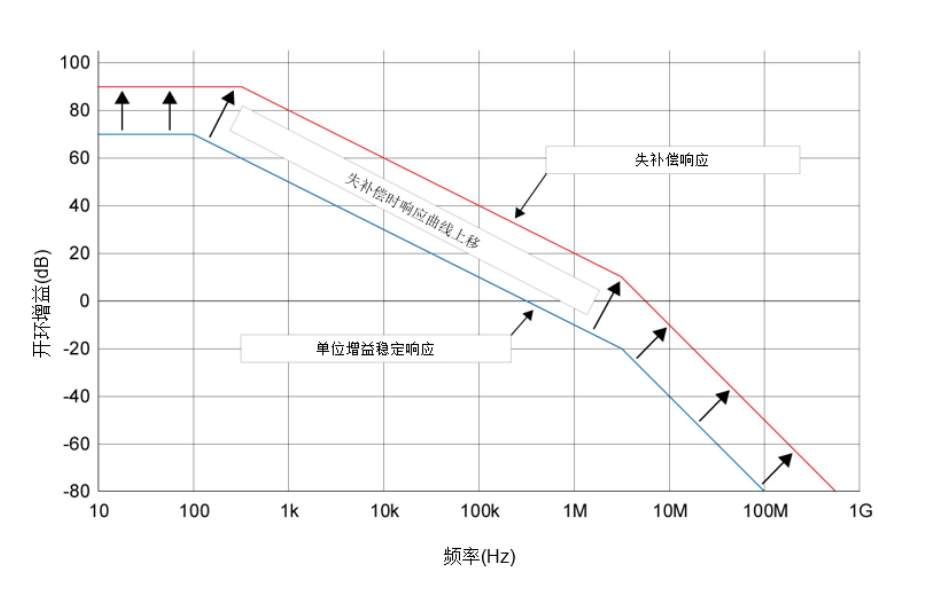

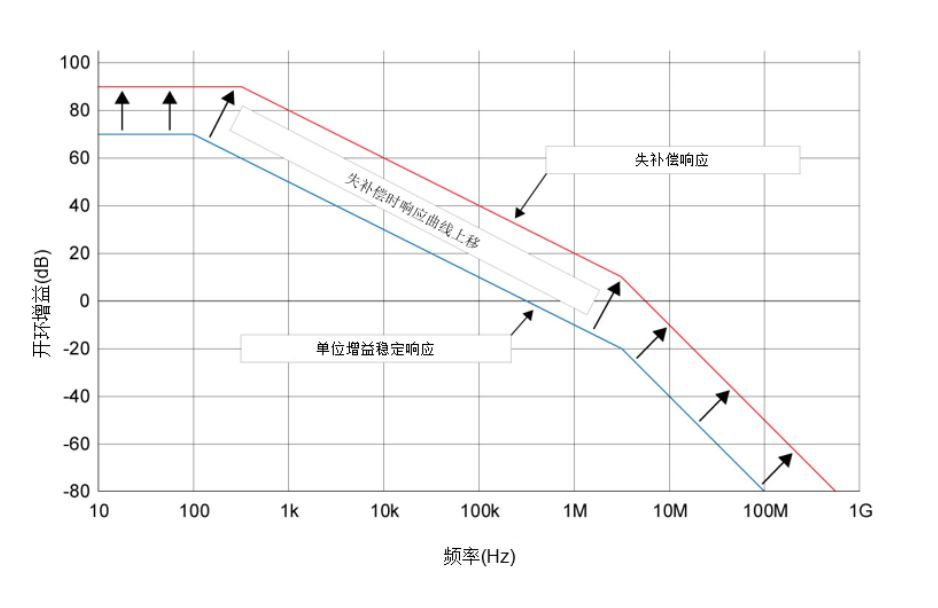

“去补偿”仅仅意味着在 Aol(开环增益)响应曲线中放置了一个高于 0 dB 的第二个极点。第二个极点也决定了确保放大器稳定性所需的最小增益。想象一下 Aol 曲线“上移”,如图 1 所示。增加的 Aol 会导致更宽的带宽。

图 1:失补偿放大器的开环增益响应曲线

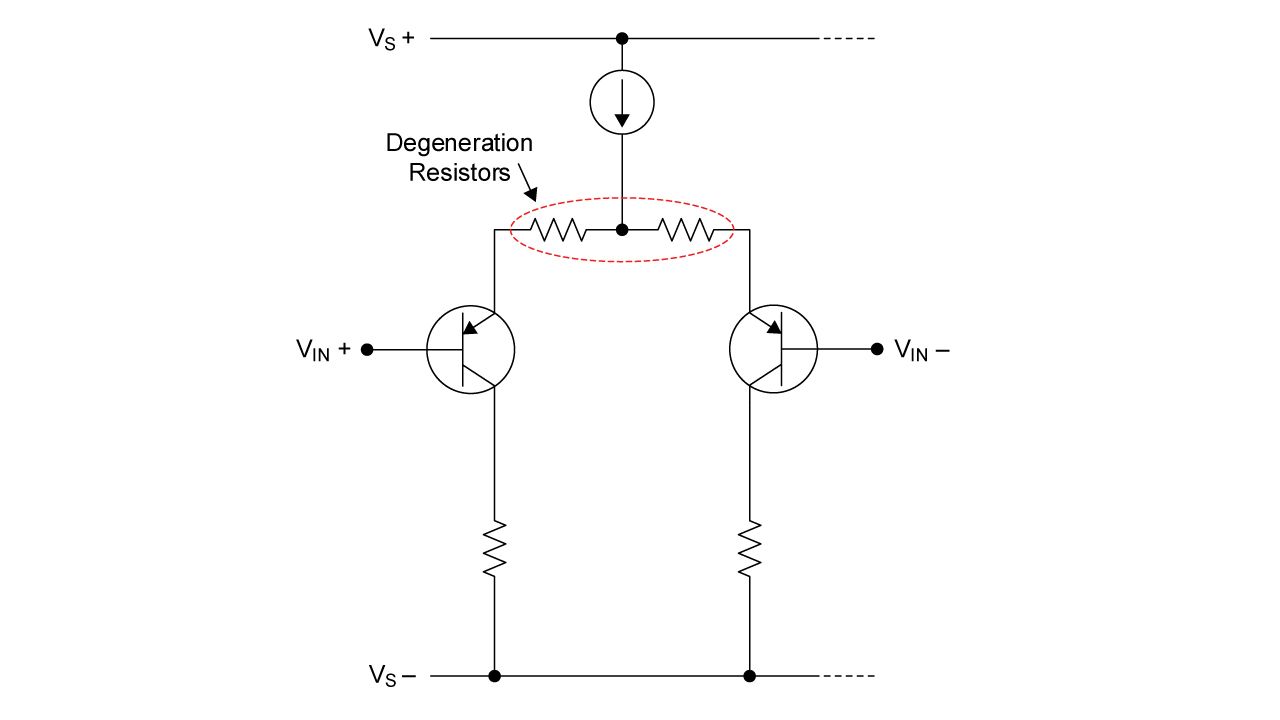

减小放大器输入对中的负反馈电阻器的尺寸会增加 Aol,如图 2 所示。更小的负反馈电阻器也有助于降低放大器噪声。

图 2:运算放大器中的退化电阻器

OPA858和OPA859分别是去补偿和单位增益稳定放大器的两个示例。对于相同的电流消耗,OPA858 具有更宽的带宽和更低的噪声,如表 1 所示。

|

|

OPA858 (失代偿) |

OPA859 (单位增益稳定) |

|

静态电流 ( IQ ) |

20.5 mA |

20.5 mA |

|

增益带宽 (GBW) |

5,500 兆赫 |

900兆赫 |

|

电压噪声 (V n ) |

2.5nV/√Hz |

3.3nV/√Hz |

|

转换率 |

2,000 伏/微秒 |

1,150 伏/微秒 |

|

最小增益 (Acl) |

7V/V |

1V/V |

表 1:去补偿和单位增益稳定放大器的比较

除了增加带宽和降低噪声外,去补偿架构还实现了更高的压摆率。总体而言,最小增益规范提供了性能权衡,如果您可以放弃单位增益并满足最小增益要求,您可以利用它。可以轻松满足最小增益规范的应用示例包括测量分流电阻器两端电压的电流检测电路、信号链中的增益级和跨阻电路。

问:什么是电流反馈放大器?

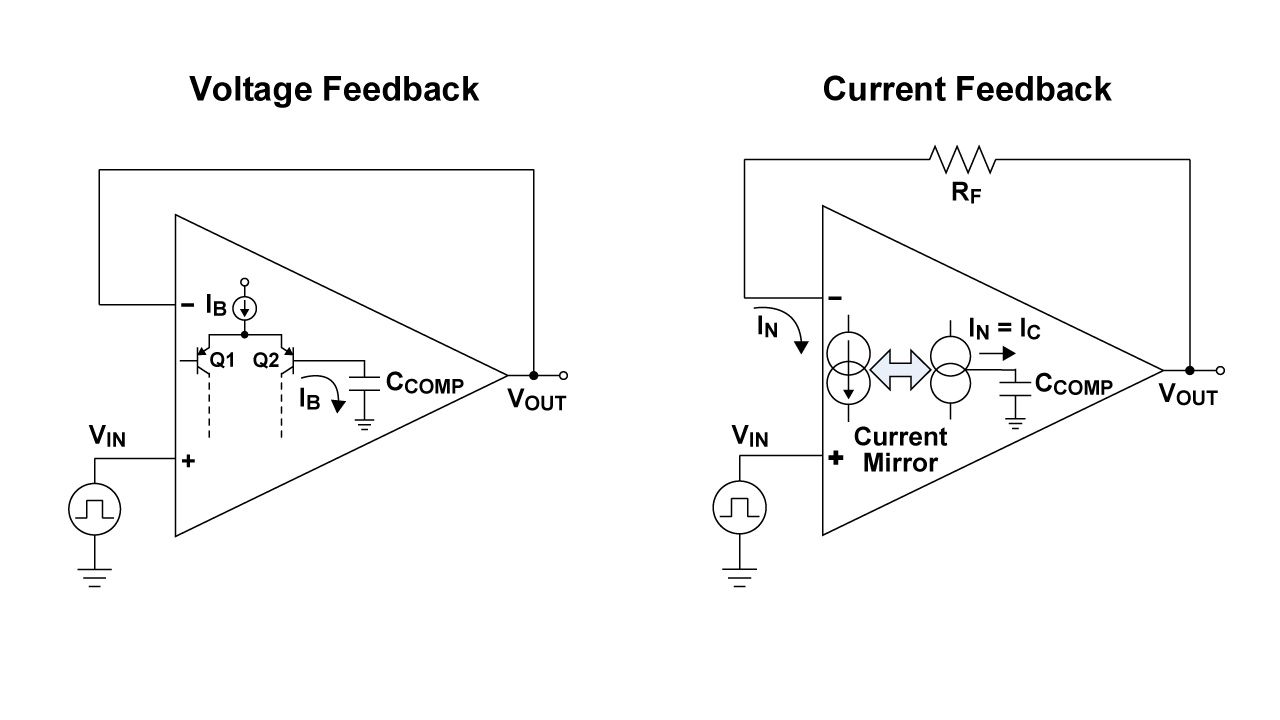

答:电流反馈放大器是一种运算放大器,可将输出信号的一部分作为电流反馈以控制放大器。电流反馈放大器不同于电压反馈放大器,后者依赖于电压形式的反馈。大多数设计人员都熟悉电压反馈架构,因为它们在大多数电子课程中更为常见和强调。

图 3 提供了电压和电流反馈放大器架构的基本输入级比较,其中电压反馈放大器被建模为压控电压源,电流反馈放大器被建模为电流控制电压源。

图 3 :比较电压和电流反馈运算放大器架构

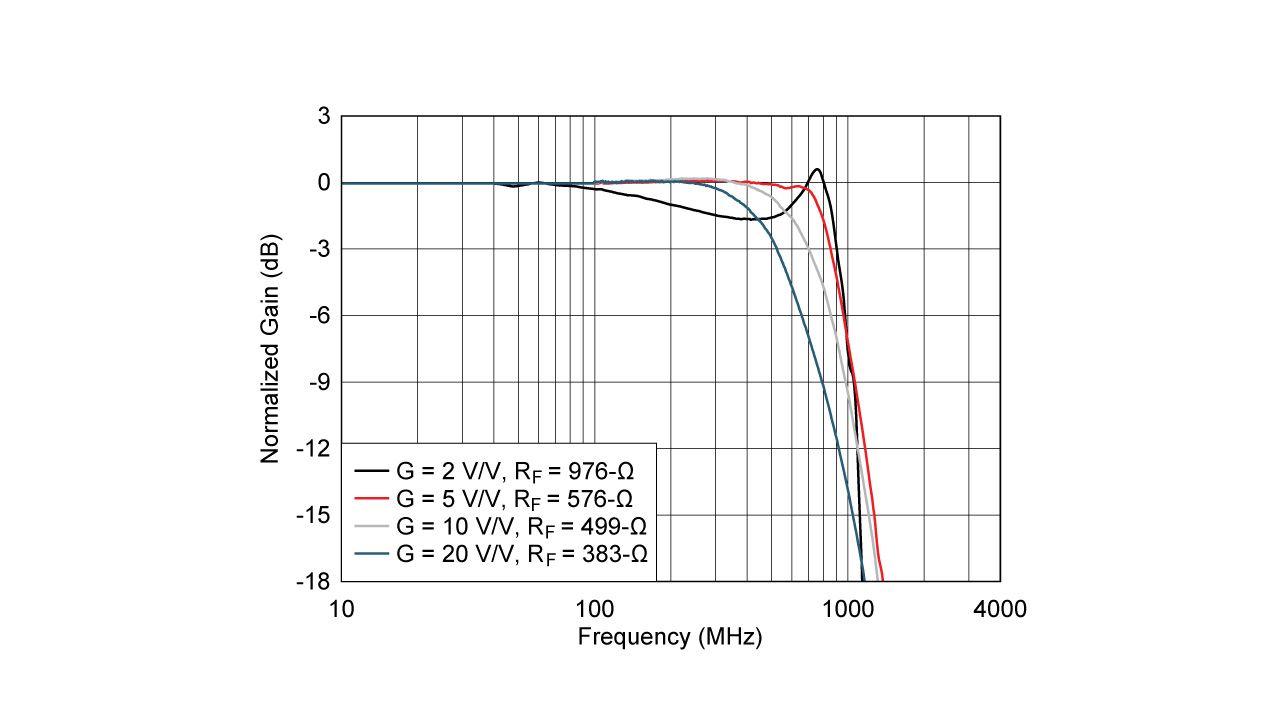

两种架构仍然用作负反馈电路中的误差放大器,但它们所需的反馈类型有所不同。例如,您可以在反相和同相增益配置中使用任一放大器类型。当前反馈架构的一个明显优势是带宽不依赖于增益。然而,在电压反馈架构中,随着增益的增加,带宽会减小,如公式 1 所示:

在电流反馈架构中,无论增益如何,带宽都几乎保持不变,如图 4 所示。该图出现在THS3491数据表中。

图 4 :电流反馈运算放大器的增益和带宽关系

表 2 比较了电压和电流反馈放大器之间的一些主要区别。

|

|

电压反馈放大器 |

电流反馈放大器 |

|

带宽 |

带宽随增益而变化 |

几乎恒定的带宽超过增益 |

|

直流精度 |

好的 |

贫穷的 |

|

输出摆幅 |

许多轨到轨输出选项 |

输出需要更大的净空 |

|

失真 |

更好的低频失真 |

更好的高频失真 |

|

转换率 |

压摆率有限 |

非常高的压摆率有助于实现高全功率带宽 |

|

获得稳定性 |

对失补偿放大器的最小稳定增益的限制 |

如果反馈跨阻保持恒定,则增益稳定 |

|

噪音 |

低输入参考电压和电流噪声 |

更高的输入参考电流噪声(不等于反相和同相输入) |

|

典型应用 |

需要直流精度的应用 面向脉冲的应用 跨阻应用 |

数模转换器接口 输出驱动器 高速 ADC 接口 Sallen-Key 过滤器 |

表2:比较电压反馈和电流反馈放大器应用

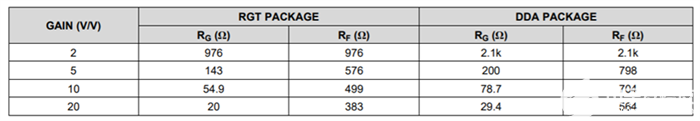

请注意,电流反馈放大器并不意味着在反馈路径中没有电阻的情况下运行。电流反馈放大器数据表将建议 R F的指定值;这些值很重要,因为 R F的值决定了放大器的补偿,即使在单位增益中也是如此。与图 4 一样,表 3 来自THS3491数据表。

表3: THS3491 数据表中推荐的 R F值示例

有关这两种架构之间差异的更多详细信息,请查看了解电压反馈和电流反馈放大器。您还可以通过观看TI 精密实验室在线培训视频了解有关当前反馈架构的更多信息。

问:为什么我的高速放大器放在面包板上时会振荡?

答:一般来说,很可能是封装引线的电感以及面包板的电容和电感导致您的高速放大器发生振荡。同样,在使用高速运算放大器进行设计时,尽量减少印刷电路板 (PCB) 上的电容和电感也很重要。即使是高速放大器 GBW 频谱的低端设备,如 50-MHz OPA607,也需要这些类型的板级设计考虑因素。

以下是一些可以优化高速布局设计的方法:

- 最小化走线长度。最小化走线长度可减少额外的电容和电感。

- 使用坚固的接地层。对于高速设计,实心接地平面通常比散列平面更好。

- 剪掉信号走线下的接地层。移除器件输入和输出下方的接地层金属有助于减少敏感节点上的寄生电容。

- 尽量减少信号路径上的过孔。过孔会增加电感,并可能导致频率高于 100 MHz 的信号保真度问题。为降低信号保真度,请将关键信号路由到与放大器相同的层上,以消除任何过孔。

- 优化返回电流路径。信号走线布局设计应尽量减少整体信号环路面积,从而最大限度地减少电感。

- 正确放置和布线旁路电容器。将旁路电容器尽可能靠近电路板同一层的放大器放置。使用更宽的走线和过孔布线到旁路电容器,然后到放大器——而不是在电容器和放大器之间。

- 正确放置电阻。将增益设置、反馈和串联输出电阻器放置在靠近器件引脚的位置,以最大限度地减少电路板寄生效应。

在评估高速运算放大器的性能时,最好使用针对特定器件的指定评估模块。这些电路板展示了良好的高速电路板布局设计,并使用 SMA 连接器来保持高保真和阻抗控制的信号路径。有关高速电路板布局实践的更多详细信息,您可以阅读高速 PCB 布局技术。

总体而言,高速运算放大器的运行与低速运算放大器非常相似。只需考虑一些设计细微差别,您就可以利用它们为您的系统提供的所有速度和性能优势。这些问题中哪一个与您最相关?在下面发表评论。

审核编辑:符乾江

-

电阻器

+关注

关注

21文章

3779浏览量

62105 -

运算放大器

+关注

关注

215文章

4915浏览量

172791 -

高速放大器

+关注

关注

0文章

13浏览量

7590

发布评论请先 登录

相关推荐

使用高速放大器进行设计时的三个常见问题

使用高速放大器进行设计时的三个常见问题

评论