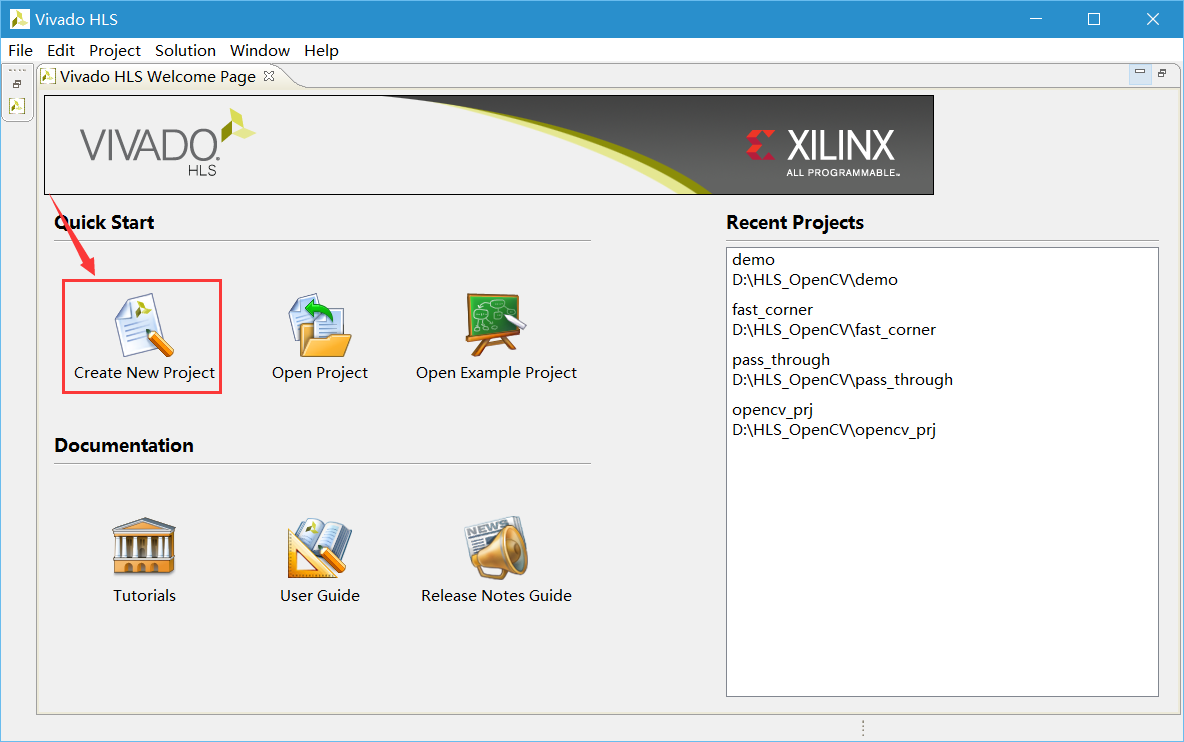

先从运行一个创建一个项目开始吧。

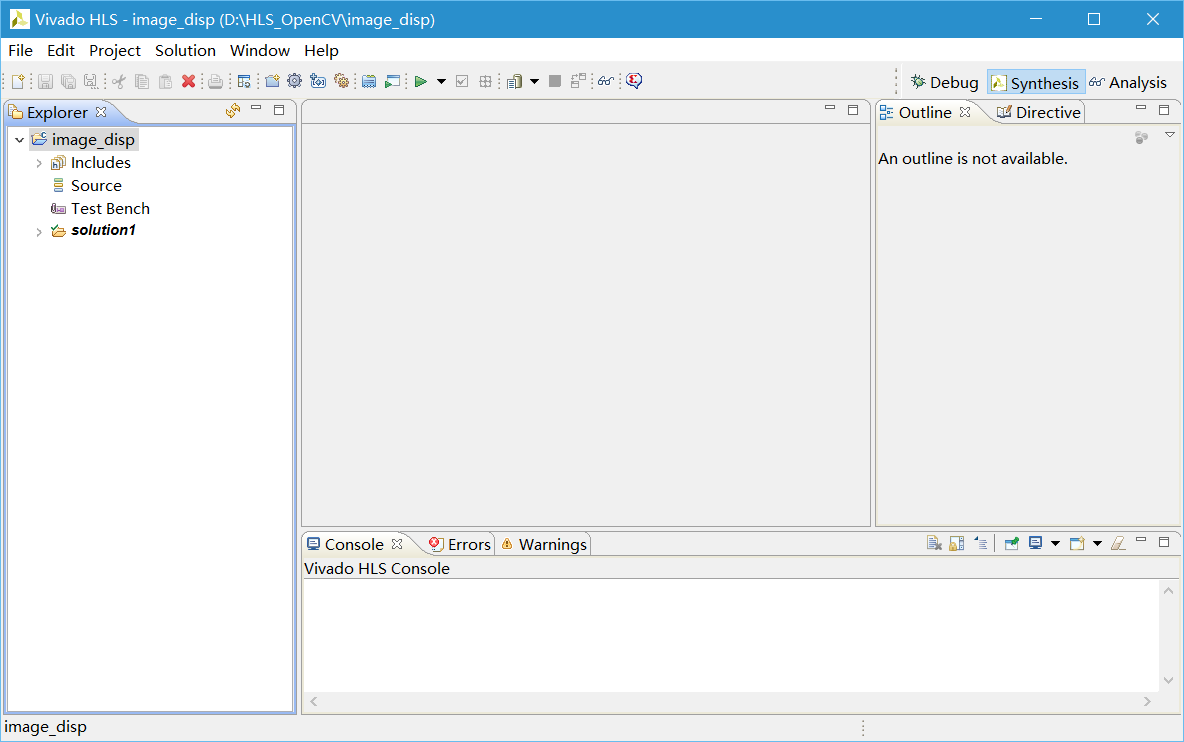

首先打开Vivado设计套件Vivado HLS 2015.4;

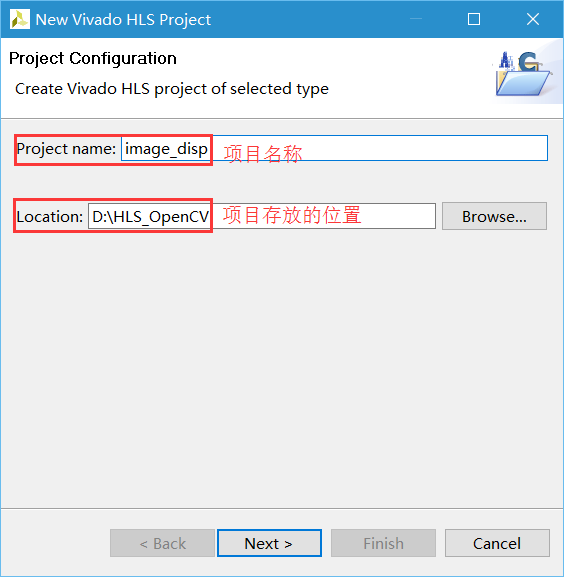

输入项目的名称和存放的位置;

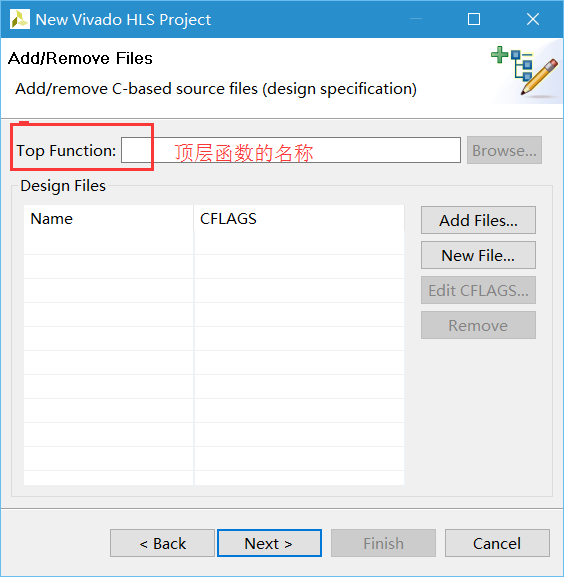

点击下一步,输入设计顶层函数的名称,接着下一步;

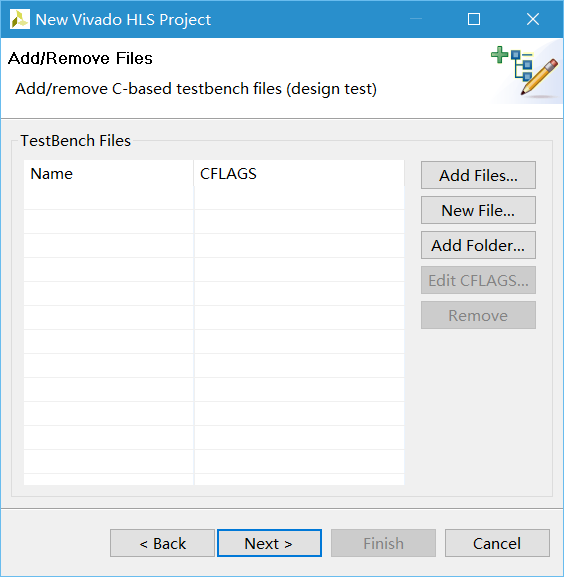

暂时不需要填写,直接下一步;

解决方案的名字默认 (solution1)就好, 时钟周期根据需要自己设,这里我设(10 ns), 时钟的不确定性一般为12.5%,接着选择器件,最后“finish”。

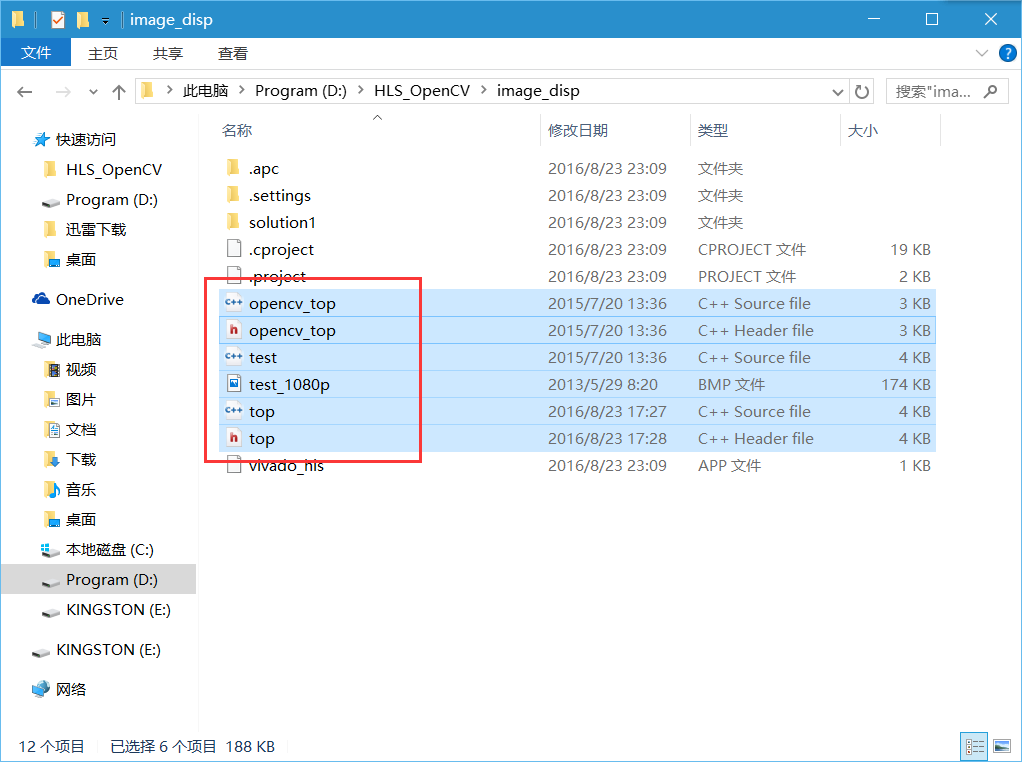

将该例程的设计文件和testbench全部复制到刚才创建的项目目录下:

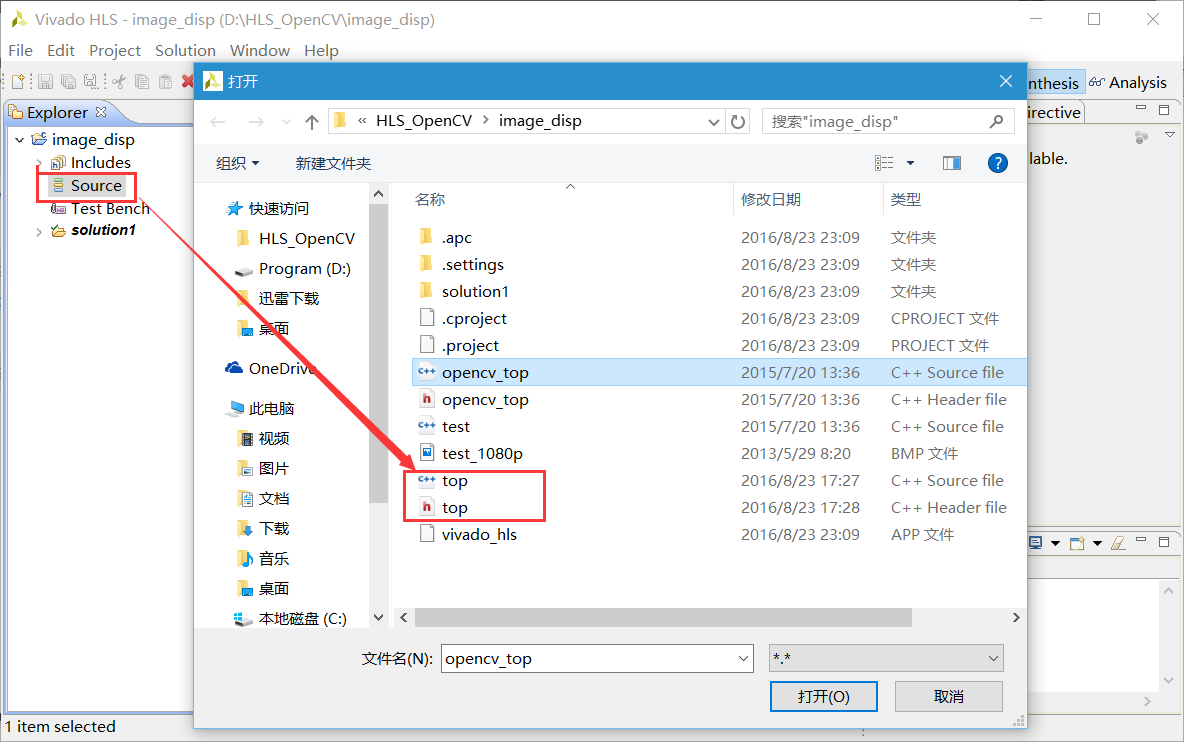

在设计资源窗口右击“Source”,添加设计文件;

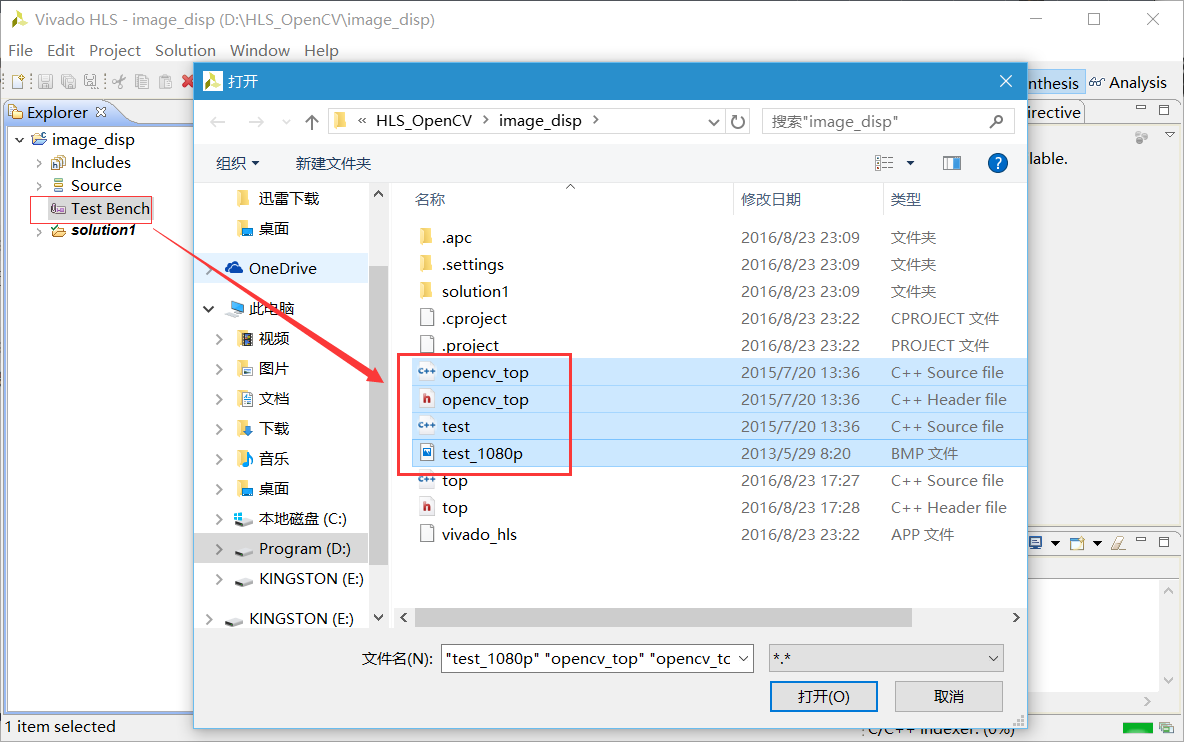

再接着右击“Test Bench”,添加文件;

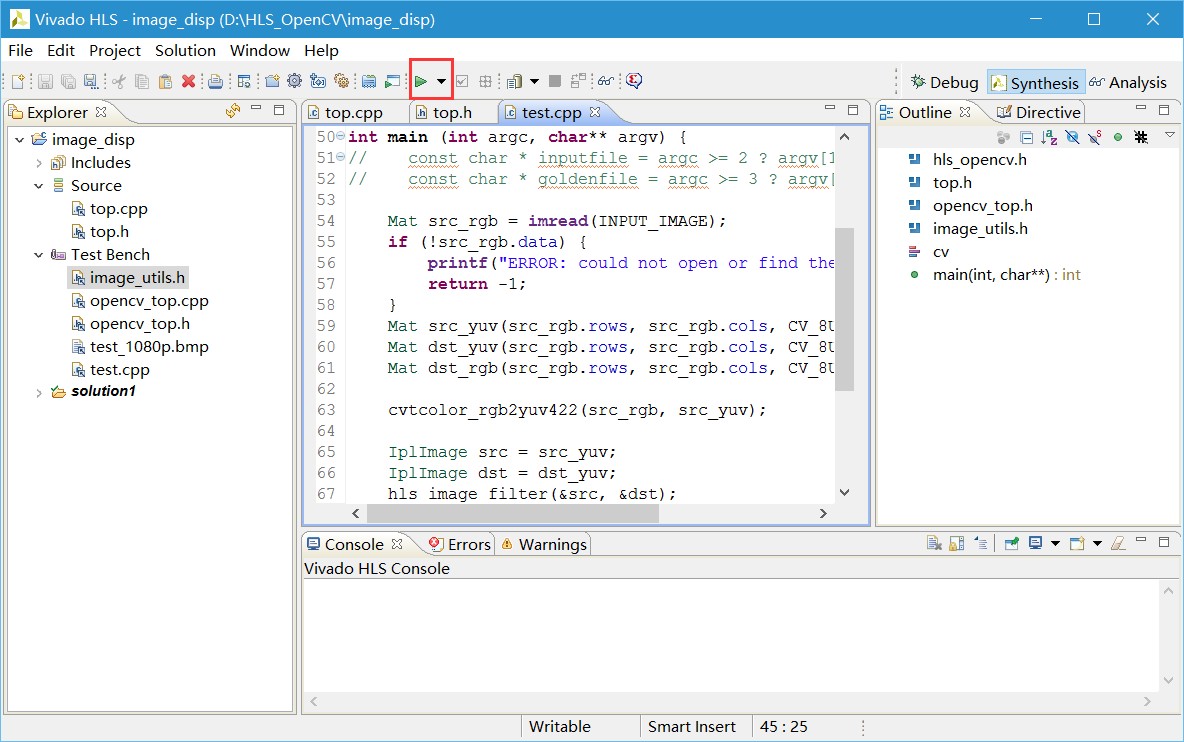

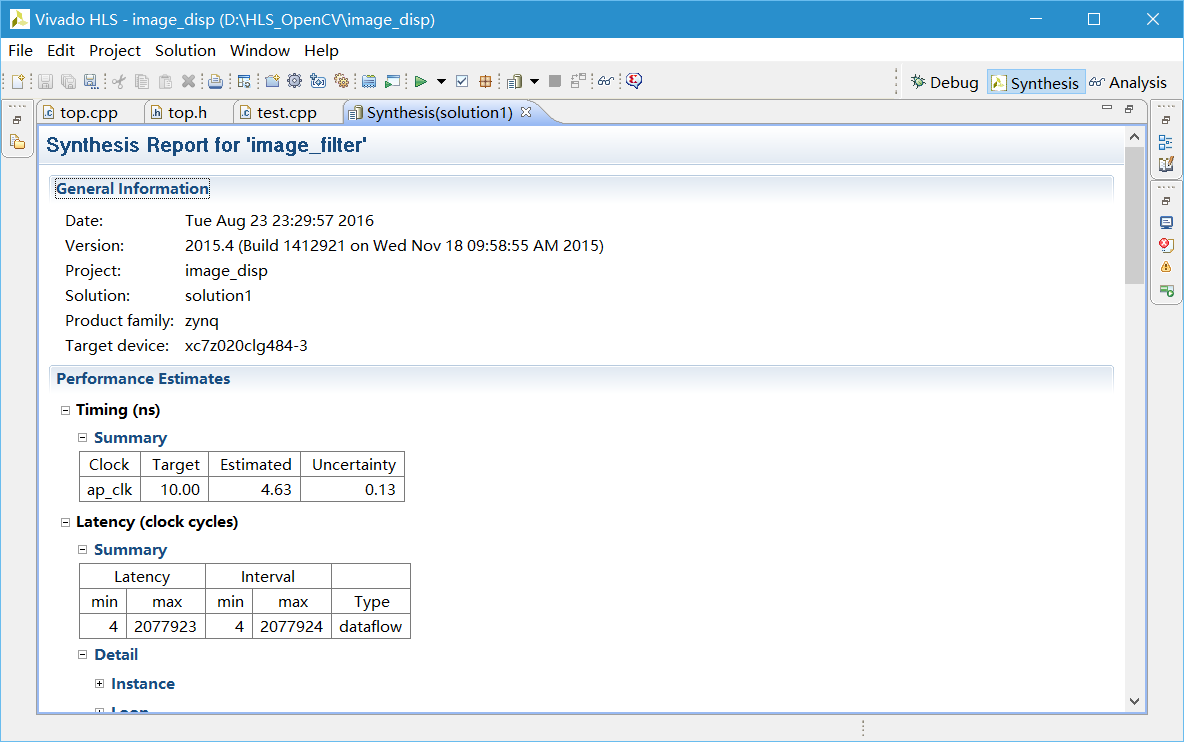

至此,项目建设完成。接着进行综合仿真,验证设计。 点击“Run C Snthry”。

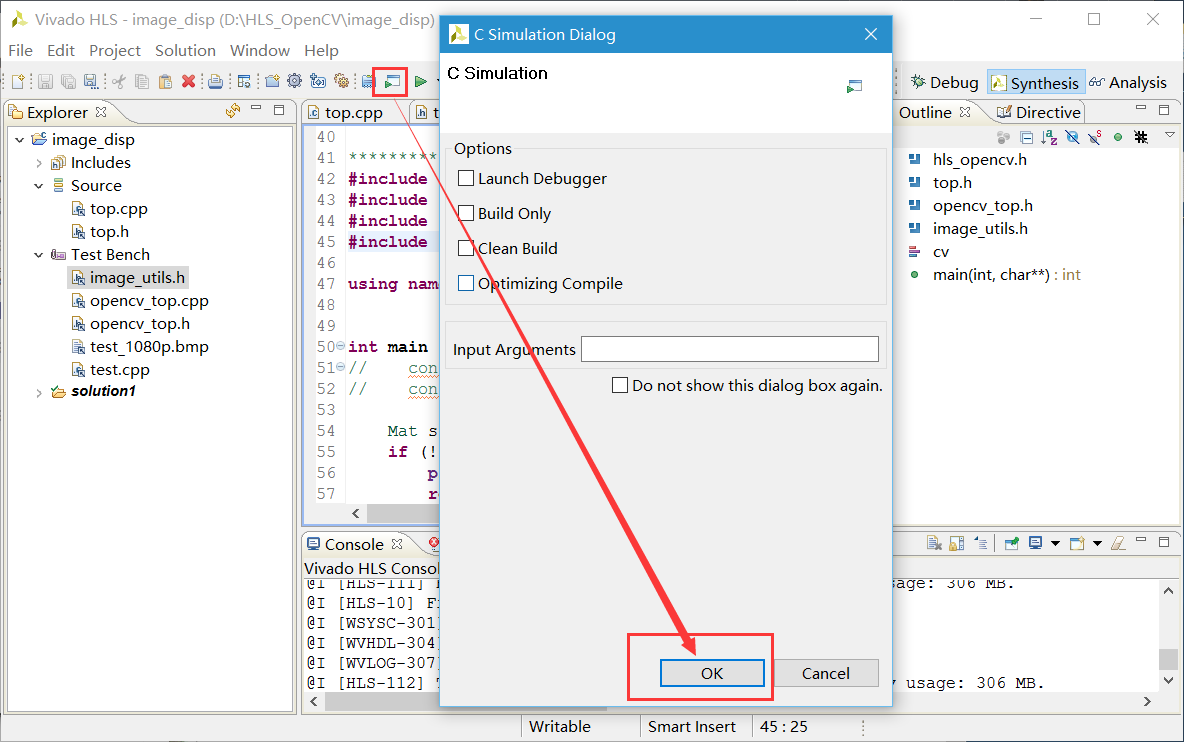

点击“Run C Simulation”,接着点击“OK”;

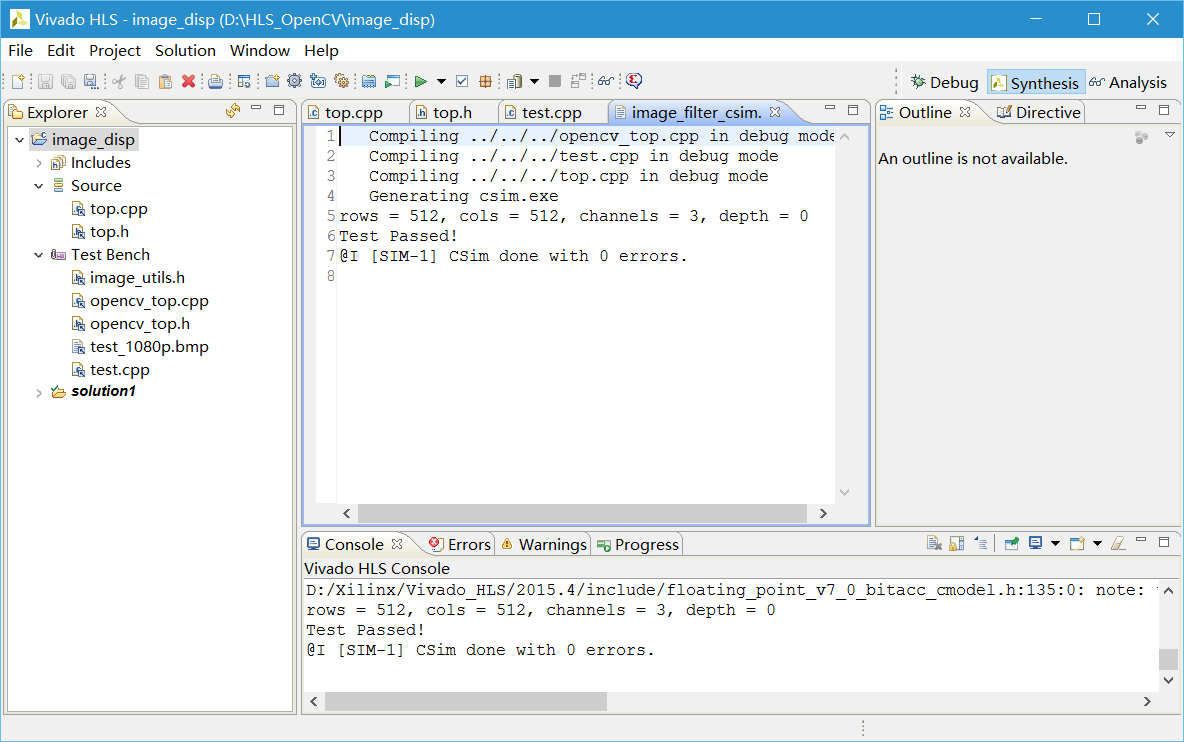

至此,此项目在没有硬件调试的前提下算是成功运行了。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

HDL

+关注

关注

8文章

327浏览量

47407 -

模型

+关注

关注

1文章

3255浏览量

48897 -

Vivado

+关注

关注

19文章

812浏览量

66631

发布评论请先 登录

相关推荐

从Level1 Model到Level3 Modle来感受器件模型是如何开发的

本文从Level1 model到Level3 model的Ids电流公式的发展来感受Compact器件模型是如何开发的。 MOS技术扩展到纳米尺寸,带来了电路模拟器中器件

助力AIoT应用:在米尔FPGA开发板上实现Tiny YOLO V4

Darknet 上训练的截图

四、 通过 Vivado HLS 为 FPGA 准备模型要将模型部署到 FPGA,需要将神经网络操作转换为硬

发表于 12-06 17:18

Vivado使用小技巧

有时我们对时序约束进行了一些调整,希望能够快速看到对应的时序报告,而又不希望重新布局布线。这时,我们可以打开布线后的dcp,直接在Vivado Tcl Console里输入更新后的时序约束。如果调整

优化 FPGA HLS 设计

优化 FPGA HLS 设计

用工具用 C 生成 RTL 的代码基本不可读。以下是如何在不更改任何 RTL 的情况下提高设计性能。

介绍

高级设计能够以简洁的方式捕获设计,从而

发表于 08-16 19:56

一种在HLS中插入HDL代码的方式

很多人都比较反感用C/C++开发(HLS)FPGA,大家第一拒绝的理由就是耗费资源太多。但是HLS也有自己的优点,除了快速构建算法外,还有一个就是接口的生成,尤其对于AXI类接口,按照

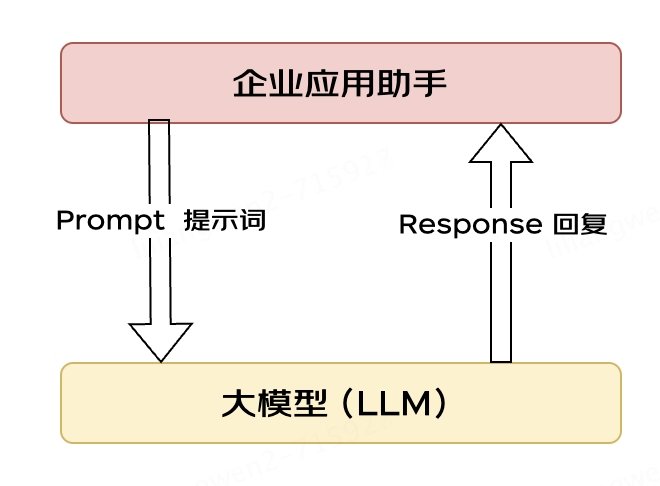

大模型应用之路:从提示词到通用人工智能(AGI)

大模型在人工智能领域的应用正迅速扩展,从最初的提示词(Prompt)工程到追求通用人工智能(AGI)的宏伟目标,这一旅程充满了挑战与创新。本文将探索大模型在实际应用中的进展,以及它们如

FPGA设计中 Verilog HDL实现基本的图像滤波处理仿真

今天给大侠带来FPGA设计中用Verilog HDL实现基本的图像滤波处理仿真,话不多说,上货。

1、用matlab代码,准备好把图片转化成Vivado Simulator识别的格式,即每行一

发表于 05-20 16:44

简谈Xilinx Zynq-7000嵌入式系统设计与实现

、IO及其他外设、用于工业控制领域如嵌入式应用。

AP SoC的诞生背景:

在全可编程平台设计阶段,设计已经从传统上以硬件描述语言HDL为中心的硬件逻辑设计,转换到以C语言为代

发表于 05-08 16:23

Verilog到VHDL转换的经验与技巧总结

Verilog与VHDL语法是互通且相互对应的,如何查看二者对同一硬件结构的描述,可以借助EDA工具,如Vivado,打开Vivado后它里面的语言模板后,也可以对比查看Verilog和VHDL之间的差异。

Vivado 使用Simulink设计FIR滤波器

小于通带内抖动值0.03db。

通过将输入信号改为脉冲信号,脉冲宽度为1个周期,此时可观测到此fir滤波器的冲击响应。经过以上步骤,基本验证此滤波器的设计能够达到需求。

5. 将模型导入到

发表于 04-17 17:29

Vivado编译常见错误与关键警告梳理与解析

Xilinx Vivado开发环境编译HDL时,对时钟信号设置了编译规则,如果时钟由于硬件设计原因分配到了普通IO上,而非_SRCC或者_MRCC专用时钟管脚上时,编译器就会提示错误。

简谈Xilinx Zynq-7000嵌入式系统设计与实现

应用。

AP SoC的诞生背景:

在全可编程平台设计阶段,设计已经从传统上以硬件描述语言HDL为中心的硬件逻辑设计,转换到以C语言为代表的软件为中心的功能

发表于 04-10 16:00

# FPGA 编程如何工作?

Vivado™ HLS 编译器提供了一个与专用和标准处理器共享关键技术的编程环境,可优化基于 C 的程序。

=#6。= TensorFlow 和 PyTorch 等 AI 平台

工程师使用Pytorch 或

发表于 03-30 11:50

使用CUBEAI部署tflite模型到STM32F0中,模型创建失败怎么解决?

看到CUBE_AI已经支持到STM32F0系列芯片,就想拿来入门嵌入式AI。

生成的模型很小,是可以部署到F0上的,但是一直无法创建成功。

查阅CUBE AI文档说在调用create函数前,要启用

发表于 03-15 08:10

Vivado HLS从HDL到模型和C的描述

Vivado HLS从HDL到模型和C的描述

评论