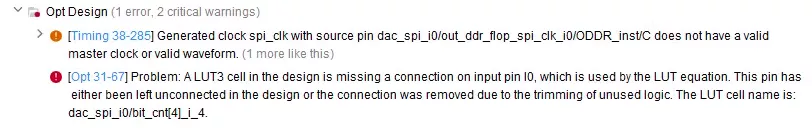

在Vivado中,可能由于某些逻辑输入悬空而导致Implementation的opt_design时会错,比如:

报的错误是dac_spi_i0/bit_cnt[4]_i_4的这个LUT有个输入悬空了,这个工程的逻辑比较简单,例化的嵌套也比较少,因此在schematic一层层找也很容易可以找到,但如果工程比较复杂,在很内部的一个LUT的输入悬空了,找起来就很费劲了。

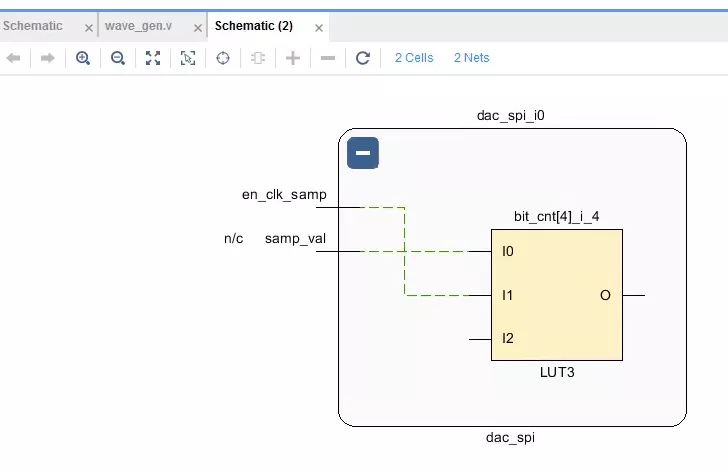

笔者碰到的问题是在vivado的axi-interconnect ip中报了这个错误,而且是ip内部套了好几层的地方,如果再一层层往下找就比较麻烦了,不过vivado提供了tcl指令可以帮我们快速找到这个LUT在schematic中的位置:

show_schematic [get_cells dac_spi_i0/bit_cnt[4]_i_4]

就会快速定位到schematic中的位置:

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

指令

+关注

关注

1文章

614浏览量

35913 -

逻辑

+关注

关注

2文章

834浏览量

29532 -

Vivado

+关注

关注

19文章

819浏览量

67162

发布评论请先 登录

相关推荐

Vivado FIR IP核实现

Xilinx的FIR IP核属于收费IP,但是不需要像 Quartus那样通过修改license文件来破解。如果是个人学习,现在网络上流传的license破解文件在破解Vivado的同时也破解

详解Object Detection Demo的移植

继上一篇移植了 Mediapipe 的 LLM Inference 后,这篇文章我们将继续探索 Object Detection Demo 的移植。

电脑相片云存储位置,如何快速找到电脑相片云存储位置

在数字化时代,传统的电脑已经无法满足我们对高效、便捷计算的需求。云电脑以其强大的功能和灵活的使用方式,成为了新时代的宠儿。今天就为大家介绍如何快速找到电脑相片云存储位置。 在现代办公和生活中

Vivado Design Suite用户指南:逻辑仿真

电子发烧友网站提供《Vivado Design Suite用户指南:逻辑仿真.pdf》资料免费下载

发表于 01-15 15:25

•0次下载

Vivado使用小技巧

有时我们对时序约束进行了一些调整,希望能够快速看到对应的时序报告,而又不希望重新布局布线。这时,我们可以打开布线后的dcp,直接在Vivado Tcl Console里输入更新后的时序约束。如果调整

TPA3118D2EVM Schematic中输出电感可用FB1812(贴片磁珠),贴片磁珠的参数规格型号和怎样选?

TPA3118D2EVM Schematic中输出电感可用FB1812(贴片磁珠),贴片磁珠的参数规格型号和怎样选

请高手或TI工程师帮忙指教

发表于 10-18 06:17

Vivado 使用Simulink设计FIR滤波器

。

使用vivado的System Generator可以在simulink下快速的通过matlab的强大设计功能设计滤波器。这里使用fdatool设计了一个15阶的FIR滤波器。

软件环境

发表于 04-17 17:29

Vivado怎么快速找到schematic中的object

Vivado怎么快速找到schematic中的object

评论