经典面试题:建立时间与保持时间

我曾背过这个答案N多遍,但是依然没有理解。

直到...

一、同步电路设计

同步电路系统设计将系统状态的变化与时钟信号同步,并通过这种理想化的方式降低电路设计难度。同步电路设计是FPGA设计的基础。

但是伴随着集成电路的微缩化和大规模化,同步式电路的一些问题也显现出来。有研究提出了基于异步电路实现FPGA的思路。这个后面再谈。

二、触发器

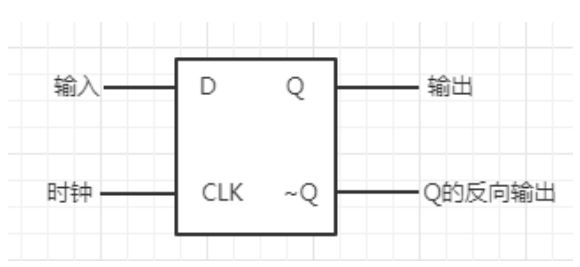

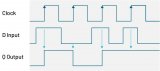

触发器(Flip Flip,FF)是一种只能存储1个二进制位(bit)的存储单元,可以用作时序逻辑电路的记忆元件。FPGA逻辑单元的D触发器(DFF)就是一种在时钟的上升沿将输入信号的变化传送至输出的边沿D触发器。DFF的符号和真值表如下图所示:

2.1 D触发器结构

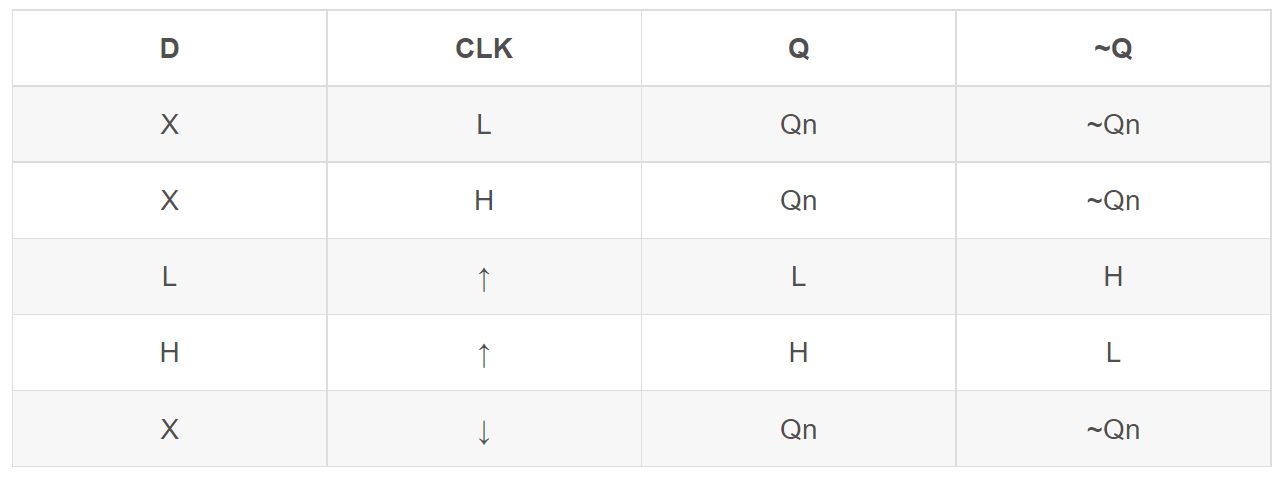

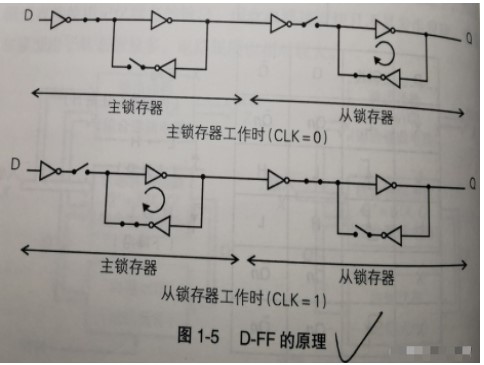

CMOS传输门构成的D边沿触发器电路如下图所示:

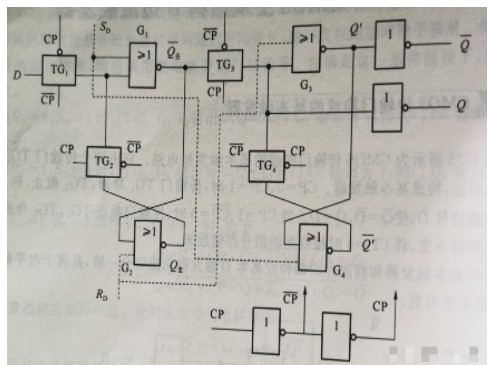

CMOS工艺下的D-FF结构如下图所示:

先由传输门和两个反相器组成一个循环电路(锁存器),再有前后两级锁存器按主从结构连接而成。这里的传输门起开关作用,随着CLK的状态切换开关。只看输出的话,前级锁存器的值会随着时钟输入的变化井然有序的传入后级锁存器。为了防止时钟信号变化时输入信号发生冒险,从而使输入数据稳定的进入前级锁存器,前级锁存器的时钟相位应与输入数据的电路时钟相位相反。

2.2 D触发器工作原理

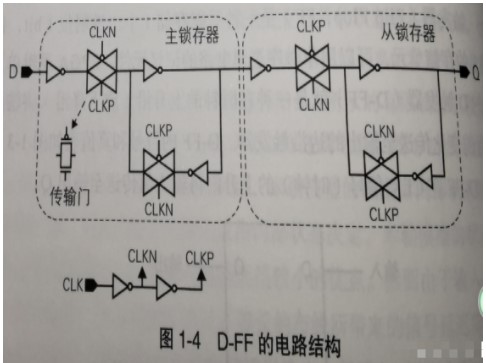

D-FF的工作原理,如下图所示:

当CLK=0时(主锁存器工作),位于前级的主锁存器将输入D的值保存进来,后级的从锁存器将维持上一个时钟周期的数据。由于此时前级与后级的反相器环路之间的传输门是关闭状态,所以前级的信号不会传到后级。

当CLK=1时(从锁存器工作),前级主锁存器的值将会传到后级,同时输入D的信号将会被隔离在外。此时如果前级反相器环路中的信号没有循环一圈以上,就会出现如下图所示的在0和1之间摇摆的中间电位,这就是所谓的亚稳态。

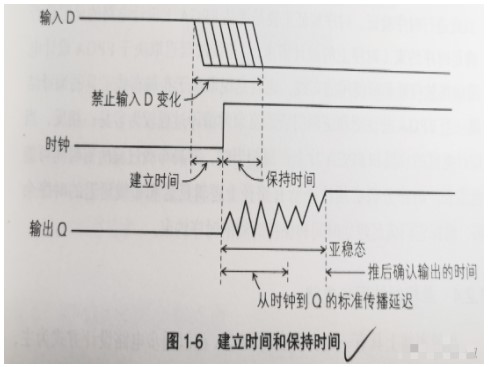

三、建立时间和保持时间

由于亚稳态时间比延迟时间长,在该阶段读取数据可能会引起错误,所以我们引入建立时间(setup time)来约束在时钟上升沿到来之前输入D保持稳定的时间。

当CLK=1时,如果输入D在传输门关闭之前就发生变化,那么本该在下一周期读取的数据就会提前进入锁存器,从而引起反相器环路振荡或产生亚稳态。因此在CLK=1之后也需要输入D维持一定的时间,我们称之为保持时间(hold time)约束。

审核编辑:汤梓红

-

FPGA

+关注

关注

1631文章

21806浏览量

606681 -

触发器

+关注

关注

14文章

2019浏览量

61397 -

同步电路

+关注

关注

1文章

60浏览量

13359

发布评论请先 登录

相关推荐

ADC采样保持过程的具体时间要如何确定?

DAC81408的建立时间为12uS,如何理解数据手册中的12uS建立时间这个参数呢?

DAC7811想要实现持续1us的100mA电流源,但DAC建立时间都有1us,如何解决?

请问如何确认dac7811的电压建立时间是否满足0.2us?

使用NTP,该如何同步时间?一文详解!

PGA281建立时间过长怎么解决?

求助,关于INA333波形建立时间的疑问求解

用混合信号示波器识别建立和保持时间违规

时间同步协议详解:从原理到应用的全方位解析

详解FPGA中建立时间与保持时间

详解FPGA中建立时间与保持时间

评论