一、7 系列FPGAs SelectIO 资源

SelectIO,就是I/O接口以及I/O逻辑的总称。《UG471--SelectIO》 篇可以分成3部分:第1部分介绍I/O的电气特性,第2部分介绍I/O逻辑资源,第3部分介绍高级的I/O逻辑资源(serializer/deserializer)。

说到I/O,必须先提到FPGA的BANK。在7系列的FPGA中,BANK分为HR(High-range)BANK和HP(High-performance) BANK。HP BANK只能支持小于等于1.8V电平标准的I/O信号,HR BANK则支持小于等于3.3V电平标准的I/O信号。HP BANK专为高速I/O信号设计,支持DCI(数控阻抗),而HR BANK则适合更大众化的所有I/O信号设计。下表列出了HP BANK 和HR BANK的特性。

无论是HR或者HP BNANK,每个BANK都包含50个I/O管脚,每个I/O管脚都可配置成输入、输出。每个BANK的首尾管脚只能作为单端I/O,其余48个I/O则可配置成24对差分I/O。

二、selectIO的逻辑资源

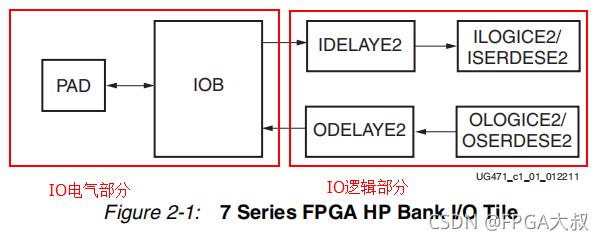

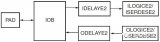

下图为HP BANK的IO 模块,HR BANK与之相比,没有输出延迟ODELAYE2;

I/O逻辑资源主要包含5部分:

2.1 ILOGIC

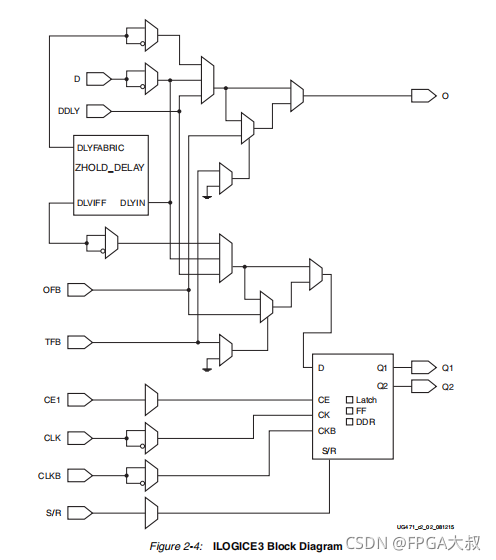

ILOGIC即输入信号处理逻辑,紧挨着IOB,外界的输入信号最先经过的就是ILOGIC。ILOGIC是由许多的数据选择器和一个IDDR(input Double Data Rate)触发器构成。该触发器既可以双沿捕获输入数据也可以拆分成普通单沿触发器。在HP BANK中,ILOGIC被称为ILOGICE2,在HR BANK中,ILOGIC被称为ILOGICE3。下图给出了ILOGICE3的示意图:

ILOGICE2与ILOGICE3的区别是:ILOGICE3包含了ZHOLD(Zero Hold) delay。

2.2 IDELAY

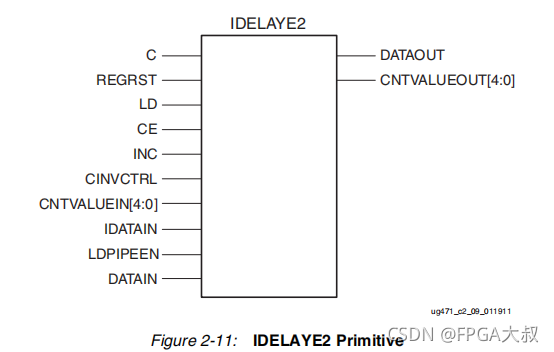

IDELAY被称为信号延迟模块,它的作用就是把信号延迟一段时间。对于一些需要对齐的输入信号来说,这至关重要。在7系列FPGA中,它被称为IDELAYE2。IDELAYE2可以将信号延迟0~31节,在这区间任意可调,并且在参考时钟为200M时,每节的延迟精度为78ps(1/(32×2×FREF),FREF为IDELAYCTRL的参考时钟)。下图为IDELAYE2例化框图。

IDELAY后文详细讲解。

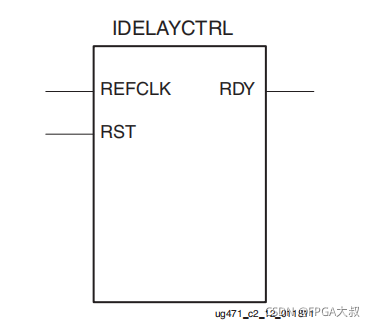

2.3 IDELAYCTRL

IDELAYCTRL其实是个辅助模块,这么说吧,只要使用了IDELAY或者ODELAY,IDELAYCTRL必须被使用,要不然就无法正常工作。因为IDELAY或者ODELAY的延迟精度是由IDELAYCTRL的输入时钟决定的,一般为200MHz。下图为IDELAYCTRL例化框图。

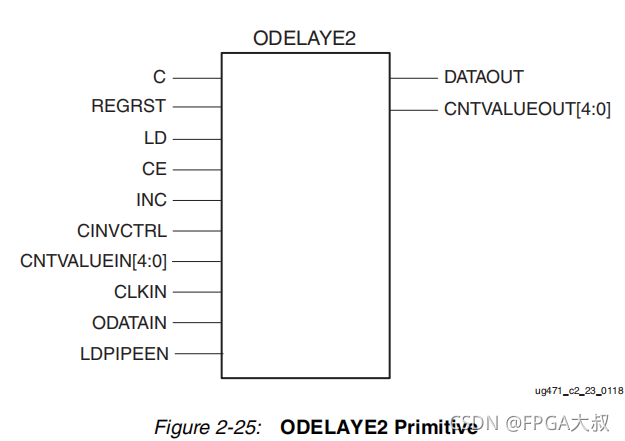

2.4 ODELAY

ODELAY和IDEALY的使用方式差不多,只不过ODELAY是用作输出信号的延迟。另外,HR BANK内没有ODELAY,HP BANK才有,被称为ODELAYE2。使用ODELAYE2时同样需要例化IDELAYCTRL。下图为ODELAYE2例化框图:

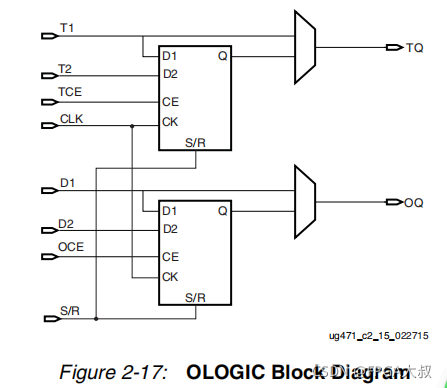

2.5 OLOGIC

LOGIC包括2个部分:一个用于配置输出路径。另外一个用于配置三态控制路径。输出路径和三态控制路径都可以独立配置成沿触发器、ODDR以及组合逻辑输出。

总的来说,I/O逻辑资源就是用来获取或者输出信号。对于一般的低速信号而言,I/O逻辑资源体现不出优势,用不用都不影响最终结果,但是对于高速信号而言,就必须使用I/O逻辑资源了,不能够正确使用它,整个FPGA逻辑代码完全无用。

三、IDELAYE2原语

使用IDELAYE2原语必须例化IDELAYCTRL原语

IDELAYCTRL IDELAYCTRL_inst (

.RDY(RDY), // 1-bit output: Ready output

.REFCLK(REFCLK), // 1-bit input: Reference clock input

.RST(RST) // 1-bit input: Active high reset input

);

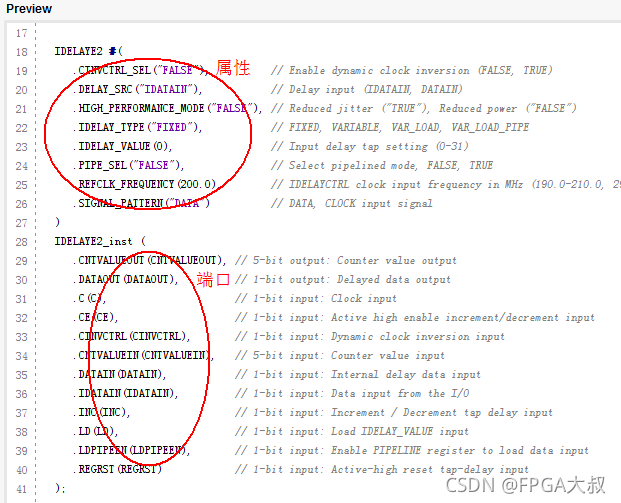

再看IDELAYE2原语:

3.1IDELAYE2属性

3.2IDELAYE2端口

3.2.1延迟控制

1. FIXED模式: 固定模式,延迟值为输入的VALUE

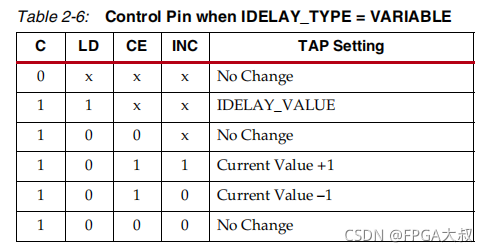

2. VARIABLE模式:由C,LD,CE,INC 共同控制,如下图所示:

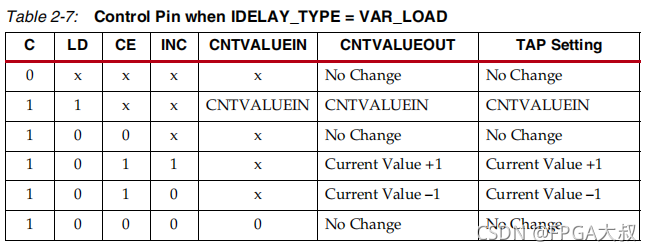

3. VAR_LOAD模式:由C,LD,CE,INC,CNTVALUEIN共同控制

3.3时序图

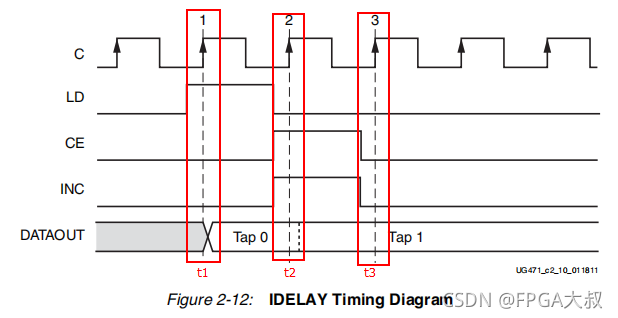

我们再看一个VARIABLE模式,加载延时的时序图:

IDELAY属性如下:

IDELAY_TYPE = VARIABLE,

IDELAY_VALUE = 0,

DELAY_SRC = IDATAIN

时刻t1:

在C的上升沿,检测LD为高,加载IDELAY_VALUE,即输出延时为tap0;

时刻t2:

在C的上升沿,检测到CE &INC同时为高,由上文延时控制部分内容可知,延时为当前值+1,即输出延时为tap1;

时刻t3:

LD,CE,INC均为0,增加延时操作完成,输出延时保持tap1,直到下一次又检测到LD,CE,INC。

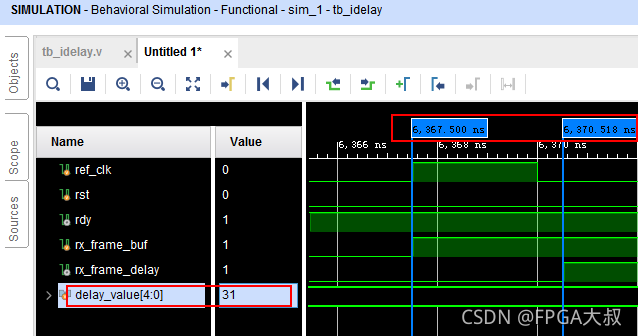

3.4仿真测试

Testbench:例化一个idelayctrl,再例化一个idelaye2(VAR_LOAD模式):

IDELAYCTRL IDELAYCTRL_inst (

.RDY(rdy), // 1-bit output: Ready output

.REFCLK(ref_clk),// 1-bit input: Reference clock input

.RST(rst) // 1-bit input: Active high reset input

);

IDELAYE2 #(

.CINVCTRL_SEL("FALSE"), // Enable dynamic clock inversion (FALSE, TRUE)

.DELAY_SRC("IDATAIN"), // Delay input (IDATAIN, DATAIN)

.HIGH_PERFORMANCE_MODE("FALSE"), // Reduced jitter ("TRUE"), Reduced power ("FALSE")

.IDELAY_TYPE("VAR_LOAD"), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE

.IDELAY_VALUE(0), // Input delay tap setting (0-31)

.PIPE_SEL("FALSE"), // Select pipelined mode, FALSE, TRUE

.REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz

.SIGNAL_PATTERN("DATA") // DATA, CLOCK input signal

)

IDELAYE2_inst_frame_delay (

.CNTVALUEOUT(cnt_delay_tap),// 5-bit output: Counter value output

.DATAOUT(rx_frame_delay), // 1-bit output: Delayed data output

.C(ref_clk), // 1-bit input: Clock input

.CE(1'b0), // 1-bit input: Active high enable increment/decrement input

.CINVCTRL(1'b0), // 1-bit input: Dynamic clock inversion input

.CNTVALUEIN(delay_value), // 5-bit input: Counter value input

.DATAIN(1'b0), // 1-bit input: Internal delay data input

.IDATAIN(rx_frame_buf), // 1-bit input: Data input from the I/O

.INC(1'b0), // 1-bit input: Increment / Decrement tap delay input

.LD(delay_load_en[12]), // 1-bit input: Load IDELAY_VALUE input

.LDPIPEEN(1'b0), // 1-bit input: Enable PIPELINE register to load data input

.REGRST(1'b0) // 1-bit input: Active-high reset tap-delay input

);

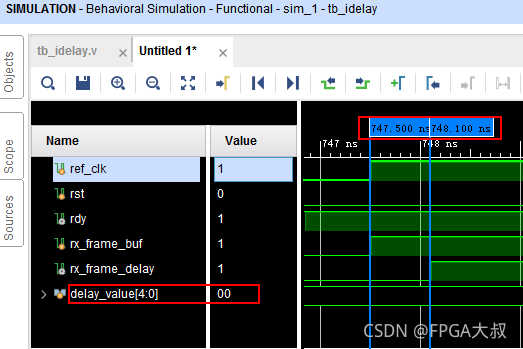

可以发现,只要过了idelay,就会增加0.6ns的延迟;

delay_value = 0;Tdelay=0.6ns;

仿真继续往下走,当tap=31时,Tdelay=3.018ns=31x78(ps) +0.6ns;

测试验证正确。

四、高级selectIO逻辑资源

为了方便使用I/O逻辑资源,Xilinx公司专门将几种模块集中起来,构成了功能强大的源语ISERDESE2和OSERDESE2:《UG471》翻译(2)ISERDESE2原语介绍

审核编辑:符乾江

-

Xilinx

+关注

关注

71文章

2173浏览量

122676 -

逻辑

+关注

关注

2文章

834浏览量

29537

发布评论请先 登录

相关推荐

AI助力实时翻译耳机

调试Xilinx Zynq + ADS58C48,ADC使用的是LVDS模式,ADC不能正常工作怎么解决?

UC3843BD1R2G安森美高性能电流模式PWM控制器-uc3843中文资料应用电路

MSP430F471x3,MSP430F471x6, MSP430F471x7混合信号微控制器数据表

IPC-6012E CN 2020中文 CN 刚性印制板的鉴定及性能规范

FPGA | Xilinx ISE14.7 LVDS应用

Xilinx ISE14.7 LVDS的应用

Xilinx SelectIO资源内部的IDELAYE2应用介绍

《Xilinx—UG471中文翻译》(1)IDELAYE2原语介绍

《Xilinx—UG471中文翻译》(1)IDELAYE2原语介绍

评论