1、为什么需要计算FIFO的最小深度

因为笔试常考。

开玩笑的。首先我们来想下FIFO有哪些作用?我大概总结下FIFO的几个重要作用:

解决不同时钟域传输的问题

用来缓存一定量的数据

解决位宽不匹配的问题

FIFO最常被用来解决写、读不匹配的问题(时钟、位宽),总结下来,其实FIFO最大的作用就是缓冲。既然是缓冲,那么就要知道这个缓存的空间到底需要多大。接下来的讨论,都建立在满足一次FIFO突发传输的基础上。连续无止境的突发不考虑。比如写时钟100M,读时钟50M,无限制的读写,那么FIFO的深度只能是无穷大了,因为写比读快,FIFO一定永远都不够用。所以在实际运用中,不会存在无限制的对FIFO进行读写。如果这样的话,FIFO就变成了一个“存储器件”,而不是一个“缓存器件”,对于FIFO的这种用法无疑是毫无意义的。

2、实例

2.1、写时钟快、读时钟慢

2.1.1、无间断的写、读操作

条件:

写入时钟频率 fA = 80MHz;读取时钟频率 fB = 50MHz. 一次写入的突发长度120

读写操作不间断

解法:

写入一个数据需要的时间:1/80MHz = 12.5ns;读取一个数据需要的时间:1/50MHz = 20ns

写入120个数据,需要的时间:120 * 12.5ns = 1500ns

在写入全部数据所需的时间(1500ns)内,可以读取出的数据数:1500ns / 20ns = 75

所以一次突发,一共需要写入120数据,在这段时间内可以被读出75数据,剩下的数据就是需要使用FIFO来缓存,所以FIFO的最小深度为120 - 75 = 45

2.1.2、间断的写、读操作

条件:

写入时钟频率 fA = 80MHz;读取时钟频率 fB = 50MHz. 一次写入的突发长度120。

每两次写入操作间隔1个写时钟周期,每两次读取操作间隔3个读时钟周期。

解法:

每两次写入操作间隔1个写时钟周期,等于每两个写时钟周期才写入1个数据,即等价的写入时钟频率 fA'=40MHz,写入一个数据需要的时间:1/40MHz = 25ns

每两次读取操作间隔3个读时钟周期,等于每4个写时钟周期才读取1个数据,即等价的读取时钟频率 fB'=12.5MHz,读取一个数据需要的时间:1/12.5MHz = 80ns

写入120个数据,需要的时间:120 * 25ns = 3000ns

在写入全部数据所需的时间(3000ns)内,可以读取出的数据数:3000ns / 80ns = 37.5 ≈ 37(要向下取整,不然有1个数据会丢)

所以一次突发,一共需要写入120数据,在这段时间内可以被读出37数据,剩下的数据就是需要使用FIFO来缓存,所以FIFO的最小深度为120 - 37 = 83

2.2、写时钟慢、读时钟快

2.2.1、无间断的写、读操作

条件:

写入时钟频率 fA = 30MHz;读取时钟频率 fB = 50MHz. 一次写入的突发长度120

写、读操作无间断

解法:

因为读操作的频率快于写操作的频率,所以数据一旦被写入FIFO后很快就会被读走,所以FIFO的最小深度为1即可

2.2.2、间断的写、读操作

条件:

写入时钟频率 fA = 30MHz;读取时钟频率 fB = 50MHz. 一次写入的突发长度120。

每两次写入操作间隔1个写时钟周期,每两次读取操作间隔3个读时钟周期。

解法:

每两次写入操作间隔1个写时钟周期,等于每两个写时钟周期才写入1个数据,即等价的写入时钟频率 fA'=15MHz,写入一个数据需要的时间:1/15MHz = 66.667ns

每两次读取操作间隔3个读时钟周期,等于每4个写时钟周期才读取1个数据,即等价的读取时钟频率 fB'=12.5MHz,读取一个数据需要的时间:1/12.5MHz = 80ns

写入120个数据,需要的时间:120 * 66.667ns = 8000ns

在写入全部数据所需的时间(8000ns)内,可以读取出的数据数:8000ns / 80ns = 100

所以一次突发,一共需要写入120数据,在这段时间内可以被读出100数据,剩下的数据就是需要使用FIFO来缓存,所以FIFO的最小深度为120 - 100 = 20

2.3、写时钟、读时钟一样快

2.3.1、无间断的写、读操作

条件:

写入时钟频率 fA = 读取时钟频率 fB = 30MHz。一次写入的突发长度120。

写、读操作无间断

解法:

1、假设读、写时钟无位差、则两个时钟同频、同相,是同步信号,故可以直接对接操作,无需FIFO

2、若读、写时钟存在相位差,则被写入的数据在一个时钟周期内会被读走,所以FIFO的最小深度为1即可

2.3.2、间断的写、读操作

条件:

写入时钟频率 fA = 读取时钟频率 fB = 50MHz。一次写入的突发长度120。

每两次写入操作间隔1个时钟周期,每两次读取操作间隔3个时钟周期。

解法:

每两次写入操作间隔1个写时钟周期,等于每两个写时钟周期才写入1个数据,即等价的写入时钟频率 fA'=25MHz,写入一个数据需要的时间:1/25MHz = 40ns

每两次读取操作间隔3个读时钟周期,等于每4个写时钟周期才读取1个数据,即等价的读取时钟频率 fB'=12.5MHz,读取一个数据需要的时间:1/12.5MHz = 80ns

写入120个数据,需要的时间:120 * 40ns = 4800ns

在写入全部数据所需的时间(4800ns)内,可以读取出的数据数:4800ns / 80ns = 60

所以一次突发,一共需要写入120数据,在这段时间内可以被读出60数据,剩下的数据就是需要使用FIFO来缓存,所以FIFO的最小深度为120 - 60 = 60

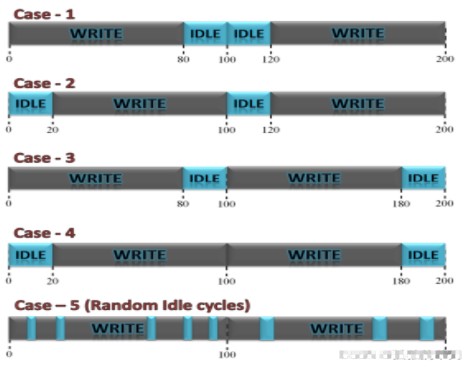

2.4、特定时间内时间写、读速率固定

条件:

每100个时钟写入80个数据,剩余20个随机值(无效)

每10个时钟读出8个数据

一次写入的突发长度160

解法:

因为每100个时钟内,仅写入80个数据,而这80个数据可能任意分布,所以160个数据的写入可能有以下几种情况:

可以看到,第4种情况是最极端的:一次性需要写入160数据,时间为160个时钟

160个时钟内,读出的数据是160*8/10 = 128

所以一共需要写入160数据,在这段时间内可以被读出128数据,剩下的数据就是需要使用FIFO来缓存,所以FIFO的最小深度为160 - 128 = 32

3、总结

FIFO是用来缓存的,不是用来存数据的,当写快读慢时,无止境的对FIFO操作是没有意义的(不管FIFO多大,一定都会被写满)

FIFO深度的计算建立在满足一次突发传输的基础上

当读快写满或者读写一样快时,FIFO的深度最多只需要1

当写快读慢时,在一次突发传输时,因为读慢,所以肯定无法全部读走。全部写入的数据量 - 已经被读走的数据量 = 需要缓存到FIFO的数据量,即异步FIFO的最小深度

审核编辑:汤梓红

-

存储

+关注

关注

13文章

4292浏览量

85782 -

fifo

+关注

关注

3文章

387浏览量

43635 -

计算

+关注

关注

2文章

448浏览量

38778

发布评论请先 登录

相关推荐

FIFO Generator的Xilinx官方手册

Efinity FIFO IP仿真问题 -v1

FPGA做深度学习能走多远?

基于Python的深度学习人脸识别方法

简单认识深度神经网络

基于深度学习的小目标检测

如何在CYUSB2014-BZXC中以8位模式配置Slave FIFO?

深度学习在计算机视觉领域的应用

同步FIFO和异步FIFO区别介绍

如何简单快速地计算FIFO的最小深度

如何简单快速地计算FIFO的最小深度

评论