多看一些example design之后,你就会发现都是熟悉的配方。

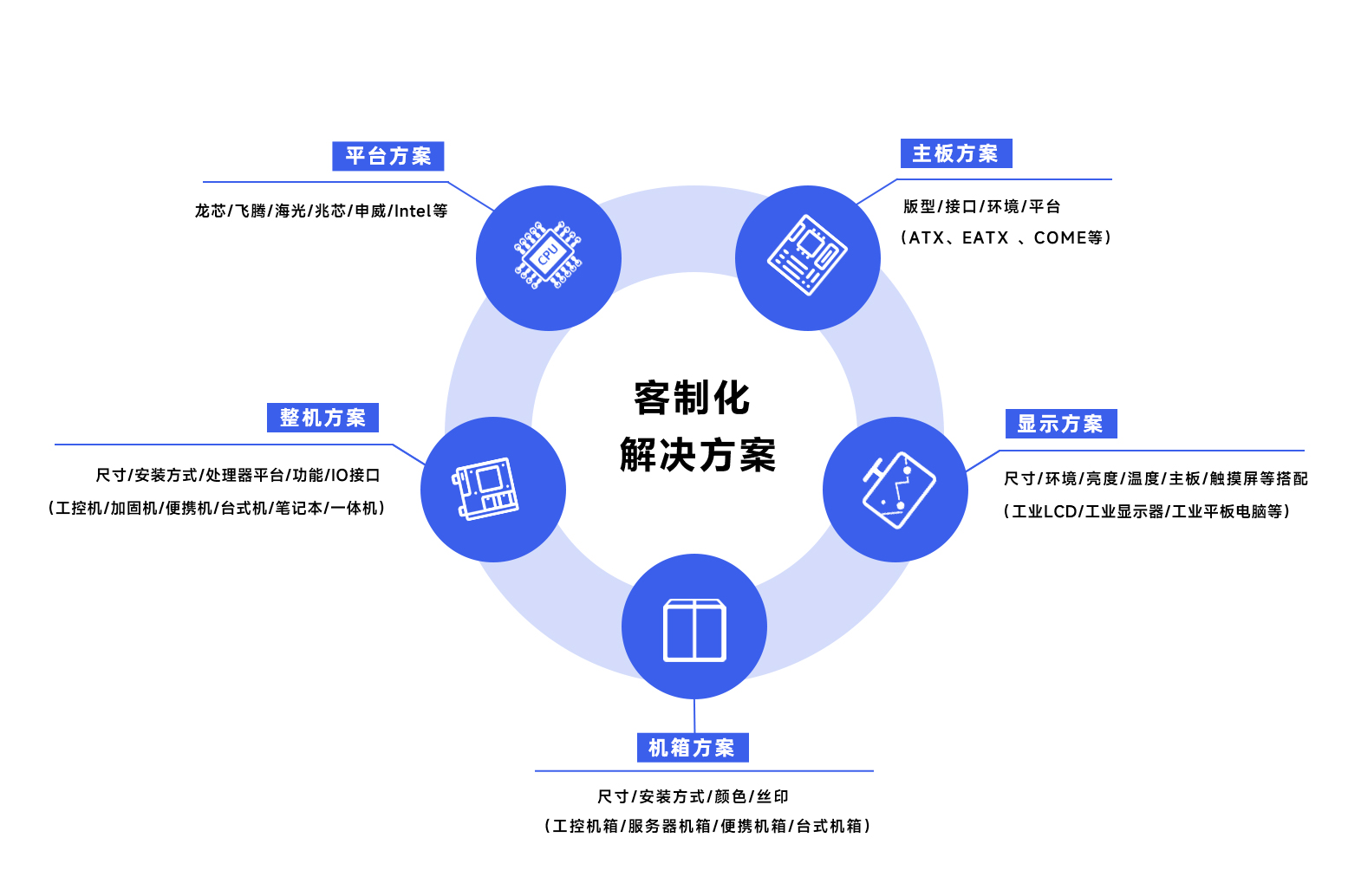

一、Example Design

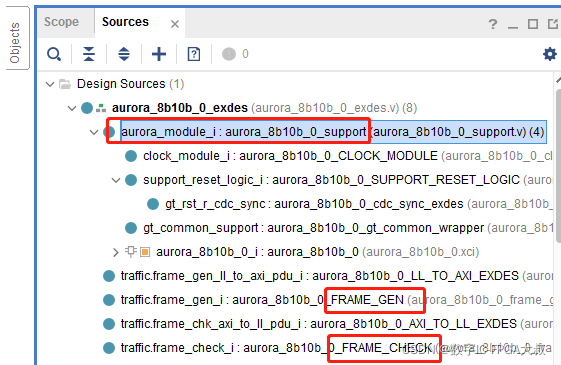

首先打开example design,看看示例工程架构:

多看一些xilinx的example design之后,你就会发现都是熟悉的配方:

support是核心模块,包含了IP的例化、时钟及复位逻辑;重点理解。

frame_gen 是数据产生模块;

frame_check是数据接收检查模块;

support.v

support是核心模块,包含了IP的例化、时钟及复位逻辑;时钟和复位在前面文章已经介绍过了,就不再啰嗦;先看下support对外的端口信号:

module aurora_8b10b_0_support

(

// AXI TX Interface

input [15:0] s_axi_tx_tdata,

input [1:0] s_axi_tx_tkeep,

input s_axi_tx_tvalid,

input s_axi_tx_tlast,

output s_axi_tx_tready,

// AXI RX Interface

output [15:0] m_axi_rx_tdata,

output [1:0] m_axi_rx_tkeep,

output m_axi_rx_tvalid,

output m_axi_rx_tlast,

// GT Serial I/O

input rxp,

input rxn,

output txp,

output txn,

// GT Reference Clock Interface

input gt_refclk1_p,

input gt_refclk1_n,

// Error Detection Interface

output frame_err,

output hard_err,

output soft_err,

// Status

output lane_up,

output channel_up,

// System Interface

output user_clk_out,

input gt_reset,

input reset,

input power_down,

input [2:0] loopback,

output tx_lock,

input init_clk_p,

input init_clk_n,

output init_clk_out,

output tx_resetdone_out,

output rx_resetdone_out,

output link_reset_out,

output sys_reset_out,

//DRP Ports

input drpclk_in,

input [8:0] drpaddr_in,

input drpen_in,

input [15:0] drpdi_in,

output drprdy_out,

output [15:0] drpdo_out,

input drpwe_in,

output pll_not_locked_out

);

首先是framing接口的发送及接收的端口信号,与上一篇我们介绍的一致;我们使用Aurora IP,无非就是将需要发送的数据放到s_axi_tx_tdata数据总线上,从m_axi_rx_tdata数据总线上接收数据。有了这点认知后,理解就简单多了。接着是GT串行I/O,对应物理管脚。接着就是状态信号channel_up,channel_up信号拉高,表明链路建立成功可以进行正常数据收发。然后是一些时钟和复位信号,最后是DRP动态重配置的相关信号。

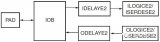

继续看support对Aurora 8b/10b的例化:

aurora_8b10b_0 aurora_8b10b_0_i

(

// AXI TX Interface

.s_axi_tx_tdata (s_axi_tx_tdata),

.s_axi_tx_tkeep (s_axi_tx_tkeep),

.s_axi_tx_tvalid (s_axi_tx_tvalid),

.s_axi_tx_tlast (s_axi_tx_tlast),

.s_axi_tx_tready (s_axi_tx_tready),

// AXI RX Interface

.m_axi_rx_tdata (m_axi_rx_tdata),

.m_axi_rx_tkeep (m_axi_rx_tkeep),

.m_axi_rx_tvalid (m_axi_rx_tvalid),

.m_axi_rx_tlast (m_axi_rx_tlast),

// GT Serial I/O

.rxp (rxp),

.rxn (rxn),

.txp (txp),

.txn (txn),

// GT Reference Clock Interface

.gt_refclk1 (gt_refclk1),

// Error Detection Interface

.frame_err (frame_err),

// Error Detection Interface

.hard_err (hard_err),

.soft_err (soft_err),

// Status

.channel_up (channel_up),

.lane_up (lane_up),

// System Interface

.user_clk (user_clk_i),

.sync_clk (sync_clk_i),

.reset (system_reset_i),

.power_down (power_down),

.loopback (loopback),

.gt_reset (gt_reset_i),

.tx_lock (tx_lock_i),

.init_clk_in (init_clk_i),

.pll_not_locked (pll_not_locked_i),

.tx_resetdone_out (tx_resetdone_i),

.rx_resetdone_out (rx_resetdone_i),

.link_reset_out (link_reset_i),

.drpclk_in (drpclk_i),

.drpaddr_in (drpaddr_in),

.drpen_in (drpen_in),

.drpdi_in (drpdi_in),

.drprdy_out (drprdy_out),

.drpdo_out (drpdo_out),

.drpwe_in (drpwe_in),

//_________________COMMON PORTS _______________________________

// ------------------------- Common Block - QPLL Ports ------------------

.gt0_qplllock_in (gt0_qplllock_i),

.gt0_qpllrefclklost_in (gt0_qpllrefclklost_i),

.gt0_qpllreset_out (gt0_qpllreset_i),

.gt_qpllclk_quad1_in (gt_qpllclk_quad1_i ),

.gt_qpllrefclk_quad1_in (gt_qpllrefclk_quad1_i ),

.sys_reset_out (sys_reset_out),

.tx_out_clk (tx_out_clk_i)

);

啊这,突然觉得官方例程的注释已经很清楚了,再罗里吧嗦的介绍有点烦。

真不是笔者偷懒~ = =||

个人建议,把时钟复位理清楚,再按照framing接口时序,来设计数据的收发。基本上就能使用Aurora搬砖了。

二、仿真

直接看仿真,清晰明了。

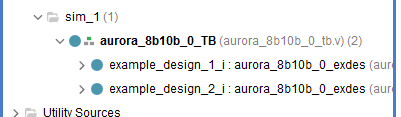

可以看到,还是熟悉的配方,仿真顶层还是例化了两个example实体,然后在TB顶层对其进行环回连接:

assign rxn_1_i = txn_2_i;

assign rxp_1_i = txp_2_i;

assign rxn_2_i = txn_1_i;

assign rxp_2_i = txp_1_i;

也就是说,Aurora-2的发送管脚接到了Aurora-1的接收管脚,那么Aurora-2发送的数据必然与Aurora-1接收到的数据是相等的;我们打开仿真,验证一下。

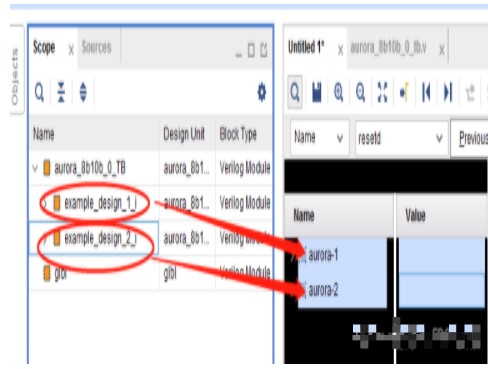

首先把相关信号拖到仿真,并设置group,便于归类查看:

根据推论,先看Aurora-2发送的第一个数据:

如图所示:

tx_data = 16’he6d5; 只有一个数据,占了一个时钟周期(user_clk时钟域),所以tlast与tvalid都只是同时拉高了一个时钟周期。同时,tkeep = 2’h3;表明这个数据所有字节都是有效的。另外注意,数据是在valid和ready握手(同时有效)时发送的。

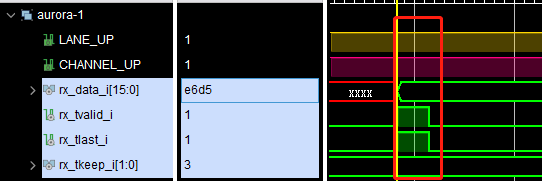

再看Aurora-1接收的第一个数据:

如图所示:

当rx_tvalid有效时,rx_data = 16’he6d5;同时,tlast信号为1,表明这一次数据传输的接收完毕。rx_tkeep = 2’h3,表明数据全部字节有效。

通过对比可知,接收数据等于发送数据。验证成功。

接下来可以继续验证Aurora-2发送的第二个数据与Aurora-1接收的第一个数据;也可以验证Aurora-1发送的数据与Aurora-2接收的数据。这里就不再啰嗦了。

下一篇,我们基于Aurora IP完成自己的数据收发。

审核编辑:汤梓红

-

AURORA

+关注

关注

0文章

25浏览量

5377

发布评论请先 登录

相关推荐

如何在ModelSim中添加Xilinx仿真库

介绍MCUboot支持的四种升级模式(2)

Xilinx SelectIO资源内部的IDELAYE2应用介绍

Xilinx 7系列FPGA功能特性介绍

Xilinx FPGA NVMe主机控制器IP,高性能版本介绍应用

国产计算机平台介绍(四)——飞腾

FPGA新IP核学习的正确打开方式

俄罗斯操作系统Aurora OS 5.0发布

Xilinx平台Aurora IP介绍(四)Example Design介绍

Xilinx平台Aurora IP介绍(四)Example Design介绍

评论