在搭建完Block Design以及硬件代码后,生成bit;

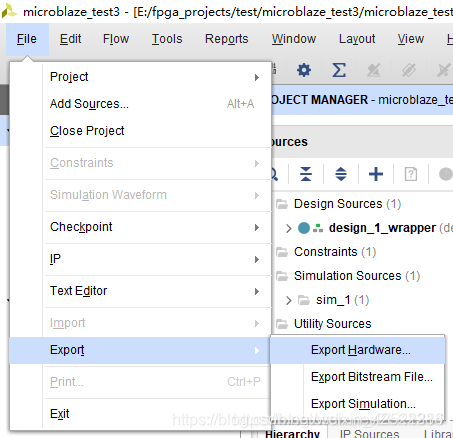

bit文件生成成功后,点击Export Hardware,导出xsa文件:(xsa做连接使用)

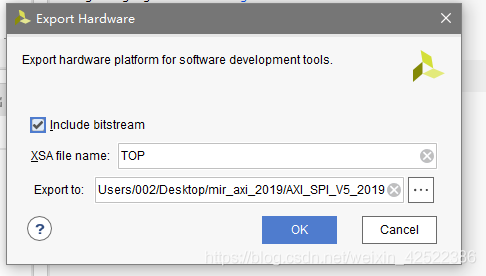

勾选 include bitstream

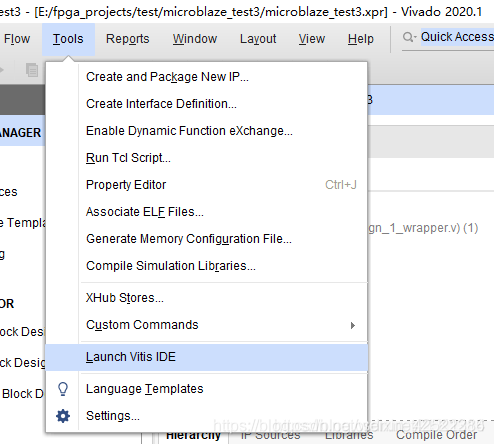

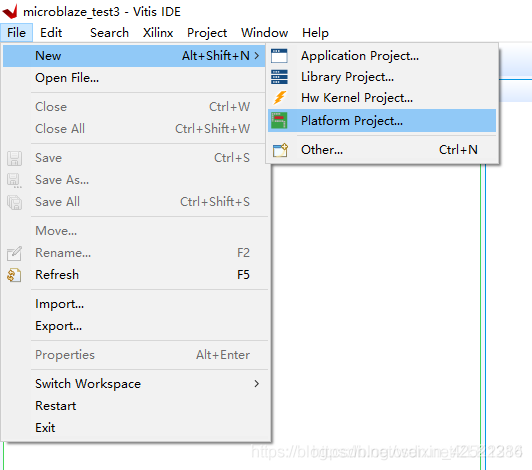

有了xsa文件,就可以启动Vitis 了。

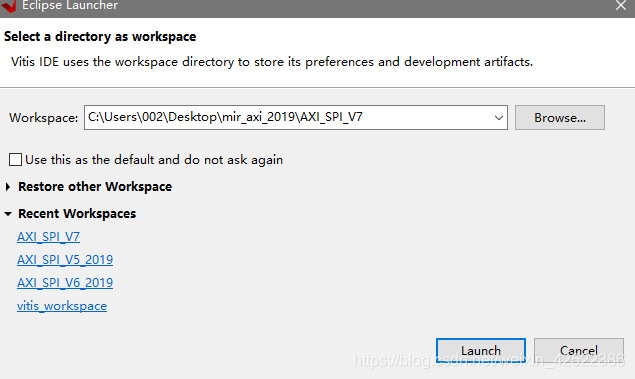

选择工作目录

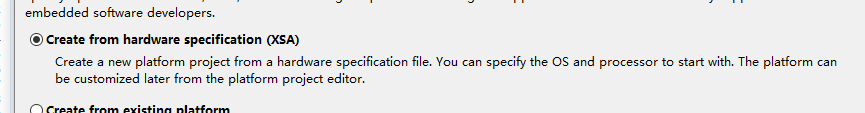

选择使用xsa后,选择XSA路径即可。完成后bulid project!!!

再建立一个APP project工程,用于代码书写。写完后bulid project!!!

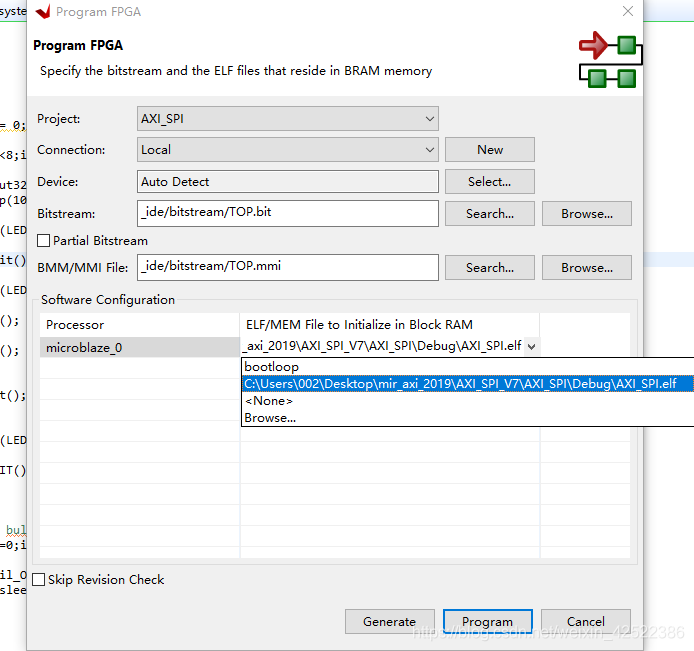

开始固化

固化需要两步。

第一步是在Program FPGA对话框里面,将bit文件和Vitis工程elf文件合并成一个download.bit文件:

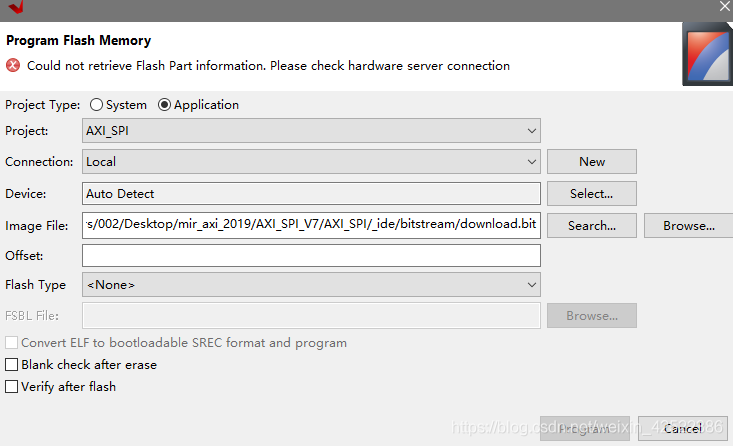

第二步就是在Program Flash对话框中,把合并后的download.bit文件烧写到SPI Flash里面:

选择对应型号flash即可。

若更改vivado代码更改了,新生成了bit文件,然后,整个Vitis工程都必须删了重建!!!!!!

重新建立Platform工程,Build一下,再重新建立Application工程,再Build一下

点Program FPGA生成download.bit,再点Program Flash把download.bit固化到flash

审核编辑:符乾江

-

代码

+关注

关注

30文章

4841浏览量

69196 -

Vitis

+关注

关注

0文章

147浏览量

7529

发布评论请先 登录

相关推荐

UV光固化:一项高效环保的固化技术

UVLED光固化机:固化行业的革新力量

一文搞懂软核的固化、启动和MultiBoot实现

AMD Vitis Unified Software Platform 2024.2发布

MicroBlaze V软核处理器的功能特性

UV胶固化新选择,UVLED固化灯瓦数如何选择?

FPGA的IP软核使用技巧

UVLED固化炉新突破:秒速固化,效率翻倍!

在Windows 10上创建并运行AMD Vitis™视觉库示例

Vitis软核固化代码流程说明

Vitis软核固化代码流程说明

评论