前言

在STA中,要分析上游器件和FPGA之间的时序关系就得指定input delay。

流程

什么是input delay:约定上游芯片输出及时钟之间的关系。约束的目的就是看适配后的时序关系是什么样的。

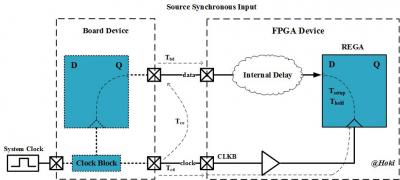

以下以源同步接口举例,上游芯片发送data和随路时钟到下游FPGA芯片端口进行接收,使用解串原语对数据进行解串。

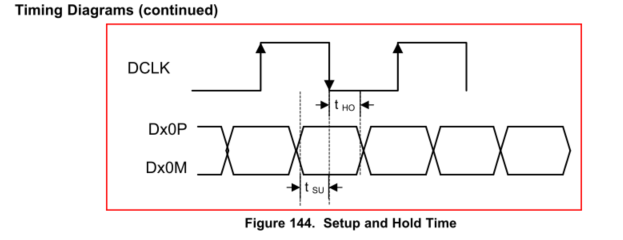

这里使用的DCLK为:4.464ns。时钟与数据关系是DDR中心对齐。

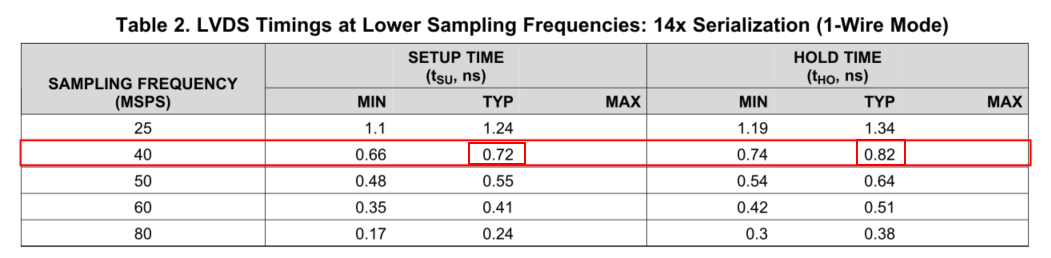

40M下的建立保持时间如下:Tsu=0.72ns,Tho = 0.82ns。

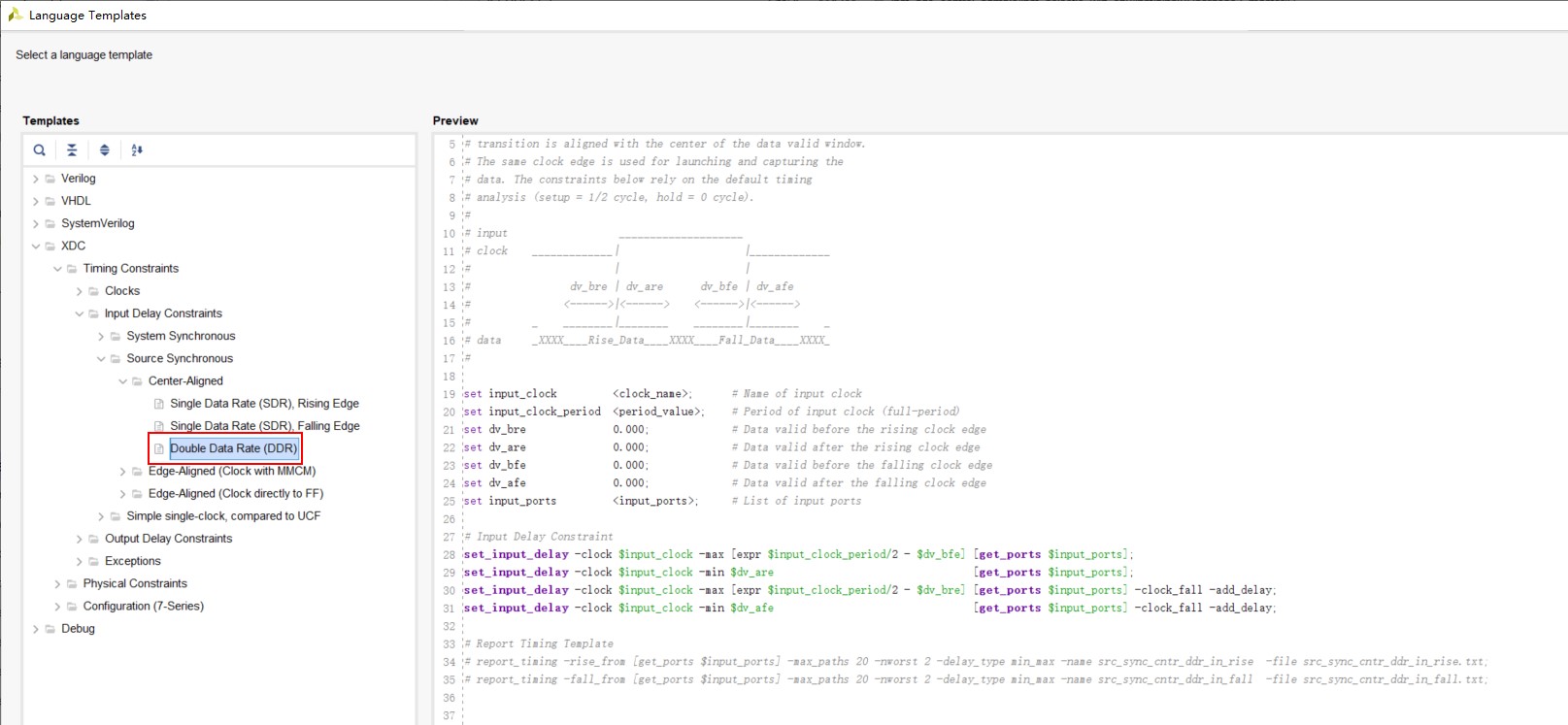

上vivado中语言模板中找模板。把Tsu、Tho抄进去对应dv_bre、dv_are、dv_bfe、dv_afe。dv_bre指的是时钟沿前稳定的时间,这个时间可以用示波器测出来,或者看datasheet上的建立保持时间(这之间的数据肯定是稳定的)。

得到:min=Tho=0.82ns,max=T/2-Tsu=4.464/2-0.72=1.512ns;这里假定时钟和数据到FPGA的路径长度是一致的(由PCB布线保证)。

set_input_delay -clock [get_clocks adc_dco_clk] -clock_fall -min -add_delay 0.820 [get_ports i_data_ch0_p]

set_input_delay -clock [get_clocks adc_dco_clk] -clock_fall -max -add_delay 1.512 [get_ports i_data_ch0_p]

set_input_delay -clock [get_clocks adc_dco_clk] -min -add_delay 0.820 [get_ports i_data_ch0_p]

set_input_delay -clock [get_clocks adc_dco_clk] -max -add_delay 1.512 [get_ports i_data_ch0_p]

编译分析STA结果:

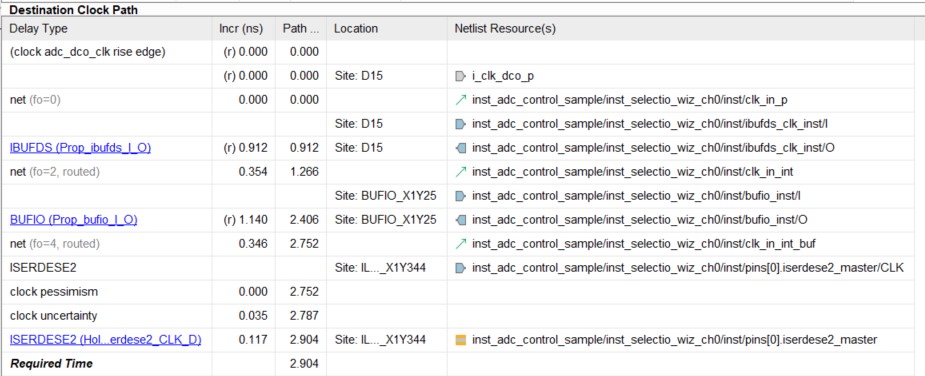

本次时钟路径:IBUFDS→BUFIO→ISERDESE 差分时钟经过IBUFDS变为单端,经过IOB中的BUFIO送入ISERDESE。

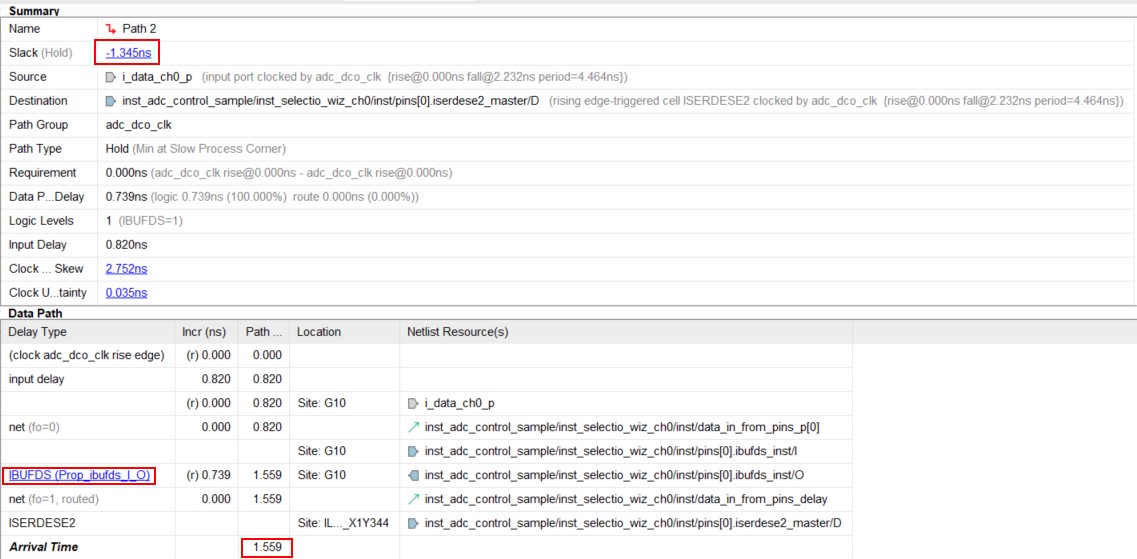

本次数据路径:IBUFDS→ISERDESE 差分数据经过IBUFDS变成单端送入ISERDESE。

则要求数据在2.904ns时候到来,但数据抵达时刻是1.559ns,出现了保持违例:1.559-2.904 = -1.345ns。

也就是说数据来早了,提前撤销导致了保持违例。另一个角度说是时钟来晚了。

所以要解决这个问题,可以让数据晚点来,或者让时钟早点来。

对于片内逻辑间的保持不满足可以插LUT1,但接口IOB部分就没法插了,于是上网上找方法。

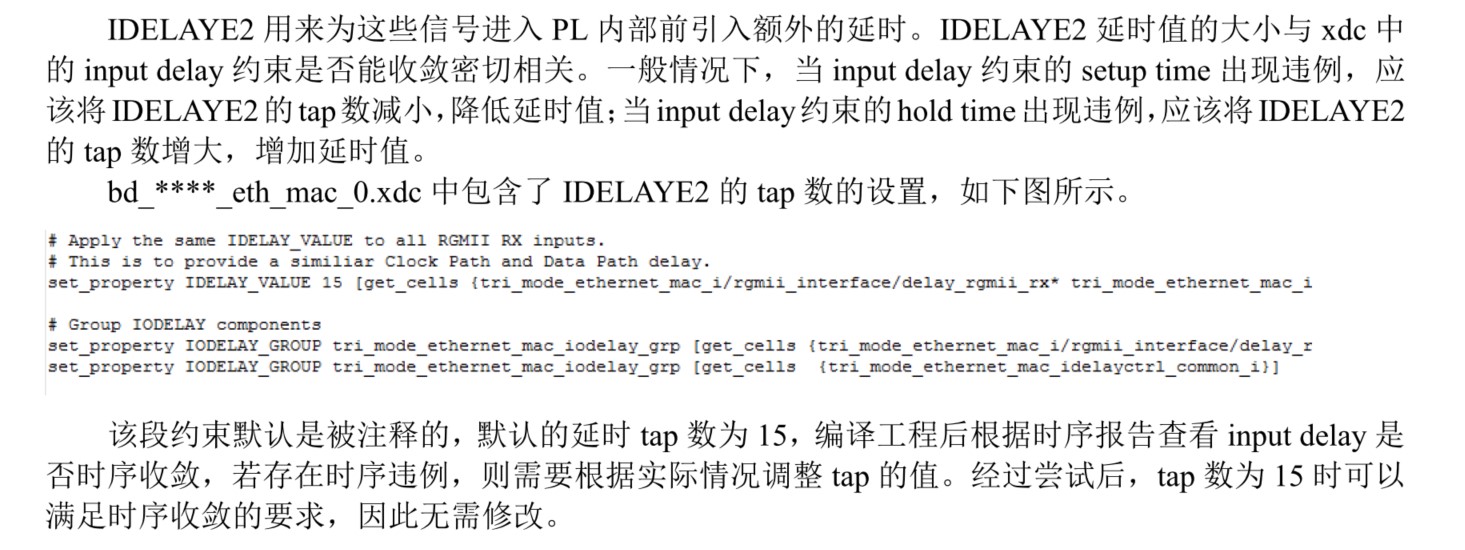

参考前面参考链接可知:可使用IODELAY原语对数据进行相应的延时,达到保持时间的满足。

这里1.345ns/78ps=18拍,即IODELAY至少需要延迟18拍;

时序约束文件中参考下述图片写,但我还没有验证过,待验证,理论可行,估计就可以STA通过了。

这个延时可以通过时序训练或者手动调节,找寻合适点。具体可参考:xapp524-serial-lvds-adc-interface.pdf

如果是动态调节TAP值,那么STA就没卵用了,STA的前提是假定TAP值为定值。

审核编辑:汤梓红

-

FPGA

+关注

关注

1634文章

21821浏览量

607552 -

芯片

+关注

关注

458文章

51475浏览量

429136 -

Vivado

+关注

关注

19文章

816浏览量

67126

发布评论请先 登录

相关推荐

ADC08D500要一起工作做Interleaving的话,需要在ADC CLK Input端各接一个Delay Line IC对吗?

ADS1281 FIR滤波器Input sample rate,Decimation factor, Decimation offset, Estimated delay是如何确定的?

常用时序约束使用说明-v1

如何做才能使TAS5631处于准备状态呢?

硬件工程师如何做元器件变更的决策

详细讲解SDC语法中的set_input_delay和set_output_delay

Xilinx FPGA编程技巧之常用时序约束详解

详解Vivado非工程模式的精细设计过程

Vivado中如何做set_input_delay约束

Vivado中如何做set_input_delay约束

评论