实验目的:

为了更方便的对DDR读写,我们对DDR再次封装成可复用的读写模块。

一、前言

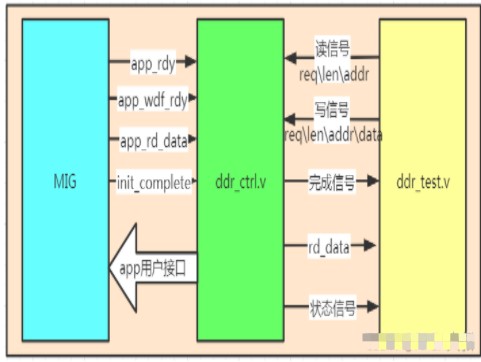

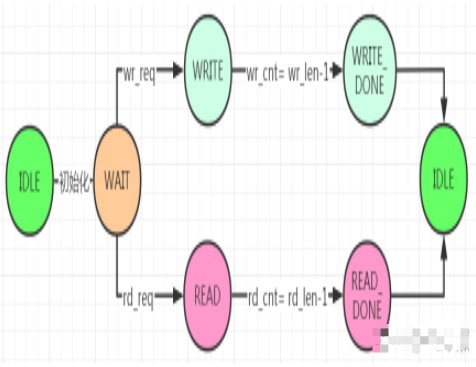

因为DDR3是半双工,所以DDR读写模块应该包括三部分内容:

ddr3_top.v :

1. ddr3读操作子模块

2. ddr3写操作子模块

3. ddr3读/写仲裁模块

但是在实际项目使用时,DDR都要根据实际需求来进行读写操作,所以本文旨在提供一种思路,将读/写/仲裁合在一个模块,实际使用当结合具体情况而定。

实现目标: 给出(写请求、写长度、写数据、写地址)就写入ddr3,给出(读请求、读长度、读地址)就从ddr3读相应数量的数据出来。

二、方案设计

2.1 系统框图

2.2设计状态机

2.3代码实现

代码都是浮云~

记得带我入门的老师傅说过:只写代码,那是码农干的~

重点是方案,是思路~

2.4仿真验证

写入200个数,1-200;

读出100个数,1-100;

验证成功。

三、其他

本章写的比较简略,主要参考黑金教程而来。实际使用正如文章开始所说,视具体情况而定。

1. ddr读写大都以FIFO作衔接,方便操作;

2. 读写操作按照时序图操作就ok,主要设计读写仲裁方案。

3.1后记

本章确实写的比较简陋,原因一是使用情况具体分析;二是时间耽搁太久了,还有很多东西需要学习;先把DDR放一放,后面有更深的理解的时候再来补充。

DDR3系列算是笔者第一个完整的系列文章,整理的同时顺便加深自己理解,有点爱上写博客了~

终于结束这个篇章了,这周末开始GTX接口系列文章的整理!

审核编辑:汤梓红

-

FPGA

+关注

关注

1635文章

21836浏览量

608245 -

封装

+关注

关注

127文章

8129浏览量

143834 -

Xilinx

+关注

关注

71文章

2173浏览量

122803

发布评论请先 登录

相关推荐

三大内存原厂或将于2025年停产DDR3/DDR4

DDR3、DDR4、DDR5的性能对比

如何选择DDR内存条 DDR3与DDR4内存区别

基于FPGA的DDR3多端口读写存储管理设计

三星和SK海力士下半年停产DDR3内存

华邦倾力挺进DDR3市场,抓住转单商机

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 电源解决方案同步降压控制器数据表

完整DDR,DDR2,DDR3 和LPDDR3 存储器电源解决方案同步降压控制器数据表

完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表

适用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF缓冲基准的TPS51206 2A峰值灌电流/拉电流DDR终端稳压器数据表

具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表

具有同步降压控制器、2A LDO和缓冲基准的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4内存电源解决方案数据表

完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表

Xilinx FPGA平台DDR3设计保姆式教程(六)

Xilinx FPGA平台DDR3设计保姆式教程(六)

评论