干货来了,用DDR搬砖,只需要会用IP就好,Xilinx官方YYDS!

一、MIG IP核配置

工具 :VIVADO 2018.3

FPGA : XC7K325FFG900-2

DDR3 : MT41J256M16XX-125

配置时钟部分,建议详看第二篇《DDR各时钟频率分析》

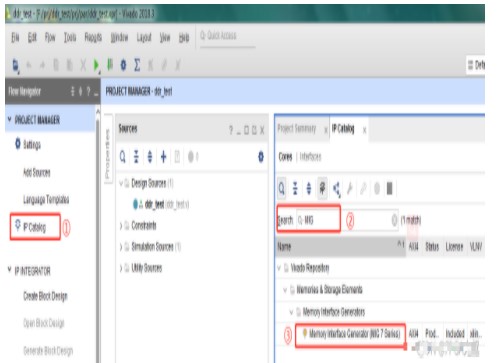

(1)选中“MIG”进入配置界面

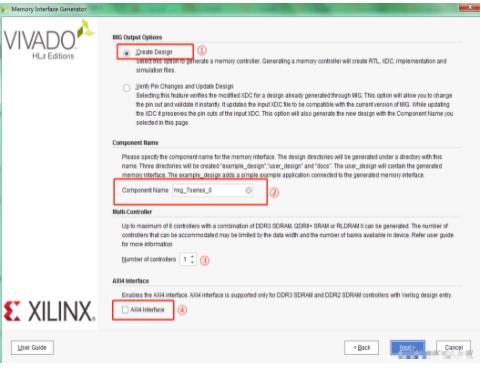

(2)选择Create Design来创建设计

①选择Create Design来创建设计

②自定义名字

③选择1个控制器就好

④是否使用AXI4接口,为了简化理解,不勾选

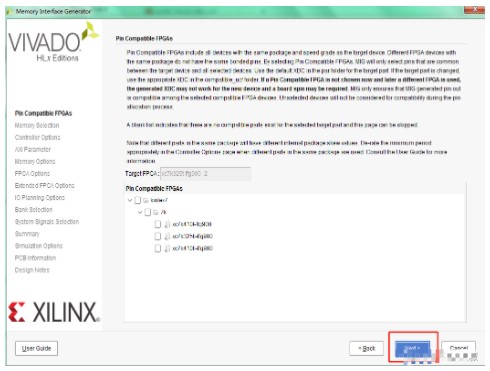

(3)是否选择兼容其他器件(不需要,直接NEXT)

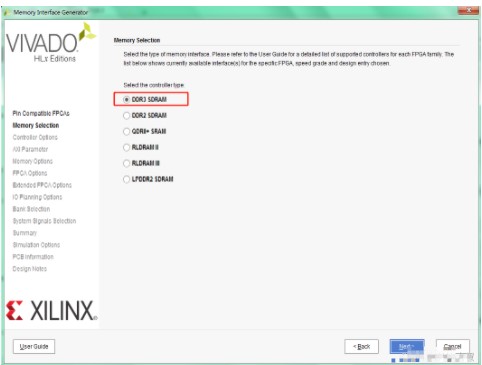

(4)存储器选择,还用说吗,DDR3走起

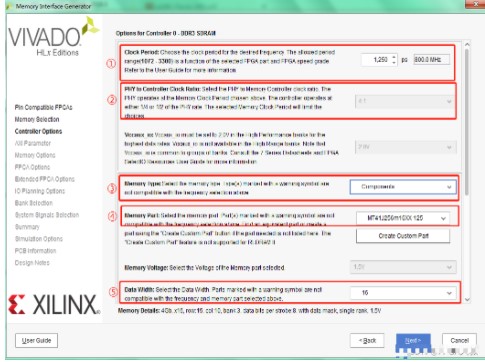

(5)重点来了,时钟配置、DDR选型

①Clock Period,即DDR芯片物理侧的IO时钟频率,称之为核心频率

②物理侧到控制器时钟的比例,可选4:1或2:1;决定了ui_clk的频率;

如图配置的话,ui_clk = 800M /4 =200Mhz

③选择DDR3的类型,Components指的是DDR3的型号是元件类,笔记本那种的插条类是SODIMMs。

④选择DDR3的型号

⑤数据位宽,由DDR型号决定,但是当FPGA挂了多片DDR时,位宽相应增加;

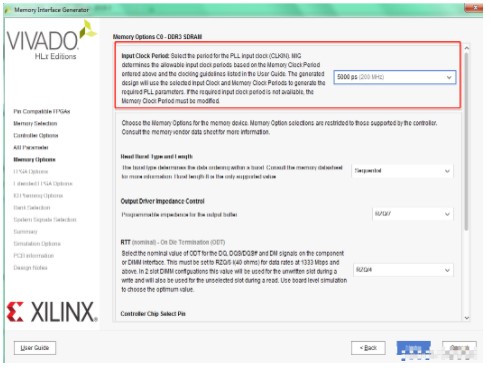

(6)配置系统时钟

系统时钟输入,建议200M,后面参考时钟可以直接使用系统时钟。

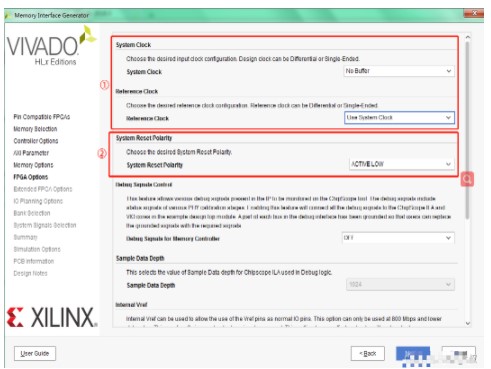

(7)参考时钟、复位

①系统时钟选择NO BUFFER,因为系统时钟为200M,所以参考时钟直接使用系统时钟就好。 参考时钟必须是200Mhz!

②复位是高电平有效还是低电平有效,笔者第一次玩DDR,仿真的时候初始化一直不成功,就是复位信号搞反了 = =||

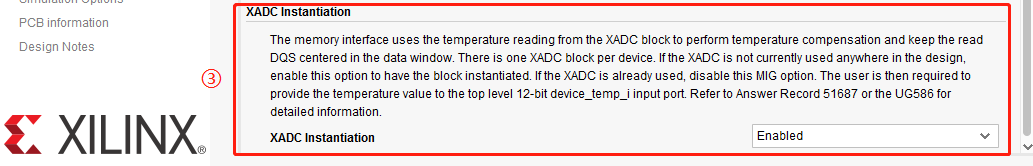

③是否使用XADC,会输出器件的温度,如果其他模块要用XADC,那么这里就不使能。

(8)下一页,50欧电阻,根据硬件而定,不用管,直接NEXT

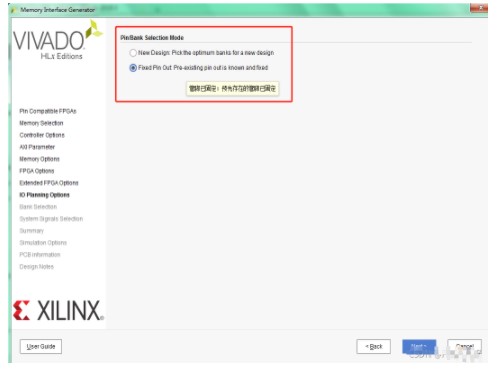

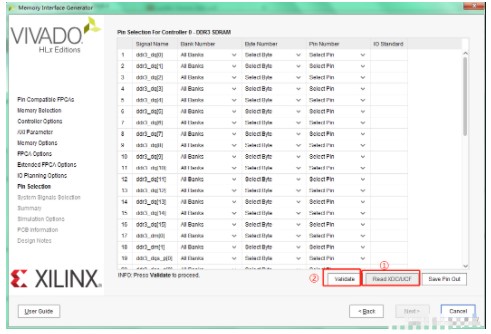

(9)新设计 or 管脚已固定?

如果硬件已经定了,那么就选下面管脚已固定,然后读取约束文件,设置管脚就好。

①管脚读取配置好了,点②确定再next进入下一页。

但是,我们这里只是为了讲解DDR应用,没有硬件,选第一种新设计模式。

(10)后面依次NEXT就好了,最后生成。

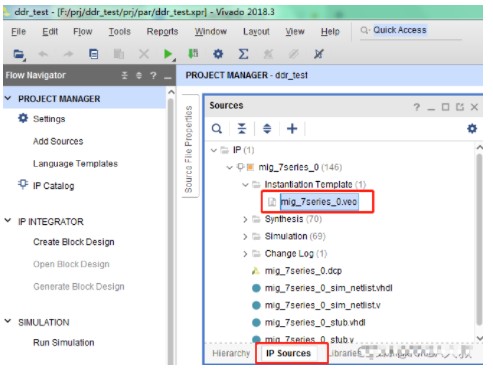

(11)IP核生成完毕,打开veo文件查看例化文件。

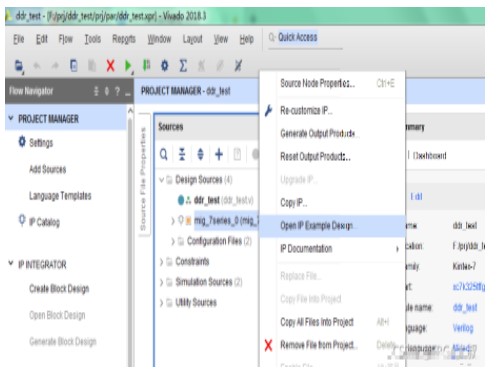

(12)所有不会使用的IP,我们都打开Example Design来了解使用。

IP核配置完成,读写测试下篇再讲,下面重点讲解各端口信号。

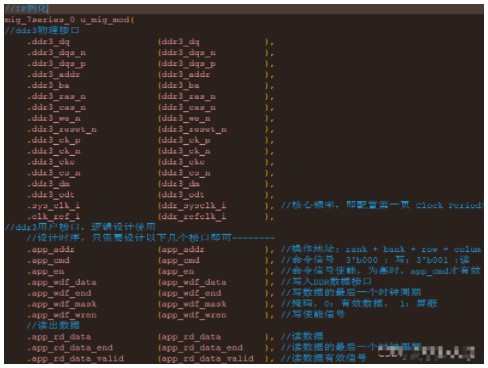

二、端口信号定义

对于mig与DDR3的读写原理我们不需要了解太多,交给mig就可以了。我们需要做的是控制好用户接口,写出正确的用户逻辑,控制好读写时序。想要写好User logic,我们就必须清楚每一个用户控制接口的含义:

2.1全部端口的注释详解

2.2端口信号分类

2.2.1使用DDR只需要设计这几个信号

app_cmd (你总要先确认你想要写还是想要读吧)

操作命令,其实你只需要用到3'b000(写入)和3'b001(读出)

要和操作地址同时出现才有效。

2. app_addr (往哪儿写,从哪儿读?)

操作地址,按照结构从高位到低位是 rank + bank + row + column

3. app_en (确认地址线上的地址有效,不能初始值都一直有效吧)

操作地址app_addr的使能,只有它拉高的时候,对应的app_addr才是有效的

4. app_wdf_data (要写的话,你得有料不是)

写入的数据接口

5. app_wdf_wren (那也不能什么料都往里倒不是)

写入的数据接口app_wdf_data的使能,

只有它拉高的时候,对应的app_wdf_data才是有效的

6. app_wdf_end (要你作甚,一句app_wdf_end = app_wdf_wren 搞定)

理论上应该有点用,但是实际你只要让它跟app_wdf_wren一样就行了

emm...大神这段解释很传神,我直接copy过来了

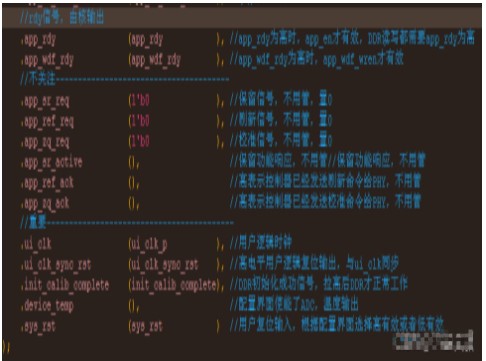

2.2.2 IP核的输出信号

app_rdy (想要DDR帮你干活,也得让人家准备好了不是?)

app_rdy表示UI已经准备好接收命令了,意思就是说必须要等app_rdy信号拉高了之后,app_en和app_cmd等才能开工干活= =

而且,这个不受你控制。等着吧

2. app_wdf_rdy (想要往DDR写数据?不好意思,等我准备好了再说)

app_wdy_rdy信号表示写数据FIFO已经准备好接收数据了,数据在app_wdf_rdy = 1’b1且 app_wdf_wren = 1’b1时被写入。

同理,这个rdy不也受你控制。等着吧

3. init_calib_complete(DDR读写不对?先检查初始化成功了没好吧)

init_calib_complete拉高表明DDR已经校准成功初始化完成了!

拿去搬砖吧!

4. ui_clk(看好了,逻辑使用的时钟搁这输出呢)

在第二篇《DDR的时钟分析》里我们也讲过,ui_clk就是逻辑使用的时钟;由配置界面“Clock Period”与“4:1 / 2:1模式”确定的;如:核心频率为400M;选择了4:1模式,那么ui_clk = 400 / 4 =100 M;

记住,你的逻辑代码工作在ui_clk这个时钟域!

2.2.3 DDR读数据信号归类

再来对DDR的信号规个类吧,哎,这写的真是罗里吧嗦

app_rdy

app_en

app_cmd

app_addr

在app_rdy为高 且 app_en 为高时,让app_cmd = 3’b001,同时我们给出读数据的地址app_addr,那么等段时间延迟后,我们就能读出想要的数据了:(结合后文时序图更容易理解)

app_rd_data

app_rd_data_valid

这就是我们读出的数据了。

2.2.4 DDR写数据信号归类

①前提条件

app_rdy

app_wdf_rdy

app_en

②地址和命令

app_cmd

app_addr

③写数据

app_wdf_wren

app_wdf_data

app_wdf_end

app_wdf_mask :一般不用,直接置0

想要写数据到DDR?必须在①前提条件全部为高时,给出②地址和命令(app_cmd = 3’b000),然后给出③写数据的信号,就成功写入数据到DDR了;

注意:①②时序严格对齐!③相对①②可以提前1拍,或最多延迟2拍,但是最好跟①②对齐,不容易出错。(结合后文时序图更容易理解)

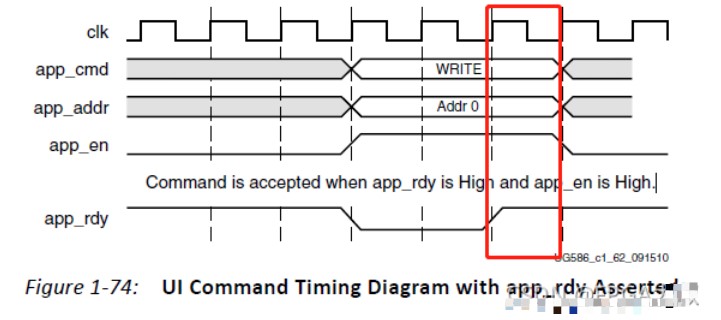

三、时序图

玩接口嘛,大部分根据时序图来就是了,挺简单的

3.1 UI控制时序图

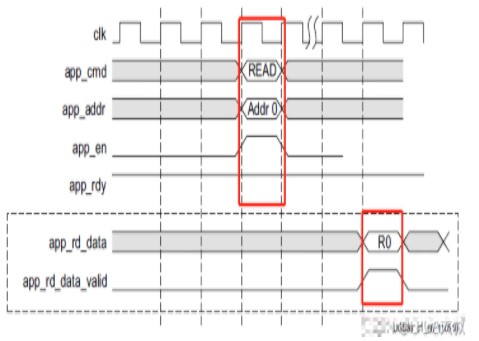

如图所示:

必须要app_rdy拉高时,你所给的(使能app_en、命令app_cmd、地址app_addr)才会被接受。

★app_rdy :前提条件,不管是读还是写,都必须在app_rdy为高的时候进行操作。

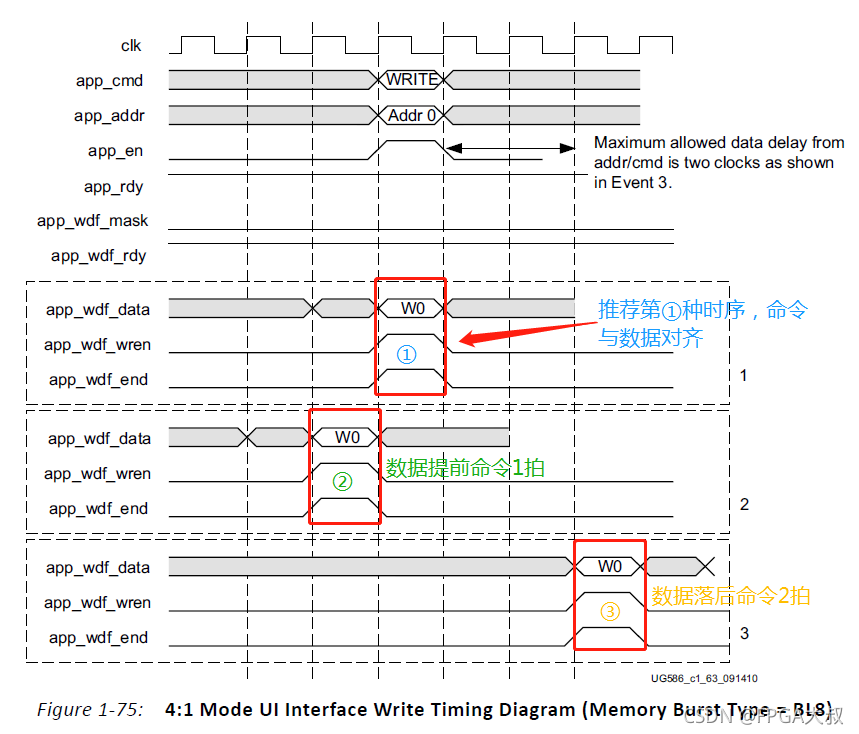

3.2写操作时序图

正如前文信号归类所说:

写入DDR必须在前提条件(app_rdy & app_wdf_rdy)全部为高时,给出地址和命令(app_cmd = 3’b000),然后给出写数据的信号(使能与数据),就成功写入数据到DDR了;

注意:地址和命令必须时序严格对齐!写数据信号相对来说有三种情况:①严格对齐;②可以提前1拍;③最多延迟2拍;但是最好全部时序对齐,不容易出错。

3.3读操作时序图

读操作就简单了,在前提条件app_rdy为高时,给出命令(app_cmd = 3’b001)与地址(app_addr),等段时间延迟,数据就读出来了,以valid信号表示数据有效。

下一篇我们就开始用DDR来搬砖了,测试下读写,初步掌握使用~

四、参考资料

《UG586》 官方文档不多说,YYDS!

《Xilinx平台DDR3设计教程之仿真篇》 一系列文章,笔者就是看过后才初步熟悉了DDR3的使用,推荐给大家。

审核编辑:汤梓红

-

DDR3

+关注

关注

2文章

274浏览量

42157 -

IP核

+关注

关注

4文章

326浏览量

49371

发布评论请先 登录

相关推荐

基于FPGA的DDR3多端口读写存储管理设计

三星和SK海力士下半年停产DDR3内存

SK海力士、三星电子陆续停产DDR3内存,带动市场价格上行

华邦倾力挺进DDR3市场,抓住转单商机

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 电源解决方案同步降压控制器数据表

完整DDR,DDR2,DDR3 和LPDDR3 存储器电源解决方案同步降压控制器数据表

具有同步降压控制器、2A LDO和缓冲基准的完整DDR2、DDR3和DDR3L存储器电源解决方案TPS51216-EP数据表

完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表

适用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF缓冲基准的TPS51206 2A峰值灌电流/拉电流DDR终端稳压器数据表

具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表

具有同步降压控制器、2A LDO和缓冲基准的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4内存电源解决方案数据表

完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表

Xilinx FPGA平台DDR3设计保姆式教程(三)

Xilinx FPGA平台DDR3设计保姆式教程(三)

评论