1. 接口约束类型

2. Tready或Tvalid不连续问题

修改代码,使综合后的启动时间间隔为1;

3. 两个HLS IP核不能之间数据流对接不上

3.1 问题描述

前提:各个IP核的初始化和配置过程确认正确。

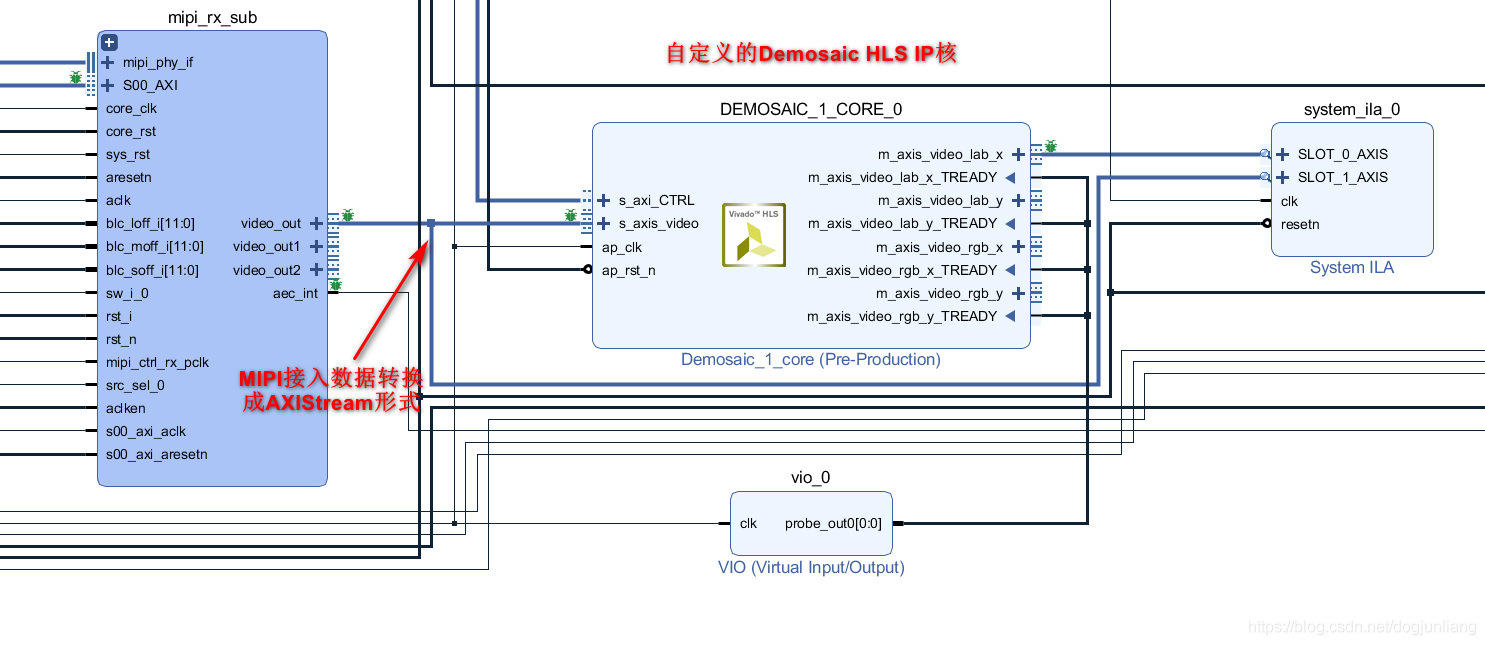

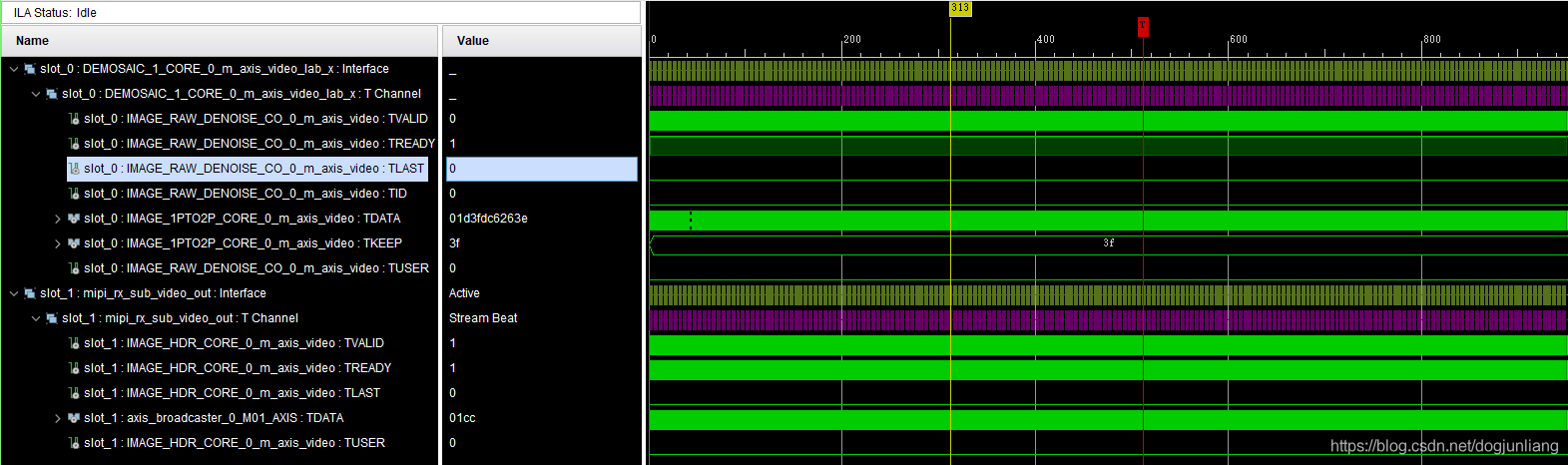

单独添加一个自定义HLS IP核,IP核的master axistream端口的输入Tready全部置1,上板测试后,DEMOSAIC_1_CORE_0的输出总线上是有正常的数据数据流,如图2所示:

图1 添加HLS DEMOSAIC1 IP核电路连接

图2 添加HLS DEMOSAIC1 IP核板级波形

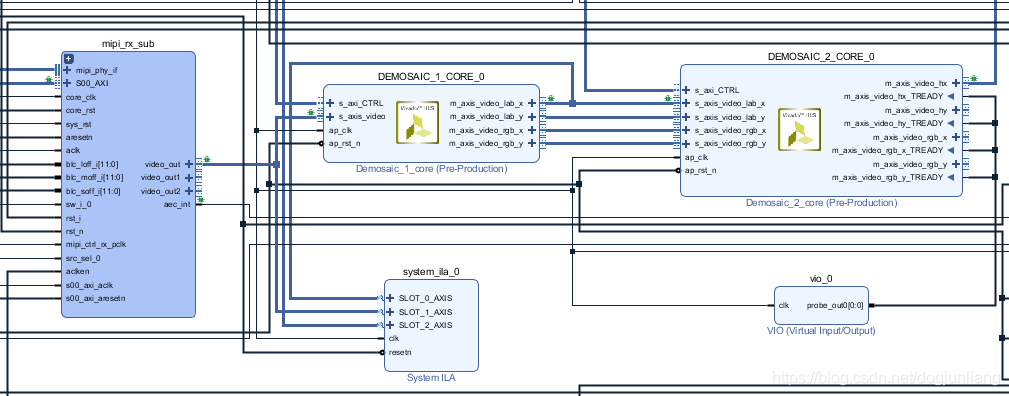

在上述平台上接入自定义HLS IP核DEMOSAIC_2_CORE,DEMOSAIC_2_CORE的MASTER端口Tready输入全部拉高,以便有效数据可以一直输出,硬件电路如下:

图3 添加HLS DEMOSAIC2 IP核电路连接

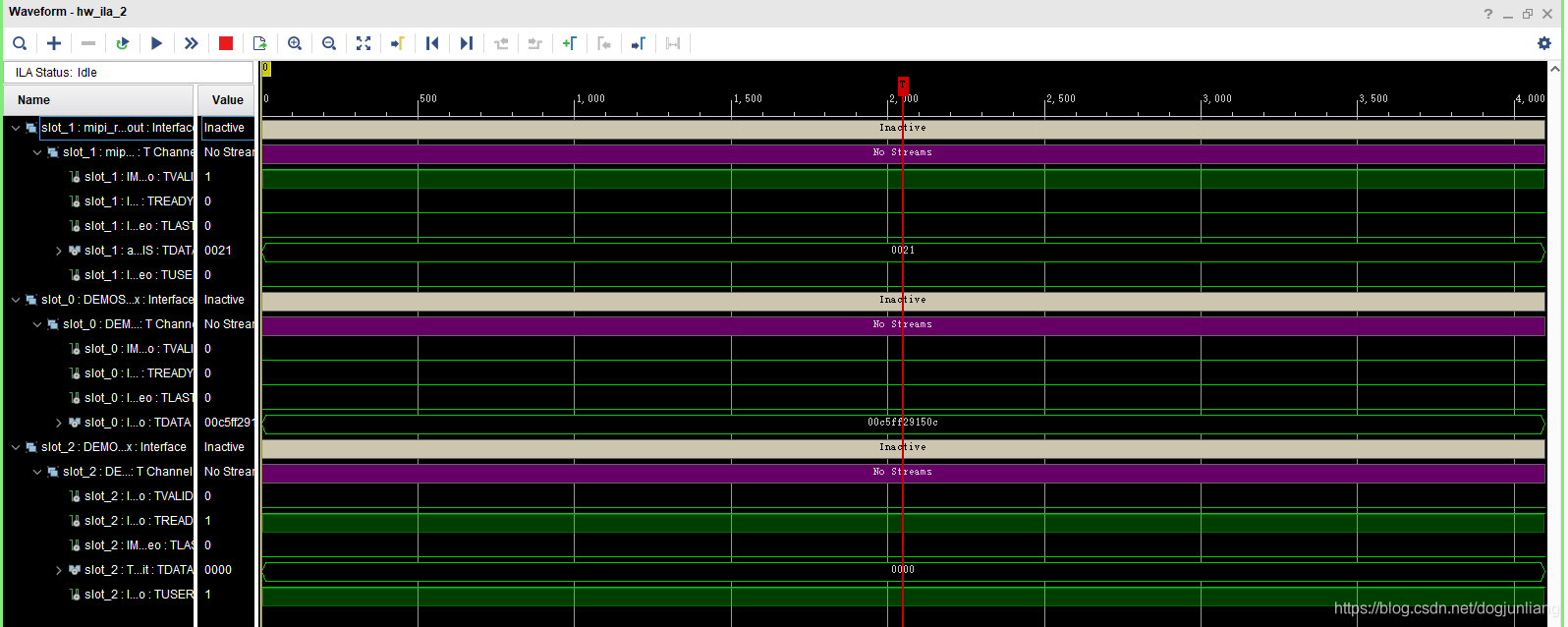

图4 添加HLS DEMOSAIC2 IP核板级波形

3.2 解决方法

UG902 214页,增加RTL FIFO深度,对输出的hls::Stream类型的数据进行约束,约束成Stream类型FIFO的深度选择合适。具体为什么要这样操作,本人目前还未找到原因,有想法的欢迎留言!!!

4. AXIStream与Video类型接口之间的转换

4.1 问题描述

两个AXIStream接口类型的IP核之间有时候需要加入一个Video(具有HS\VS)接口的IP核,这就需要将AXIStream类型的数据转换为Video类型,通过Video接口的IP核之后,又要将Video接口转换为AXIStream,以下是其中一种解决方案。

4.2 解决方案

AXIStream类型的数据流时钟大于PCLK;

AXIStream to Video IP核选择异步模式,FIFO的深度为8192;

Video to AXIStream IP核选择异步模式,FIFO的深度为8192;

VTC的FULL FRAME的W和H要配置、ACTIVE的W和H要和输入Video的格式相同,否则AXIStream to Video IP无法锁定。

审核编辑:汤梓红

-

接口

+关注

关注

33文章

8597浏览量

151150 -

配置

+关注

关注

1文章

188浏览量

18382 -

HLS

+关注

关注

1文章

129浏览量

24113

发布评论请先 登录

相关推荐

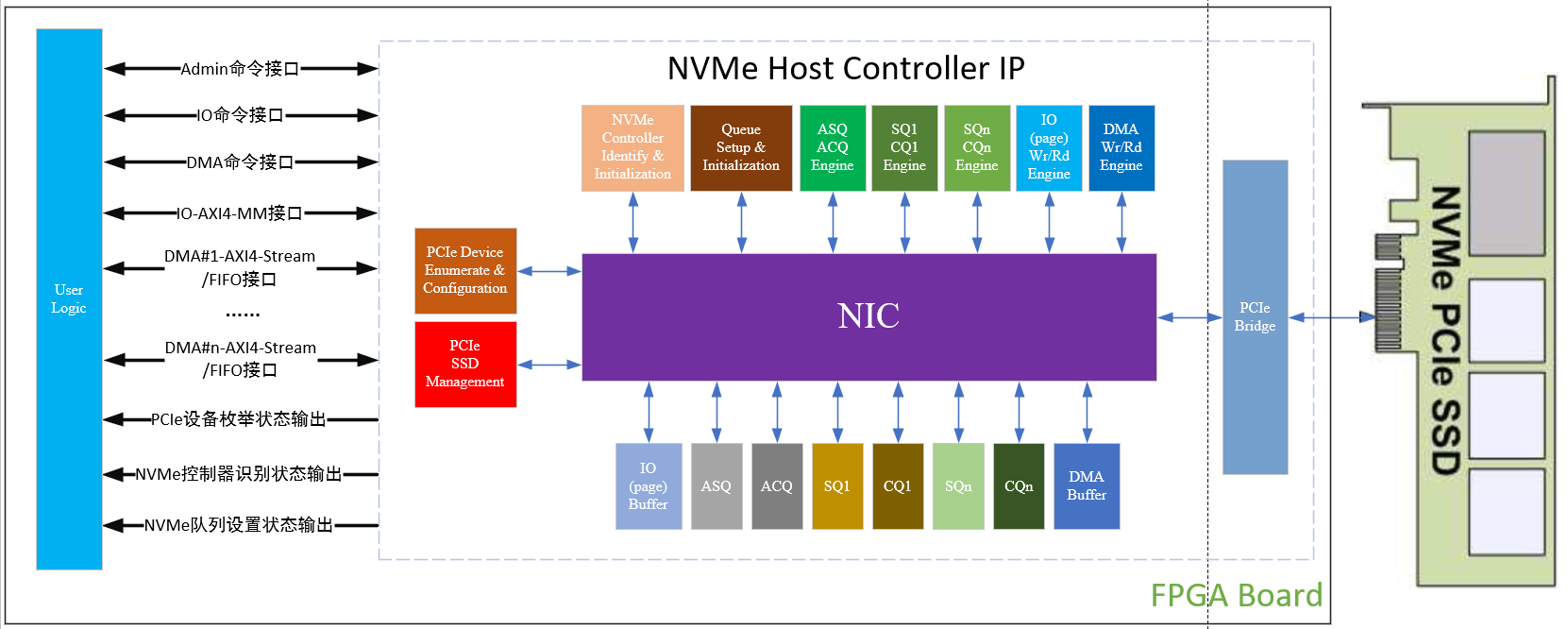

芯驿电子 ALINX 推出全新 IP 核产品线,覆盖 TCP/UDP/NVMe AXI IP 核

AMBA AXI4接口协议概述

Xilinx NVMe AXI4主机控制器,AXI4接口高性能版本介绍

一种在HLS中插入HDL代码的方式

基于TI Sitara系列AM5728工业开发板——FPGA视频开发案例分享

关于FPGA IP核

Xilinx FPGA NVMe主机控制器IP,高性能版本介绍应用

Xilinx高性能PCIe DMA控制器IP,8个DMA通道

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

HLS IP核AXI Stream接口问题汇总

HLS IP核AXI Stream接口问题汇总

评论