注:本文转自赛灵思中文社区论坛,源文链接在此。本文原作者为XILINX工程师。

以下为个人译文,仅供参考,如有疏漏之处,还请不吝赐教。

本篇博文是面向希望学习使用 Vivado 进行 FPGA 设计输入的新手的系列博文第一讲。

这些实践旨在为用户提供快速入门指导,帮助其简要了解工具流程原理。我们选择了一项非常简单的设计,便于读者理解流程中的不同步骤。

这些实践将按如下顺序展示:RTL 流程、基于 IP 的流程、基于 HLS 的流程、基于 IP integrator 的流程,最后是混用前述流程创建设计。

第一项实践是 RTL 流程。 每个步骤都包含截屏,以便用户自行尝试时参考。

步骤如下:

1.调用 Vivado。

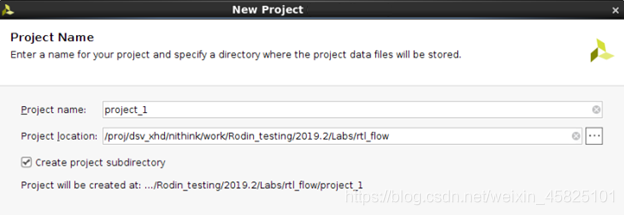

2.用户提供自己选择的工程名称(该工具使用的默认工程名称为 project_1),并提供工程创建路径,然后单击“下一步 (Next)”。

3.默认情况下,该工具会选中“选择 RTL 工程 (Select RTL Project)”,然后单击“下一步 (Next)”。

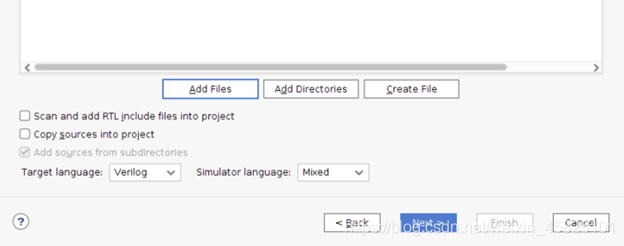

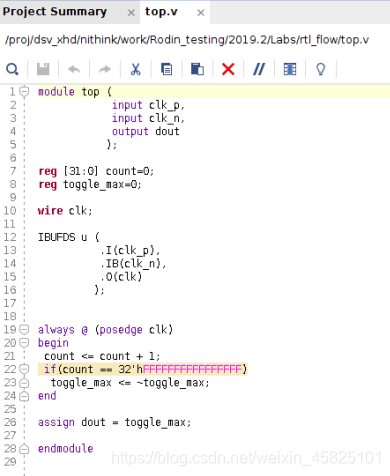

4. 该工具会提示您选择“Add Sources”以添加源文件。选择“添加文件 (Add Files)”,然后提供此处随附的 RTL 文件 (top.v)。

单击“下一步 (Next)”。

以下提供了 RTL 的详细信息:

RTL 用于描述自由运行的简单 32 位计数器。当该计数器达到其最大值时,就会翻转触发器。此触发器连接到输出。

这样会使用另一个缓冲器 (IBUFDS) 来创建时钟差分对,其输出将在设计中使用。在下一节中,我们将讲解为何使用此缓冲器。

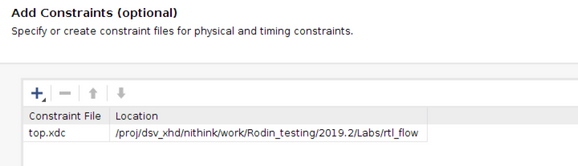

5. 您将看到“添加约束 (Add Constraints)”对话框,其中包含“添加 (Add Files)”选项。

选择“Add Files”,提供此处随附的 top.xdc,然后单击“Next”。

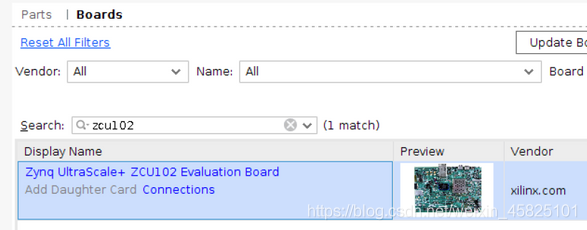

6.单击开发板选项卡,搜索 zcu102,然后选择此处显示的开发板(Zynq UltraScale+ ZCU102 评估板)。

单击“下一步 (Next)”。

7.在以下窗口中,单击“完成 (Finish)”。

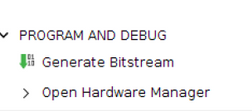

8.在左侧,您将看到“生成比特流 (Generate Bitstream)”按钮。

单击此按钮。

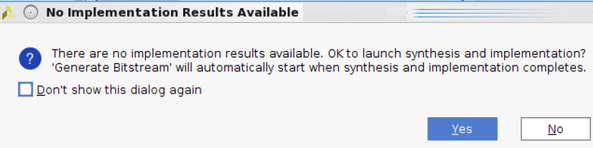

9.这样将显示如下提示:

单击“是 (Yes)”。这样将弹出另一条提示,要求您启动运行。单击“OK”。

这样就会触发综合 (Synthesis),然后实现 (Implementation),并且将生成比特流。

实践至此完成。

XDC 文件内容:

XDC 文件包含:

create_clock -name clk_p -period 8 [get_ports clk_p]

set_property LOC G21 [get_ports clk_p]

set_property LOC AG14 [get_ports dout]

set_property IOSTANDARD LVCMOS18 [get_ports dout]

set_property IOSTANDARD DIFF_HSTL_I_18 [get_ports clk_p]

使用 IBUFDS 的原因:

使用 IBUFDS 的原因是因为我们选择的开发板需要差分时钟。

每块开发板都有其自己特定的管脚 LOC 及其支持的系统时钟频率。

此开发板支持 300Mhz 和 125Mhz,因此我们使用 125Mhz 和与之对应的管脚 LOC。输出连接至 LED,其 LOC 为 AG14。最后 2 条语句用于指定端口的 IOSTANDARD。

审核编辑:符乾江

-

RTL

+关注

关注

1文章

385浏览量

59838 -

Vivado

+关注

关注

19文章

812浏览量

66633

发布评论请先 登录

相关推荐

每次Vivado编译的结果都一样吗

Vivado使用小技巧

LLC输入功率与什么有关系

差分放大电路同相输入和反相输入怎么看

如何判断同相输入端和反相输入端

单端输入和双端输入的区别是什么

与非门的闲置输入端如何处理

差模输入信号的概念、原理及应用

差分放大电路单端输入和双端输入的区别

PLC输入设备有哪些

详解Vivado非工程模式的精细设计过程

Vivado 设计输入纪事—RTL 设计输入

Vivado 设计输入纪事—RTL 设计输入

评论