1、综合-优化资源

当选择为none,综合器优化的最少,当选择为full时,综合器优化的最多,选择rebuilt时,工具自动选择一个折中的方案,对当前工程做优化。如果在rebuilt的选项不希望一些信号被优化,则可以调用原语进行约束。

对于模块,想保留该模块的层次结构

(* keep_hierarchy=“yes” )

对于信号,在实际使用中,最好作用于寄存器,有的wire即使约束,也会被优化。

( keep=“true” )

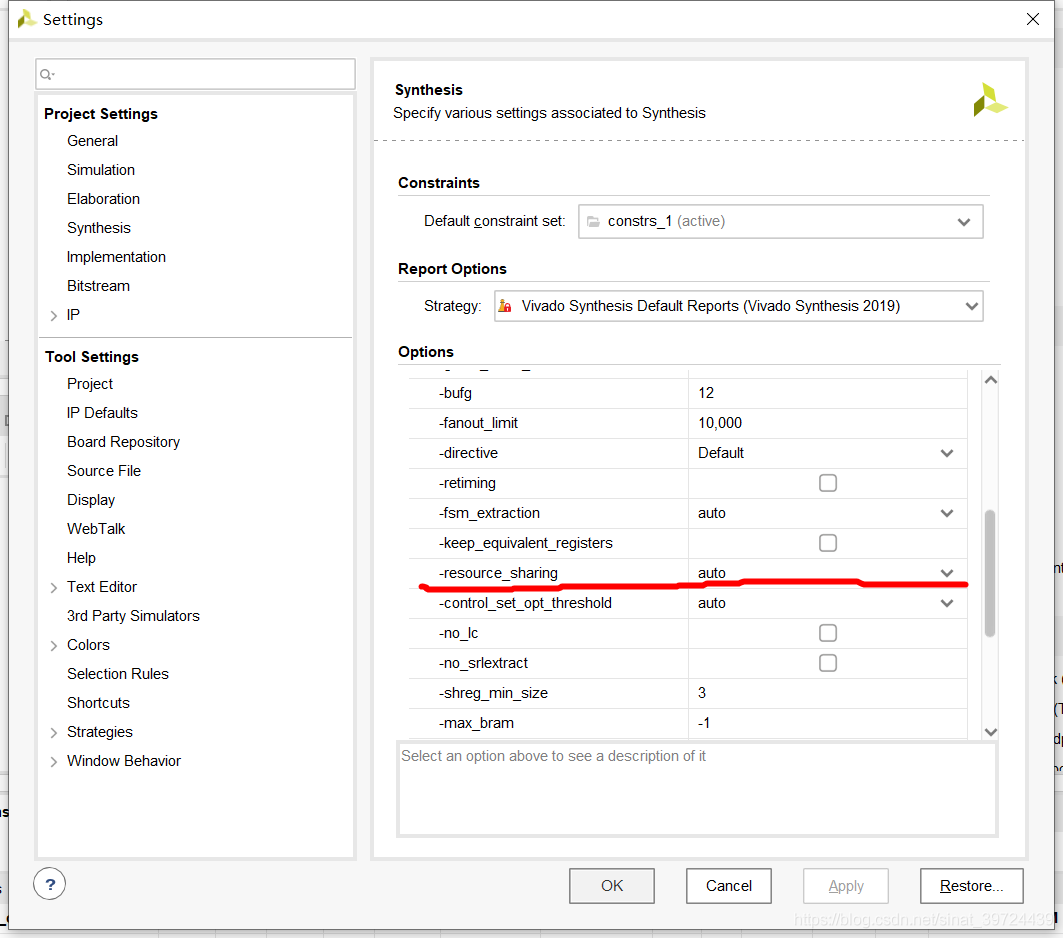

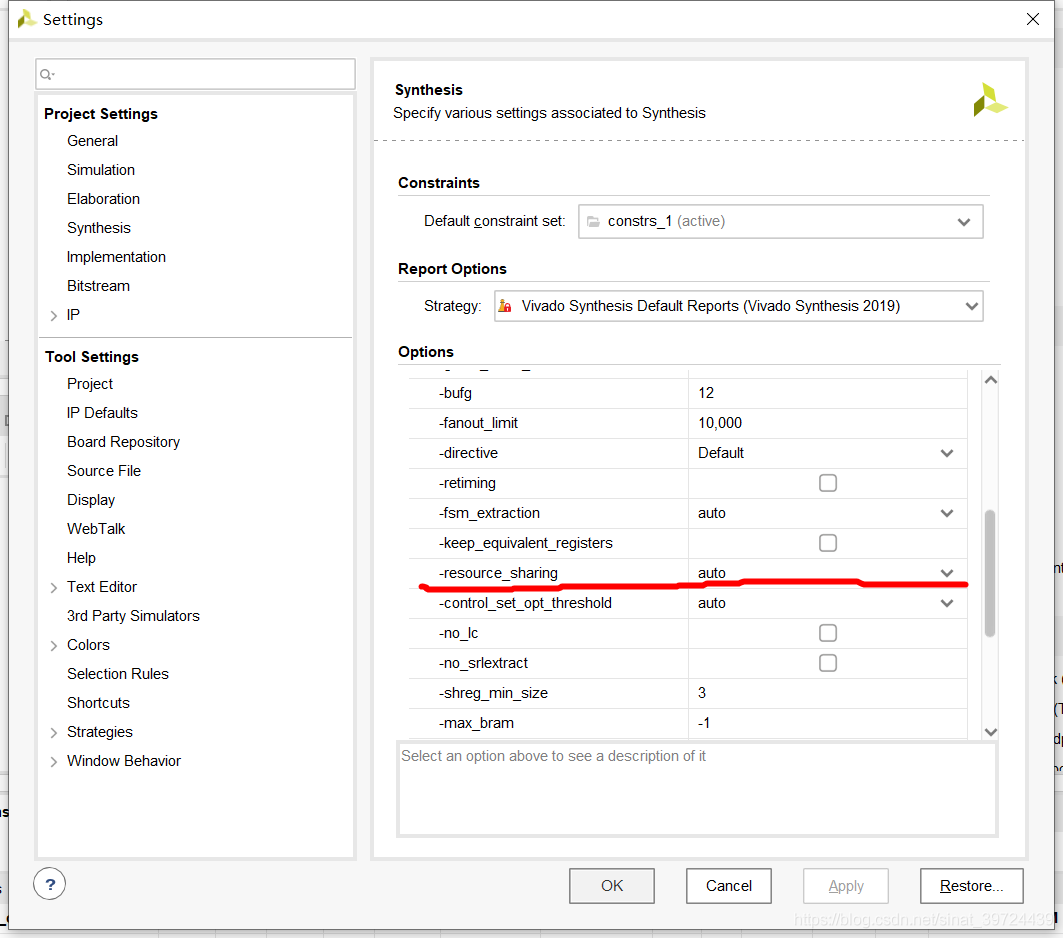

2、综合-资源共享

当选择为on时,使能资源共享,当选择为off时,关闭资源共享,当选择为auto时,综合器会根据时序的余量自动选择是否启动资源共享。

注意,此此选项只对当前代码中加减乘有影响。

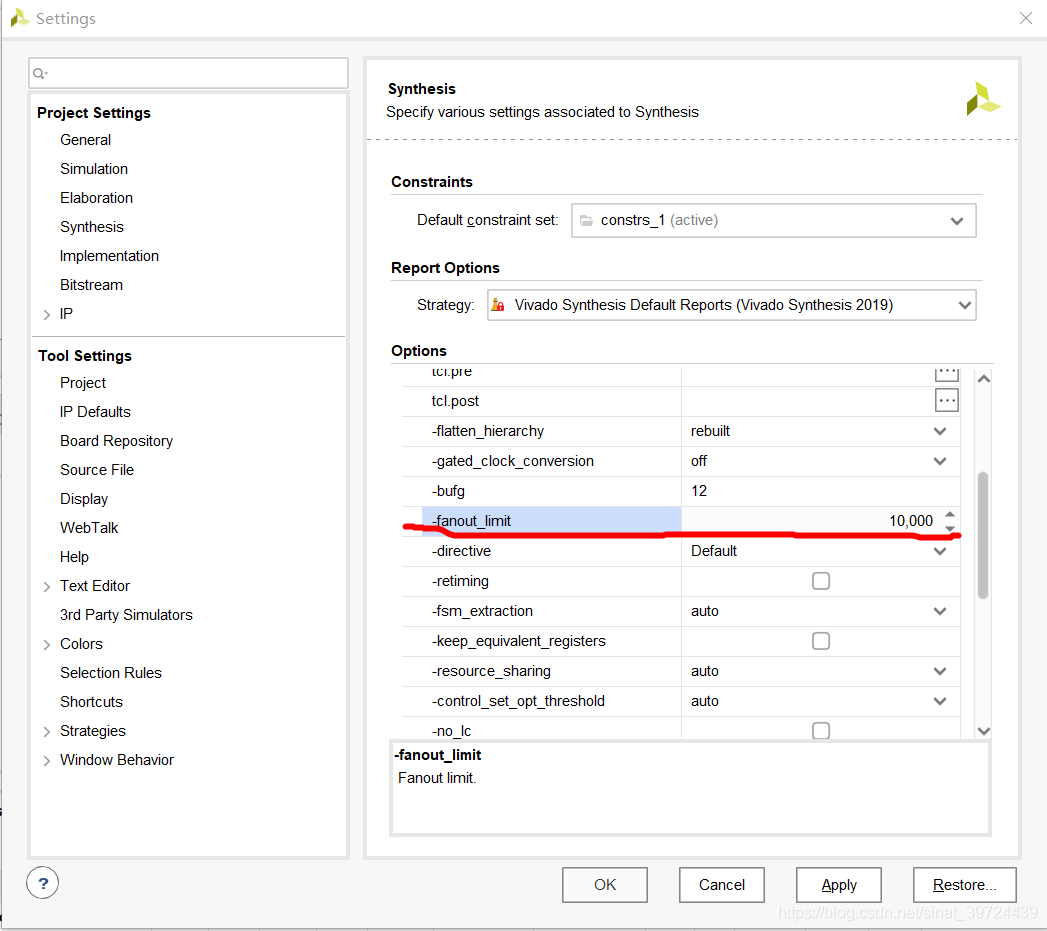

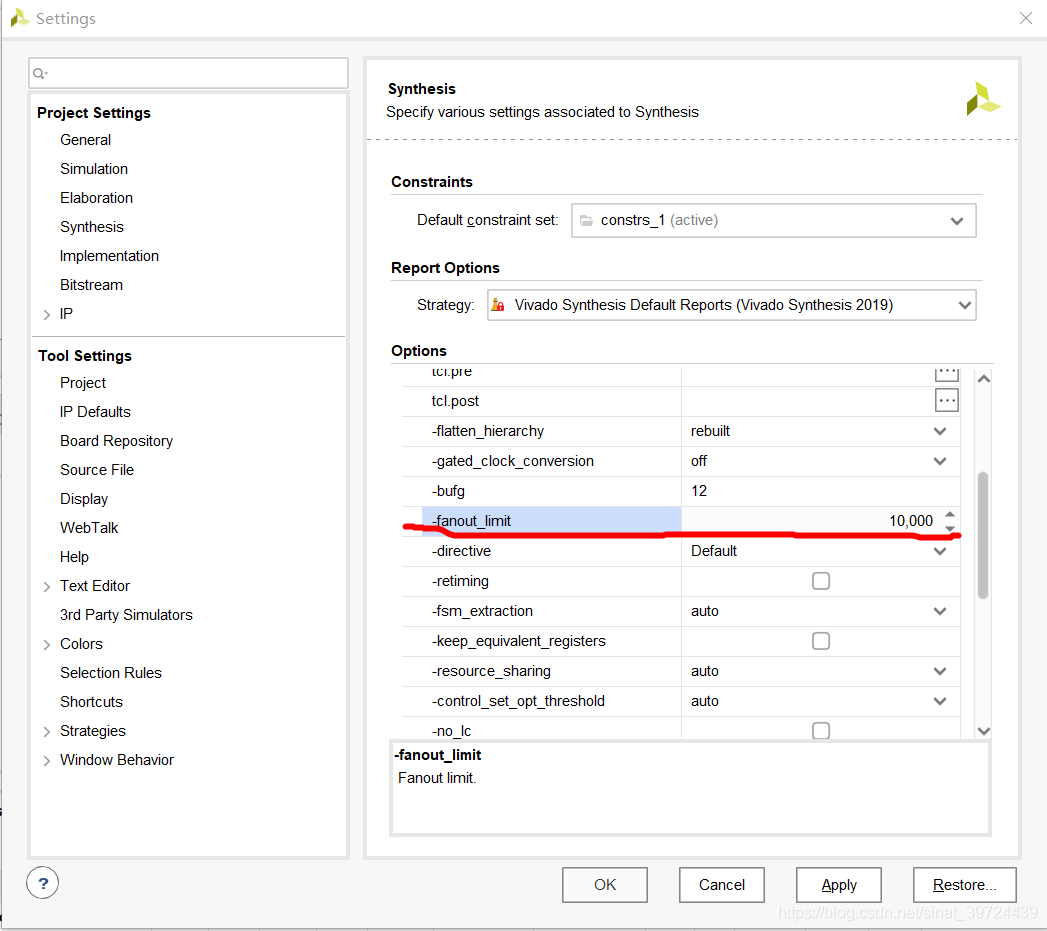

3、综合-扇出限制

默认是10000,这只是一个笼统的全局设置,对复位无效。

对于单一信号的扇出约束,使用约束

( max_fanout= *)

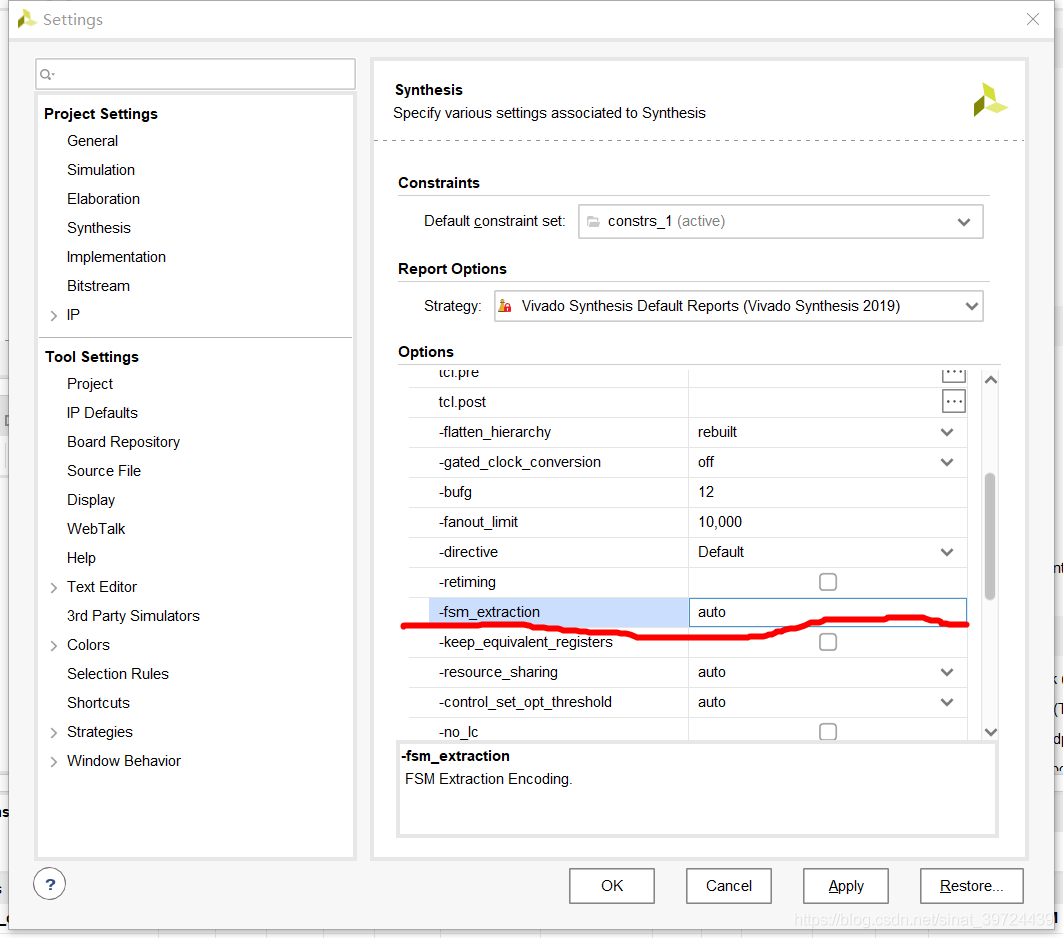

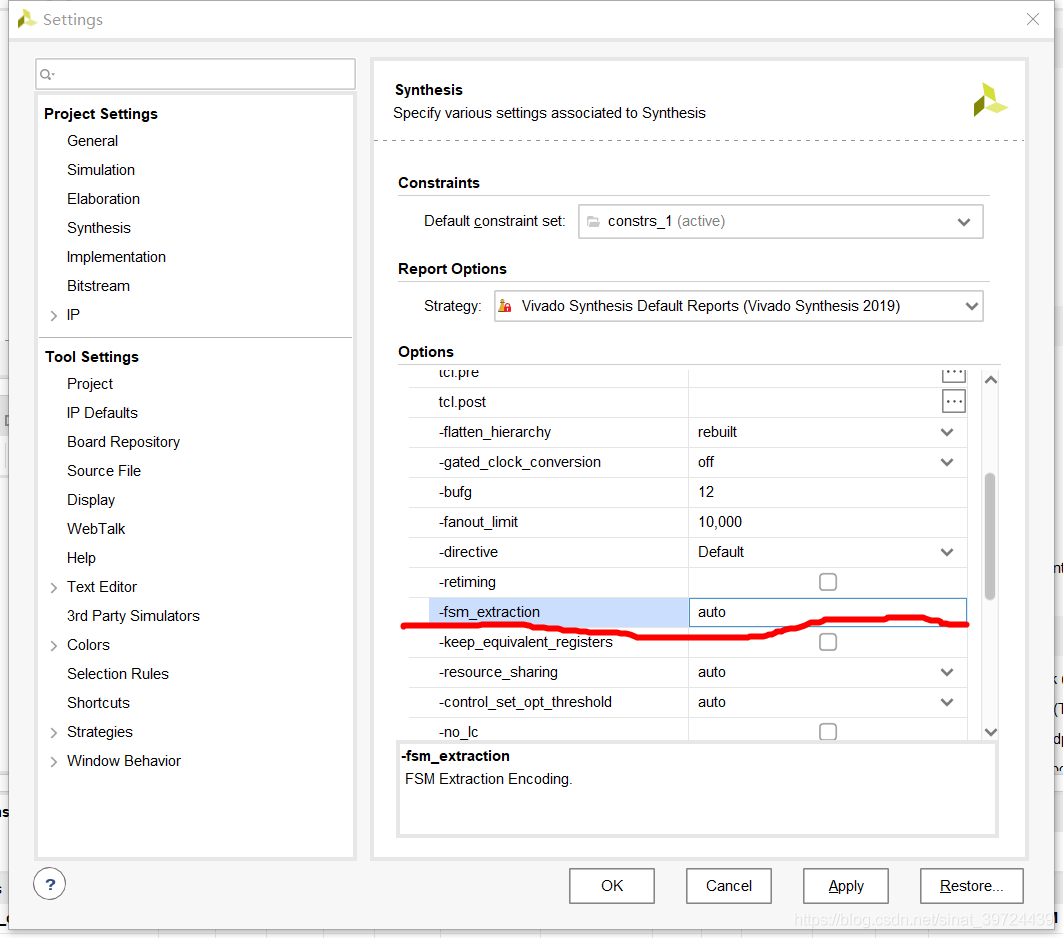

4、状态机的编码方式

当选择为auto时,综合器会根据当前的代码,自动选择最有的编码方式。

审核编辑:汤梓红

![]()

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

相关推荐

。今天给大家带来如何设置Termius。 Termius是一款功能强大的SSH终端工具,支持多种操作系统,包括Windows、Mac和Linux等。以下是关于如何实现Termius设置的内容: Termius基本

![的头像]() 发表于

发表于 12-18 15:22

•300次阅读

I Agree,然后点击 Next: 选择 Vivado HL System Edition(一般选择这个设计套件比较完整,它比 Vivado HL Design Edition 多了一个 System Generator for DSP with Mat

![的头像]() 发表于

发表于 11-16 09:53

•1329次阅读

AMD Alveo 加速卡使用有两种流程,AMD Vitis Software Platform flow 和 AMD Vivado Design Tool flow。比较常见的是 Vitis

![的头像]() 发表于

发表于 11-13 10:14

•216次阅读

很多FPGA工程师都有这种困惑,Vivado每次编译的结果都一样吗? 在AMD官网上,有这样一个帖子: Are Vivado results repeatable for identical

![的头像]() 发表于

发表于 11-11 11:23

•456次阅读

有时我们对时序约束进行了一些调整,希望能够快速看到对应的时序报告,而又不希望重新布局布线。这时,我们可以打开布线后的dcp,直接在Vivado Tcl Console里输入更新后的时序约束。如果调整

![的头像]() 发表于

发表于 10-24 15:08

•384次阅读

网关的设置规则涉及多个方面,包括硬件安装、网络连接、基本配置、高级配置以及安全设置等。以下是一篇关于网关设置规则的详细指南,旨在帮助用户正确配置和管理网关设备。

![的头像]() 发表于

发表于 09-30 11:48

•2390次阅读

从综合角度看,Vivado 2024.1对SystemVerilog和VHDL-2019的一些特性开始支持。先看SystemVerilog。

![的头像]() 发表于

发表于 09-18 10:34

•992次阅读

Vivado 2024.1已正式发布,今天我们就来看看新版本带来了哪些新特性。

![的头像]() 发表于

发表于 09-18 10:30

•1497次阅读

Verilog与VHDL语法是互通且相互对应的,如何查看二者对同一硬件结构的描述,可以借助EDA工具,如Vivado,打开Vivado后它里面的语言模板后,也可以对比查看Verilog和VHDL之间的差异。

![的头像]() 发表于

发表于 04-28 17:47

•2596次阅读

,用户可直接在simulink下综合出网表和约束文件,打包至.dcp文件中,用户可在vivado下直接加载dcp文件调用模型。

4、直接在vivado中添加模型文件(推荐)。

Viv

发表于 04-17 17:29

Xilinx Vivado开发环境编译HDL时,对时钟信号设置了编译规则,如果时钟由于硬件设计原因分配到了普通IO上,而非_SRCC或者_MRCC专用时钟管脚上时,编译器就会提示错误。

![的头像]() 发表于

发表于 04-15 11:38

•5797次阅读

电缆隧道作为城市电力供应、信息传输和能源输送的重要通道,其安全和稳定性对城市的正常运行至关重要。因此,一个高效、智能的电缆隧道综合监控管理平台的规划设置就显得尤为关键。本文深圳鼎信智慧科技将详细探讨

![的头像]() 发表于

发表于 04-09 18:01

•541次阅读

将设置设计的输出路径,设置设计输出路径的步骤如下所示。 第一步:如图4.3所示,在“Vivado%”提示符后输入命令“set outputDir ./gate_Created_Data/top_output”。

发表于 04-03 09:34

•1827次阅读

要求

1.ISP路由器只能配置IP地址,之后不进行任何配置

2.内部整个网络基于192.168.1.0/24进行地址划分

3.R1/2之间启动OSPF协议,单区域

4.PC1-4自动获取IP地址

5.PC1不能telnetR1,PC1外的其余内网PC可以telnet

![的头像]() 发表于

发表于 03-21 11:43

•716次阅读

摘要:城市综合管廊的供配电系统设计多种多样,通过对综合管廊自用负荷的分析及安全运行的因素考虑,并结合综合管廊设计案例,简要总结综合管廊供配电

发表于 01-19 17:32

关于Vivado综合设置使用总结

关于Vivado综合设置使用总结

评论