随着5G、人工智能、物联网、汽车电子等新兴应用的崛起,ADC作为信号链核心的地位仍在提升。距离我们上一次挖掘ADC新品,已经过去了不少时日。每一次行业内新的ADC产品发布都能带给我们不少的惊喜,这一次也不会例外。

ADI ADC新品AD4134

AD4134,一款24位的4通道同步采样无混叠ADC,主要针对航空航天、医疗设备、工业自动化以及仪器仪表测量领域应用开发。该新品最大的特点就是能有效抑制ADC混叠频带附近的信号。

ADI ADC新品AD4134

AD4134,一款24位的4通道同步采样无混叠ADC,主要针对航空航天、医疗设备、工业自动化以及仪器仪表测量领域应用开发。该新品最大的特点就是能有效抑制ADC混叠频带附近的信号。

(图源:ADI)

首先看看它的抗混叠能力。AD4134采用了连续时间Σ-Δ(CTSD)调制方案,消除了一般设计里所需的位于Σ-Δ调制器之前的开关电容电路采样,放宽了对ADC输入驱动的要求。CTSD架构本身就能抑制ADC混叠频带附近的信号,并且不需要复杂的外部抗混叠滤波器。在AD4134高性能模式下,抗混叠抑制典型值高达102.5dB。

高抗混叠之外,它的其他关键性能也是毫无争议的行业一流。其失调误差漂移不超过0.9 µV/C,增益漂移不超过2ppm/℃,积分非线性为2ppm,在1kHZ的输入信号音下总谐波失真典型值为-120dB。这些特性使得系统性性能得到了大幅改善,在温度、压力、振动、冲击等各类传感器中都能发挥出出色的实力。

在AD4134的四个通道中,每个通道均有CTSD调制器和数字抽取与滤波路径,能同时对四个独立的信号源采样。每个信号测量支持391.5 kHz的最大输入带宽,四个信号测量之间实现了严密的相位匹配。

AD4134集成了异步采样速率转换器,能利用插值和重采样技术精准地控制抽取率,进而控制ODR。AD4134支持从0.01 kSPS到1496 kSPS的宽范围ODR频率,调整分辨率小于0.01 SPS。异步采样速率转换器不再需要将数字后端的高频低抖动主时钟路由到各ADC,因此可简化中等带宽数据采集系统的时钟分配要求。

AD4134还支持灵活且独立的数据接口,既可充当总线主机,也可充当从机,具有各种时钟选项,支持多种通信总线协议。而在封装上,器件采用8 mm×8 mm、56引脚引线框架芯片级封装。

TI ADC新品ADS7067

在推出了几款汽车类应用的同步采样ADC后,这一次TI最新推出的ADS7067是具有GPIO和SPI的八通道16位SAR ADC。

(图源:TI)

该ADC在保证了一流的同类产品性能的前提下,大幅减少了外部组件,对减小系统整体的尺寸有相当大的助力。ADS7067具有集成的无电容基准和基准缓冲器,因此无需较多的外部组件,其本身也只有1.62mm×1.62mm,可以大幅减小整体解决方案尺寸。

ADS7067本身也具备出色的交/直流性能,90dB的SNR,-100dB的THD,800kSPS的采样率能做到无延迟输出,同时在内部改善了失调电压和漂移。内置的失调电压校准功能,可在系统的宽工作范围内提高精度,可编程均值滤波器可实现更高的分辨率测量。ADS7067 的八个通道可以单独配置为模拟输入、数字输入或数字输出,以实现更小的系统尺寸,并简化混合信号反馈和数字控制的电路设计。

ADS7067具备增强型的SPI数字接口,拥有60MHz的高速,能够支持器件以较低的时钟速度实现高数据吞吐量。这种配置进一步简化了整个器件的布局并能降低成本。晶圆级芯片封装让这个新ADC能适应任何空间受限的应用。

小结

这两款新品一个显著抑制ADC混叠,一个大幅降低系统尺寸,反映出了ADC这个核心器件的发展方向,如何在大幅提高数据吞吐量和带宽的同时尽可能减小功耗和尺寸,是每一个ADC厂商都在攻克的课题。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADI

+关注

关注

146文章

45829浏览量

250621 -

ti

+关注

关注

112文章

7985浏览量

212600 -

adc

+关注

关注

98文章

6513浏览量

545037

发布评论请先 登录

相关推荐

低通抗混叠的频率选多少为好?

需要采集压电式加速度传感器产生的低频信号,1kHz以下,采用电荷放大器将电荷信号转成电压信号(几十mV),然后经过低通抗混叠,积分,和高通,再经过放大给AD采集,AD拟采用ADS8519的±10V

发表于 12-20 10:12

ADS7066有可编程滤波器,请问使用该滤波器时,是否可以简化设计抗混叠滤波的截止频率?

我看ADS7066有可编程滤波器,请问使用该滤波器时,是否可以简化设计抗混叠滤波的截止频率?是否会有像SD ADC一样的过采样效果?

例如,采样10KHz采样频率,设置过采样为16倍

发表于 11-25 07:29

为什么Δ-∑型ADC的前级仅需要简单的RC抗混叠滤波电路?

我想请教下,为什么Δ-∑型ADC的前级仅需要简单的RC抗混叠滤波电路,理论上它和SAR型ADC一样都是开关电容输入结构,应该对于输入端的电

发表于 11-18 08:19

驱动流水线型ADS5500 ADC的运放电路抗混叠RC阻容设计是否与SAR ADC一样的呢?

由于使用流水线型ADC ADS5500,驱动流水线型ADS5500 ADC的运放电路抗混叠RC阻容设计是否与SAR

发表于 11-18 07:22

用THS4522作为ADC的有源抗混叠滤波器可以吗?

做一个数据采集 用的是ads4522采集的信号为10M一下的宽带信号,ADS4522评估板推荐用THS4509作为ADC的驱动,不知我用THS4522作为ADC的有源抗混

发表于 09-10 07:41

图中红色框中是抗混叠电路,那么这个截止频率应该怎么计算?

上图是OPA189手册中推荐的一个电路,我的问题是图中红色框中是抗混叠电路,那么这个截止频率应该怎么计算,我一开始认为计算公式是:

f=1/{2*pi*(R1+R2)*C2},后来我发现那电容

发表于 08-13 07:38

使用OPA4192设计的抗混叠模拟滤波,软件仿真得到的截止频率与实际的不符是怎么回事?

使用OPA4192设计的抗混叠模拟滤波,使用软件仿真得到的截止频率是60k,但在实际电路中,-3dB点的频率是76k,这是什么原因导致的呀

发表于 08-02 09:43

求助,关于OPA2828设计抗混叠滤波器的疑惑求解

1、德州仪器信号链资料里面提到的设计抗混叠滤波器的阻带频率为Fs(采样率)-信号频率,根据ADC位数,设置它的阻带衰减;

而,TI precision labs

发表于 07-30 08:26

Q值恒定、可同时输出:低通、高通、带通的抗混叠滤波器电路

由于传感器、传输路径等因素的影响,使得视频信号混叠噪声信号,由于这些噪声信号的类型相当复杂,目前采用数字滤波方式,这需要大量的DSP芯片。Q值恒定、可同时输出:低通、高通、带通的抗混

发表于 04-24 22:51

避免高光谱成像数据中的光谱混叠问题

高光谱成像技术在农业、环境监测、医学诊断等领域具有广泛的应用前景。然而,光谱混叠是高光谱成像数据分析中常见的问题之一,它会影响数据的解释和应用。光谱混叠指的是不同光谱特征在成像中相互叠

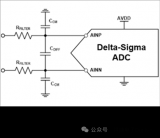

Δ-Σ ADC模数转换器抗混叠滤波器组件选择

低速 Δ-Σ ADC 通常需要一个简单的单极 RC 滤波器来减少混叠效应。对于差分信号,滤波器结构通常由两个滤波路径组成:一个差分滤波器(源自两个滤波器电阻 RFILTER 和差分电容器 CDIFF

继续挖掘ADC新品,抗混叠与降低尺寸再革新

继续挖掘ADC新品,抗混叠与降低尺寸再革新

评论