摘要

嵌入式硅锗在最近的技术节点中被应用于互补金属氧化物半导体中,以提高器件性能并实现扩展。本文发现硅锗表面相对于沟道的位置对功率因数校正阈值电压和器件可变性有显著影响。因此,嵌入式硅锗的凹槽蚀刻和沉积必须得到很好的控制。我们展示了器件对填充工艺的敏感性,并描述了用于优化外延控制的前馈和反馈技术。

介绍

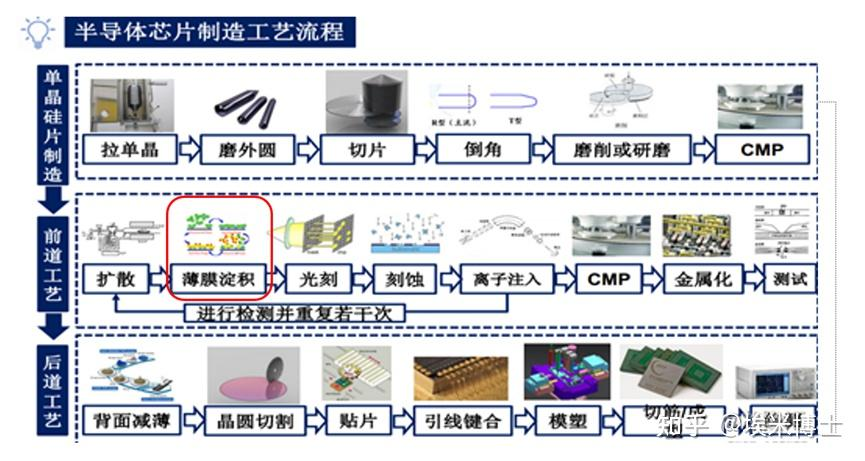

在进入制造业的最新CMOS技术节点,由于传统的栅极长度和厚度缩放不再提供在较低漏极电压(Vd)下较高饱和电流(Id,sat)所需的增益,因此越来越需要添加技术元素来提升器件性能。这里我们指的是诸如应力工程、激光退火、高k电介质和金属栅极等技术。在本文中,我们讨论了嵌入式硅锗(eSiGe)的应用,它是应力工程的一种形式,也是提高pFET器件性能的一种非常有效的方法。我们表明,应该很好地控制凹槽反应离子蚀刻(RIE)和外延层厚度,以避免pFET阈值电压(Vth)可变性的显著增加。

技术描述

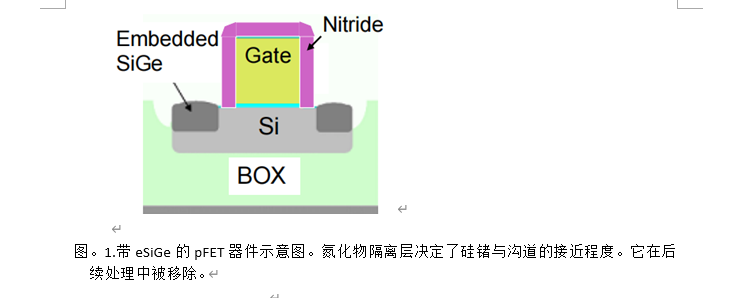

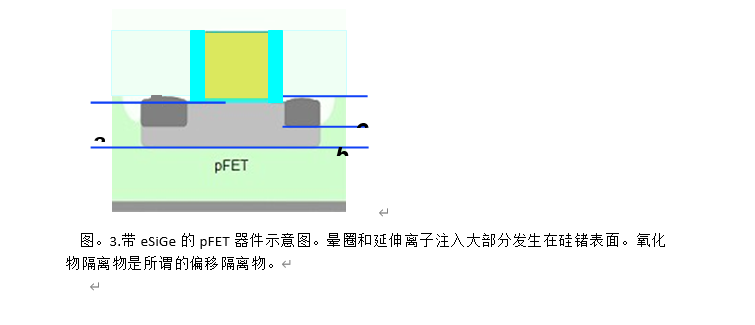

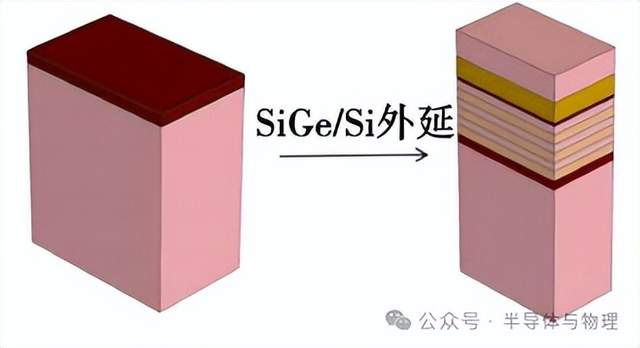

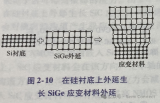

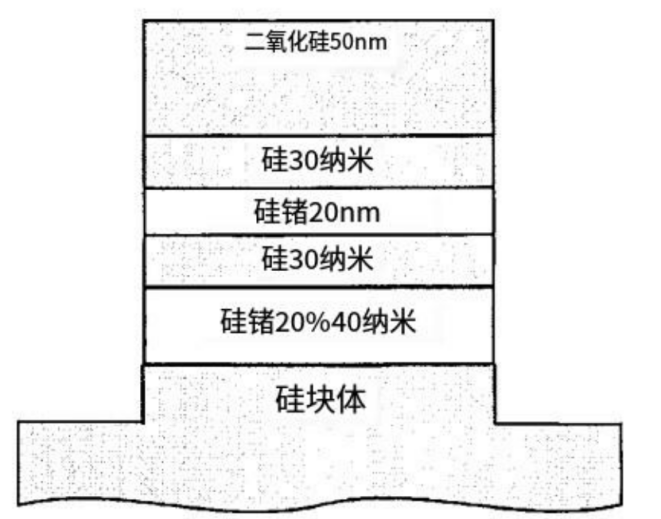

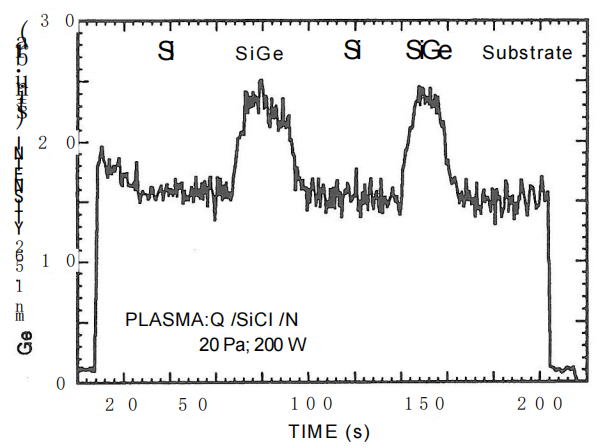

在SOI技术中,活性硅位于所谓的掩埋氧化层上,而氧化层又位于硅片上。在定义栅极之后沉积硅锗。首先,用氮化物层覆盖表面,该氮化物层在pFET器件的源极/漏极区上方开口。随后,我们将开口区域中的硅蚀刻到指定的深度,然后选择性地沉积硅锗。我们使用使用硅烷的传统技术,其中硅锗不在氮化物上生长。氮化物还充当限定硅锗接近沟道的隔离物。 在硅锗外延之后,氮化物被选择性地去除,并且处理按照常规继续,在本例中,这意味着栅极-侧壁间隔物以及n和p晕圈和延伸注入的序列。在SiGe沉积之后,但是在去除氮化物隔离物之前,器件的横截面显示在图1中。

设备灵敏度

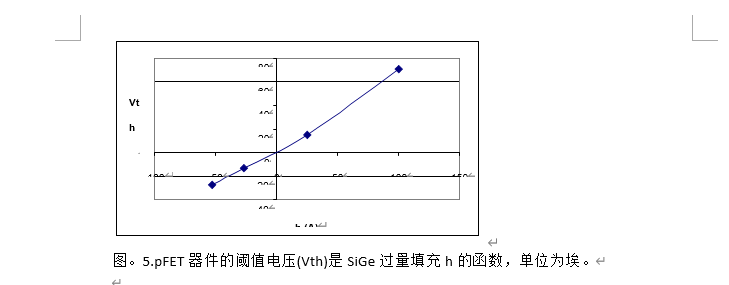

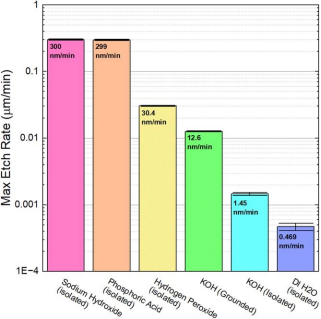

图4显示了在确定硅锗表面相对于沟道的位置时要考虑的尺寸。过量填充h是硅锗表面的高度和沟道的高度之差。当我们谈论过满h时,我们通常指的是在线计量所用宽垫片上测量的高度。器件灵敏度如图2所示。5.此处显示的数据来自分割批次,其中通过改变沉积时间,硅锗沉积厚度在15纳米范围内变化。正如预期的那样,阈值电压随着硅锗高度的增加而增加,在我们的情况下约为每纳米6 mV。

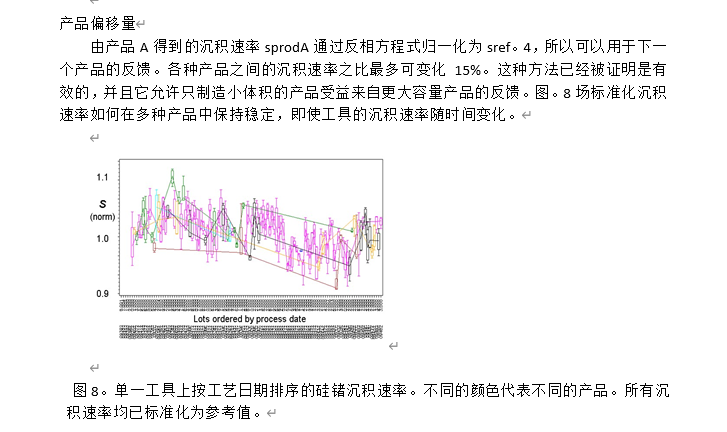

如上所述,这种先进过程控制(APC)方法,通过其反馈和前馈的结合,将改善填充控制。如果我们比较两种技术,使用相同的工具进行RIE和外延,其中一种使用传统的工具控制,没有运行到运行的反馈其次,使用上述方法,我们发现一个显著的差异。与常规控制工艺相比,使用反馈,沉积层的标准偏差降低了30%。

结论

本文发现功率场效应晶体管的阈值电压强烈依赖于嵌入硅锗的沉积厚度。这既是因为硅锗接近沟道,也是因为它对离子注入的影响。为了最小化器件可变性,我们采用前馈和反馈技术,使硅锗表面与输入SOI厚度紧密匹配。所用的APC技术应用于多种产品,通过包含沉积速率之间的已知比率来说明差异。

审核编辑:汤梓红

-

CMOS

+关注

关注

58文章

5710浏览量

235421 -

电流

+关注

关注

40文章

6850浏览量

132112 -

半导体

+关注

关注

334文章

27293浏览量

218106

发布评论请先 登录

相关推荐

SiGe与Si选择性刻蚀技术

选择性沉积技术介绍

一文详解半导体薄膜沉积工艺

湿法蚀刻的发展

源漏嵌入SiGe应变技术简介

基于光谱共焦技术的PCB蚀刻检测

通信——通过表面电荷操纵控制锗的蚀刻

关于两种蚀刻方式介绍

流量控制器在半导体加工工艺化学气相沉积(CVD)的应用

影响pcb蚀刻性能的五大因素有哪些?

锗化硅(SiGe)和硅(Si)之间的各向同性和选择性蚀刻机制

半导体资料丨氧化锌、晶体硅/钙钛矿、表面化学蚀刻的 MOCVD GaN

Si/SiGe多层堆叠的干法蚀刻

详解SiGe的蚀刻和沉积控制

详解SiGe的蚀刻和沉积控制

评论