摘要

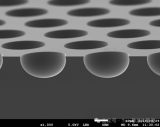

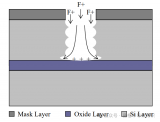

一种形成介电间隔物的方法,包括提供衬底,文章全部详情:壹叁叁伍捌零陆肆叁叁叁该衬底包括具有第一多个栅极结构的第一区域和具有第二多个栅极结构的第二区域和至少一种含氧化物材料或含碳材料。在第一区域上方形成厚度小于存在于第二区域中的含氮化物层的厚度的含氮化物层。在第一多个栅极结构和第二多个栅极结构上由含氮化物层形成介电间隔物。

背景

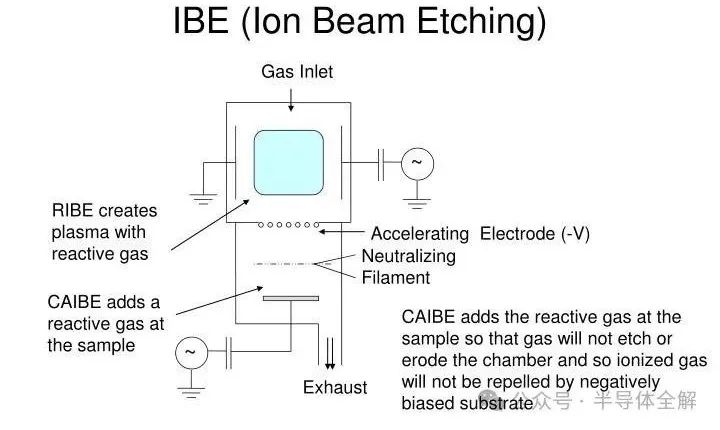

本公开涉及半导体结构和器件。更具体地,本公开涉及在半导体器件的制造中采用的蚀刻工艺。

为了能够制造出比目前可行的更高集成密度的集成电路 (IC),例如 10 个存储器、逻辑和其他设备,必须找到进一步缩小场效应晶体管 (FET) 尺寸的方法,例如金属氧化物半导体场效应晶体管 (MOSFET) 和互补金属氧化物半导体 (CMOS)。缩放通过缩小设备的整体尺寸和工作电压同时保持设备的电气特性来实现紧凑性并提高设备的工作性能。蚀刻工艺正在不断改进,以满足半导体器件规模增加 20 倍的需求。

总结

提供了一种形成介电栅极侧壁间隔物的方法,其中提供介电栅极侧壁间隔物的氮化物材料层的蚀刻速率通过控制在形成介电栅极侧壁间隔物的蚀刻工艺期间存在的氧化物的量来调整. 在一个实施例中,形成介电间隔物30的方法包括提供衬底,该衬底包括具有第一多个栅极结构的第一区域和具有第二多个栅极结构和至少一种含氧化物材料的第二区域。

详细说明

本文公开了要求保护的结构和方法的详细实施例;然而,应当理解,所公开的实施例仅仅是可以以各种形式体现的所要求保护的结构和方法的说明。此外,结合各种实施例给出的每个示例旨在是说明性的,而不是限制性的。此外,附图不一定按比例绘制,某些特征可能被夸大以显示特定组件的细节。

审核编辑:符乾江

-

半导体

+关注

关注

334文章

27476浏览量

219574 -

刻蚀

+关注

关注

2文章

189浏览量

13140

发布评论请先 登录

相关推荐

芯片湿法刻蚀方法有哪些

如何提高湿法刻蚀的选择比

光束均匀性的重要性及针对光束均匀性测试的解决方案

用于光波导系统的均匀性探测器

湿法刻蚀步骤有哪些

晶圆表面温度对干法刻蚀的影响

改善刻蚀均匀性的技术

改善刻蚀均匀性的技术

评论