没有任何寄存器逻辑,RTL设计是不完整的。RTL是寄存器传输级或逻辑,用于描述依赖于当前输入和过去输出的数字逻辑。

在异步计数器中,时钟信号不由公共时钟源驱动。如果LSB触发器的输出作为后续触发器的输入,则设计是异步的。异步设计的主要问题是由于级联,触发器的累积时钟到q延迟。由于存在小故障或尖峰问题,ASIC/FPGA设计中不建议使用异步计数器,甚至此类设计的时序分析也非常复杂。

所以接下来只介绍一种计数器

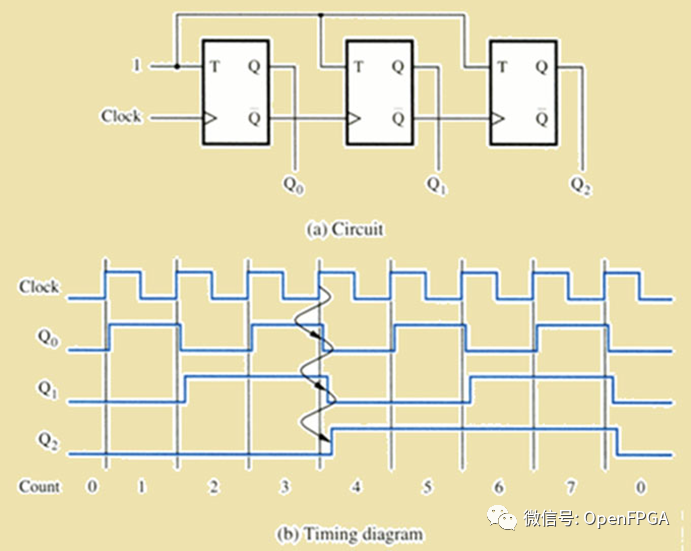

纹波计数器是一个异步计数器,如图5.33所示。如逻辑图所示,所有触发器均为正边缘触发,LSB寄存器从主时钟源接收时钟。LSB触发器的输出作为下一级的时钟输入。

图5.33三位纹波计数器逻辑图

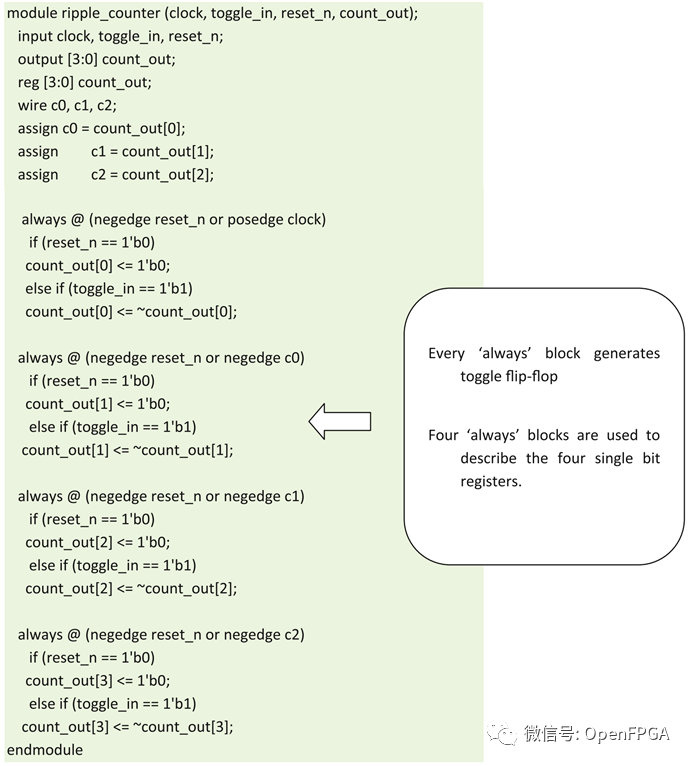

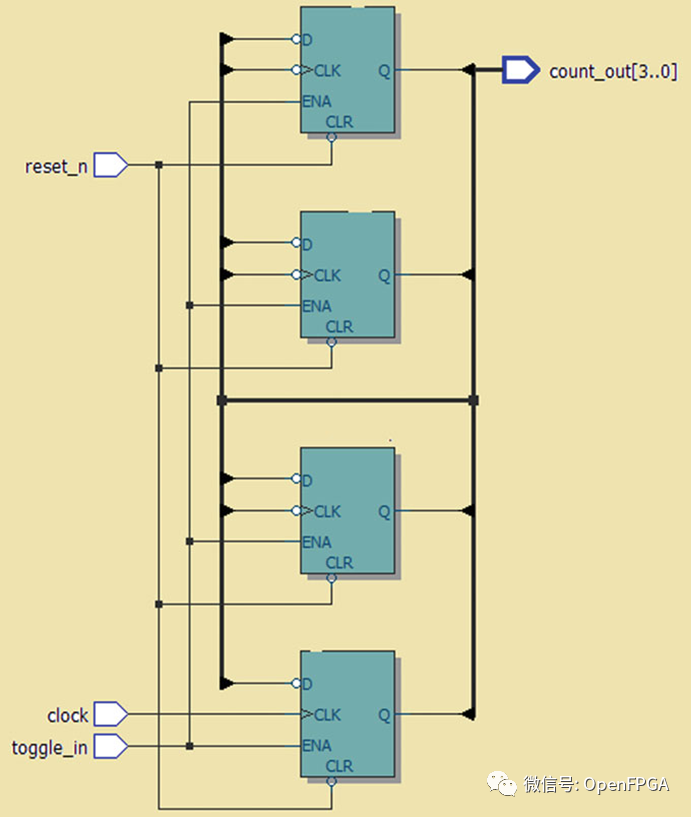

四位纹波递增计数器的Verilog RTL如例5.18所示。综合逻辑如图5.34所示。

示例5.18四位纹波递增计数器的Verilog RTL

图5.34四位纹波递增计数器的综合逻辑

内存模块设计

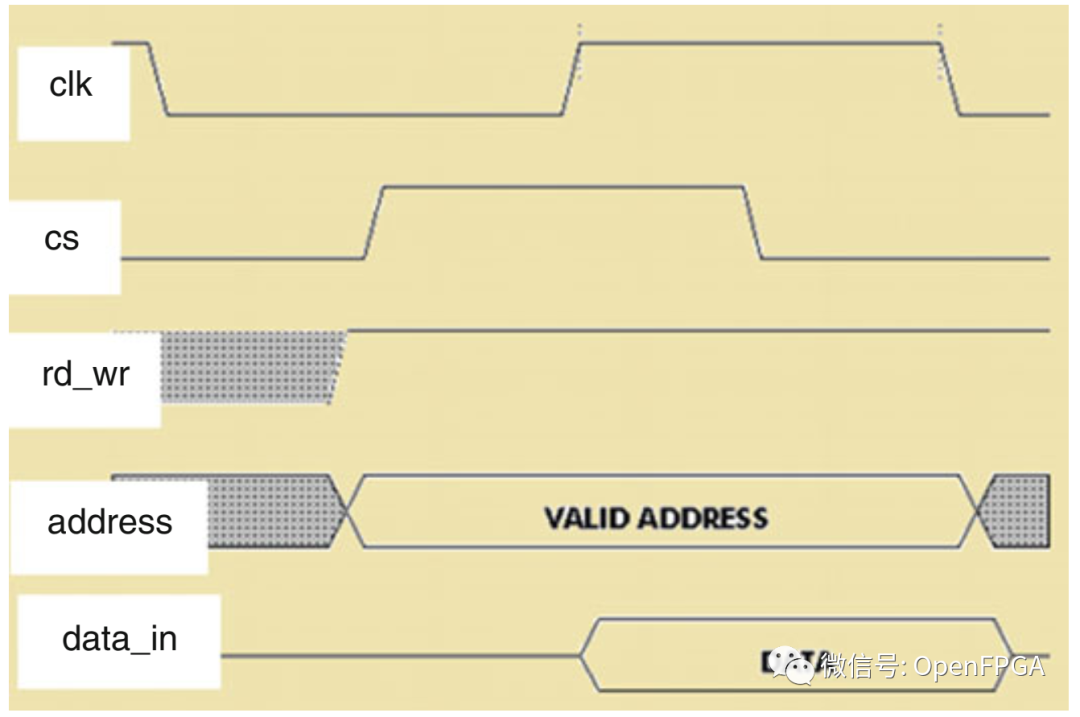

在大多数ASIC/FPGA设计和基于SoC的设计中,存储器用于存储二进制数据。存储器可以是ROM、RAM、单端口或双端口类型。本节的目的是描述基本的单端口读写存储器。时序如图5.35所示。

如时序所示,读写操作由“rd_wr”控制,如果“cs”为高电平,则在时钟信号“clk”的正边缘对数据进行采样。地址输入由总线“address”描述。

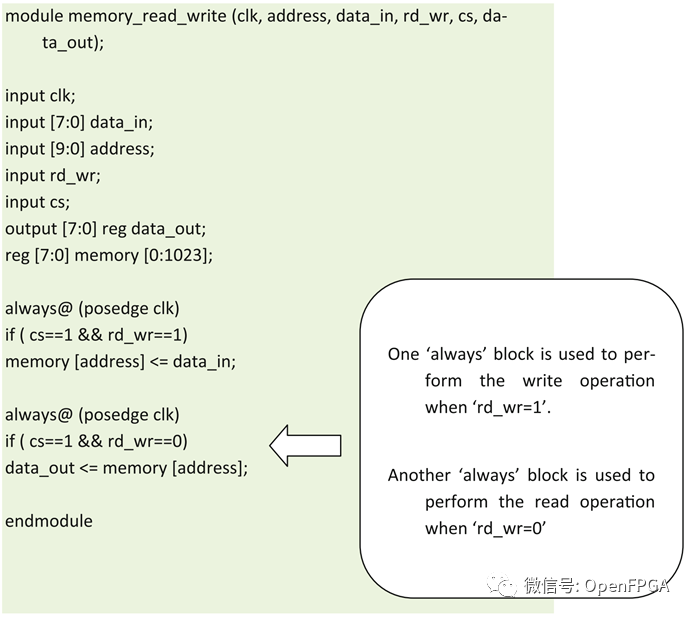

单端口读写存储器的Verilog RTL如例5.19所示。

图5.35存储器的时序

示例5.19读写存储器的Verilog RTL

审核编辑:‘’

-

寄存器

+关注

关注

31文章

5355浏览量

120513 -

计数器

+关注

关注

32文章

2256浏览量

94641 -

触发器

+关注

关注

14文章

2000浏览量

61185

原文标题:Verilog时序逻辑硬件建模设计(五)异步计数器&总结

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

什么是时序分析?教你掌握FPGA时序约束

FPGA设计中的时序分析及异步设计注意事项

verilog描述异步置0,异步置1功能的D触发器

ASIC中的异步时序设计

Verilog HDL语言实现时序逻辑电路

如何使用Verilog-HDL做CPLD设计的时序逻辑电路的实现

异步设计之Verilog时序分析

异步设计之Verilog时序分析

评论