警告:

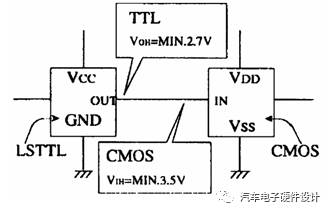

请注意LS和CMOS之间的高电平的不兼容性。

TTL: VOH min =2.7V

CMOS: VIH min =3.5V

潜在问题:

一个由TTL电路产生的高电平将被CMOS电路视为低电平。

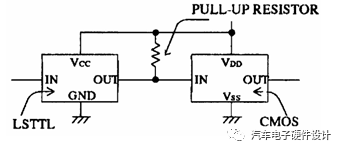

预防措施:

添加一个上拉电阻器来增加高电平。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

CMOS

+关注

关注

58文章

5735浏览量

236033 -

高电平

+关注

关注

6文章

153浏览量

21494

原文标题:LS 与CMOS高电平的不兼容性

文章出处:【微信号:QCDZYJ,微信公众号:汽车电子工程知识体系】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

TTL电平与信号降噪技术的区别

。 功耗 :TTL电路的功耗相对较高,因为它们使用双极型晶体管(BJT)。 速度 :TTL电路的速度相对较慢,因为晶体管的开关速度有限。 兼容性 :TTL电平与其他类型的逻辑电平(如CMOS

TTL电平与高电平信号的转换

在电子工程领域,信号电平的转换是一个常见的需求,尤其是在不同技术标准之间。TTL(晶体管-晶体管逻辑)电平和高电平信号是两种不同的电平标准,

BNC插头尺寸指南:标准尺寸与兼容性分析

德索工程师说道在电子设备连接领域,BNC插头作为一种常见的同轴电缆连接器,其尺寸规格和兼容性直接影响到设备的正常运行与连接效果。对于工程师和相关技术人员而言,深入了解BNC插头的尺寸标准与兼容性至关重要。

EE-313:28x28 MQFP和LQFP封装之间的焊盘模式兼容性

电子发烧友网站提供《EE-313:28x28 MQFP和LQFP封装之间的焊盘模式兼容性.pdf》资料免费下载

发表于 01-07 14:22

•0次下载

Testin云测中标哈尔滨银行兼容性测试项目

近日,Testin云测成功中标哈尔滨银行手机银行APP和手机银行5.0版本升级兼容性测试服务项目!此次中标不仅展现了Testin云测在兼容性测试方面的技术实力,也体现了深度服务客户、持续创新的承诺。

高电平输入和低电平输入是什么意思

在现代电子系统中,数字电路扮演着至关重要的角色。这些电路处理的是二进制信号,即由逻辑“1”和逻辑“0”组成的信号。这些逻辑状态通常通过电压水平来表示,其中高电平代表逻辑“1”,低电平代表逻辑“0

芯片引脚悬空是高电平还是低电平

受到周围电路环境和噪声的影响,表现出随机性。在一些情况下,引脚悬空可能会被视为高电平或低电平,但这并不是绝对的,而是取决于具体的电路设计和环境。 其次,对于某些芯片来说,其内部可能集成了上拉电阻或下拉电阻,这些

高电平和低电平输入有什么区别

在数字电子学中,高电平和低电平是两种基本的信号状态,它们分别代表二进制数字1和0。这两种电平状态在数字电路设计、通信和计算机系统中扮演着至关重要的角色。 高电平和低

risc-v的mcu对RTOS兼容性如何

RISC-V的MCU对RTOS(实时操作系统)的兼容性主要取决于多个因素,包括RTOS的版本、RISC-V指令集的实现、以及芯片制造商提供的支持。以下是关于RISC-V的MCU对RTOS兼容性的一些

发表于 05-27 16:26

CMOS电路什么输入为高电平 cmos门电路输出电平判断

半导体)管道组成。在CMOS电路中,输入信号的高和低电平取决于输入信号的电压和电路中的配置。 对于CMOS门电路来说,判断输出电平的关键是输入电压。在理想的情况下,当输入电压为

cmos电平与ttl电平如何转换 怎么判断ttl电路高低电平

的CMOS电平一般分为逻辑高电平(High Level)和逻辑低电平(Low Level)。CMOS电平

LS和CMOS之间高电平的不兼容性

LS和CMOS之间高电平的不兼容性

评论