“ 此小节中介绍Verilog HDL中提供的常用预编译命令:`define ;`timescale ;`include ;`ifdef 、`elsif、`endif 。”

01、时间尺度`timescale

`timescale命令用于在文件中指明时间单位和时间精度,通常在对文件进行仿真时体现。EDA工具可以支持在一个设计中可根据仿真需要在不同模块里面指定不同的时间单位。如模块A仿真的时间单位为皮秒(ps),模块B仿真的时间单位为纳秒(ns)。使用`timescale命令语句格式如下:

`timescale 《时间单位》 / 《时间精度》

使用时注意《时间单位》和《时间精度》必须是整数,且时间精度不能大于时间单位值。

其中时间单位是定义仿真时间和延迟时间的基准单位;时间精度是定义模块仿真时间的精确程度的,又被称为取整精度(在仿真前,被用来对延迟的时间值进行取整操作,例程中会对此进行介绍)。如果在同一个设计中,出现多个`timescale命令,工具会采用最小的时间精度值来决定仿真的时间单位。

下面举例说明`timescale用法。

`timescale 1ns / 1ps:此命令已定义模块中的时间单位为1ns,即仿真模块中所有的延迟时间单位都是1ns的整数倍;定义了模块的时间精度为1ps,即仿真模块中延迟单位可以指定到小数点后3位,小数超过3位会进行取小数点后3位的操作。

02、宏定义`define

在设计中,为了提高程序可读性和简化程序描述,可以使用指定的标识符来代替一个长的字符串,或者使用一个简单的名字来代替没有含义的数字或者符号,此时需使用到宏定义命令`define。它的使用形式如下:

`define signal(宏名) string(宏内容)

在设计中进行了以上声明后,在与编译处理时,在此命令后程序中所有的signal都替换成string,此过程称为“宏展开”。具体使用方法如下:

例1 :`define LENGTH 16

reg[ `LENGTH–1 : 0 ] writedata;//即定义reg[15:0]writedata;

例2 :`define expression a+b+c

assign data = `expression + d ; // 经宏展开之后assign //add_data = a+b+c+d;

例3 :`define A a+b

`define B c+`A

assign data = `B ; // 即data = c + a + b;

03、文件包含指令`includ

和C语言中声明头文件很类似。其一般形式为:`include “文件名”

例:

文件para.v中有一个宏定义 `defineA 2+3

在test.v文件中可以直接调用

`timescale1ns/1ps`include"para.v"`include"para2.v"module test(input wire clk,outputreg[7:0]result);always@(posedge clk)beginresult<= `A+10;endendmodule

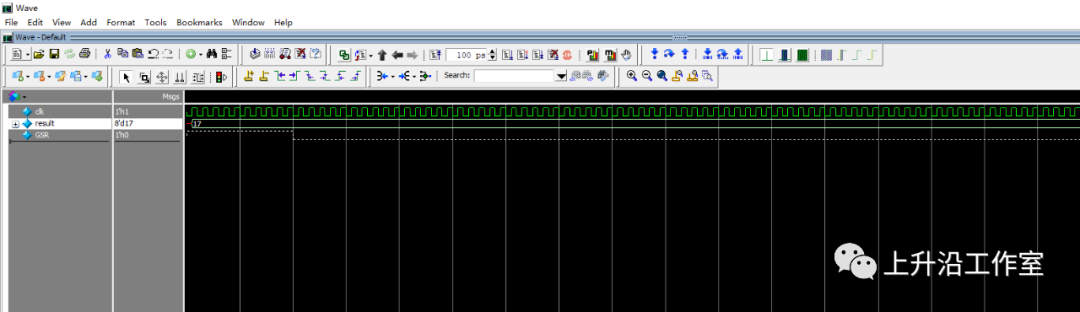

仿真结果如下:

关于“文件包含的几点说明”:

-

一个`include只能指定一个包含文件;

-

`include中的文件名可以是相对路径,也可以是绝对路径(ISE中调用Modelsim仿真的时候得用绝对路径,否则Modelsim会报错);

-

如果文件1包含文件2,而文件2要用到文件3的内容,那么在文件1中用`include命令分别包含文件2和文件3(文件3在文件2的前面)

例:

para.v中: `define A 2+3

para2.v中 : `define B `A+2

test.v中:

`timescale 1ns / 1ps`include"para.v"`include " para2.v"module test(input wire clk,output reg [7:0] result);always@(posedge clk)beginresult<= `B+10;endendmodule

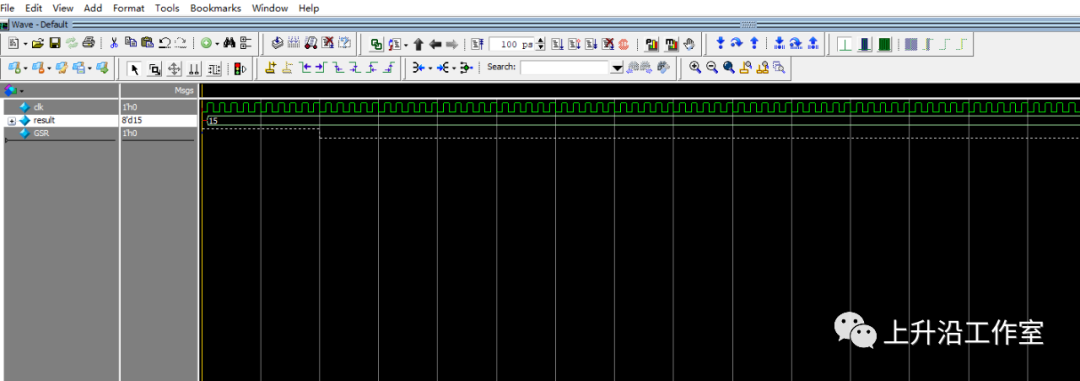

仿真结果如下所示:

04、 条件编译指令(`ifdef、`elsif、`endif)

条件预编译指令有如下几种形式:

1. `ifdef宏名

程序段1

`elsif

程序段2

`endif

当宏名被定义,则对程序段1进行编译,程序段2被忽略;否则编译程序段2,程序段1倍忽略。

`ifdef宏名

程序段1

`endif

其中程序段可以是语句组也可以是命令行

例:

`timescale1ns/1ps`defineMODE_ADD`defineMODE_ENABLEmodule test_add(input clk,rst_n,output reg [ 15 : 00 ] data_cal,output reg [ 15 : 00 ] data_cal2);:0]data;MODE_ADDclk or negedge rst_n) beginif(!rst_n)data_cal <= 1'b0;elsedata_cal <= data_cal + 16'd100;endMODE_ADD2clk or negedge rst_n) beginif(!rst_n)data_cal <= 1'b0;elsedata_cal <= data_cal + 16'd200;end`endifMODE_ENABLEM 10MODE_ENABLE2M 20`endifclk or negedge rst_n) beginif(!rst_n)data_cal2 <= 1'b0;elsedata_cal2 <= `M;end=`M;endmodule

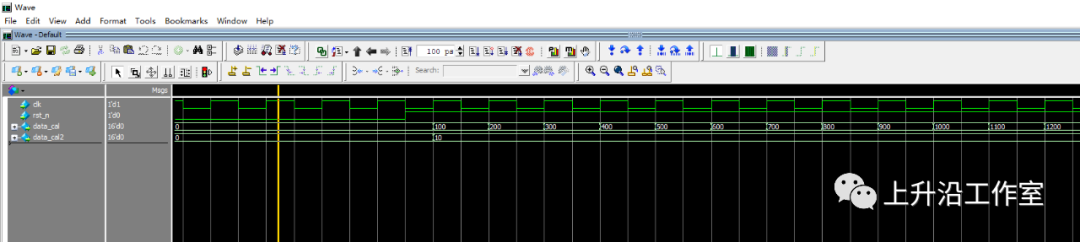

仿真结果如下:

如果将:

`defineMODE_ADD`defineMODE_ENABLE改成`defineMODE_ADD2`defineMODE_ENABLE2

仿真结果如下:

审核编辑:郭婷

-

仿真

+关注

关注

50文章

4039浏览量

133408 -

Verilog

+关注

关注

28文章

1343浏览量

109976 -

eda

+关注

关注

71文章

2708浏览量

172858

原文标题:Verilog基础知识学习笔记(五)

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Verilog-HDL实践与应用系统设计

Verilog HDL华为入门教程

Verilog HDL入门教程(华为绝密资料)

Verilog HDL程序设计教程_王金明

Verilog HDL硬件描述语言_Verilog语言要素

Verilog HDL入门教程

Verilog HDL入门教程之Verilog HDL数字系统设计教程

Verilog HDL入门教程

什么是预编译

Verilog HDL中常用预编译命令介绍

Verilog HDL中常用预编译命令介绍

评论