“本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括循环语句(forever、repeat、while和for)、运算符。”

01

—

循环语句

在Verilog中存在着4种类型的循环语句(forever、repeat、while和for),其中“while”与“for”的使用方法与C语言中的基本类似。

“forever”语句

语句格式如下: forever begin //add codes end

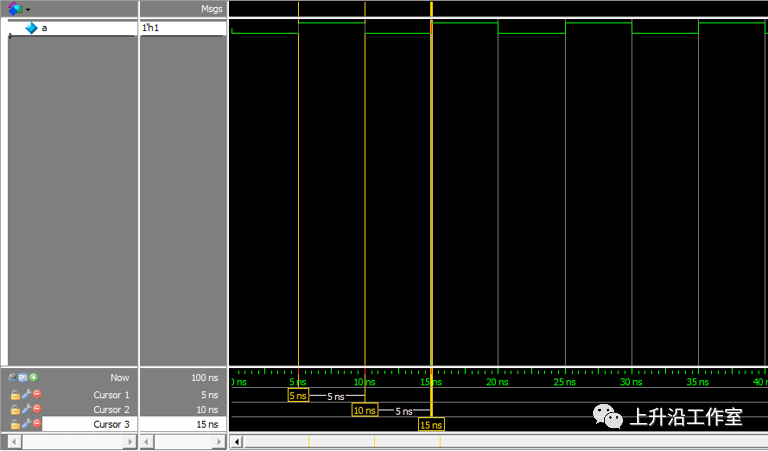

仿真效果如下:rega;initial begina = 0;foreverbegin#5 a = ~a;endend

-

“repeat”语句

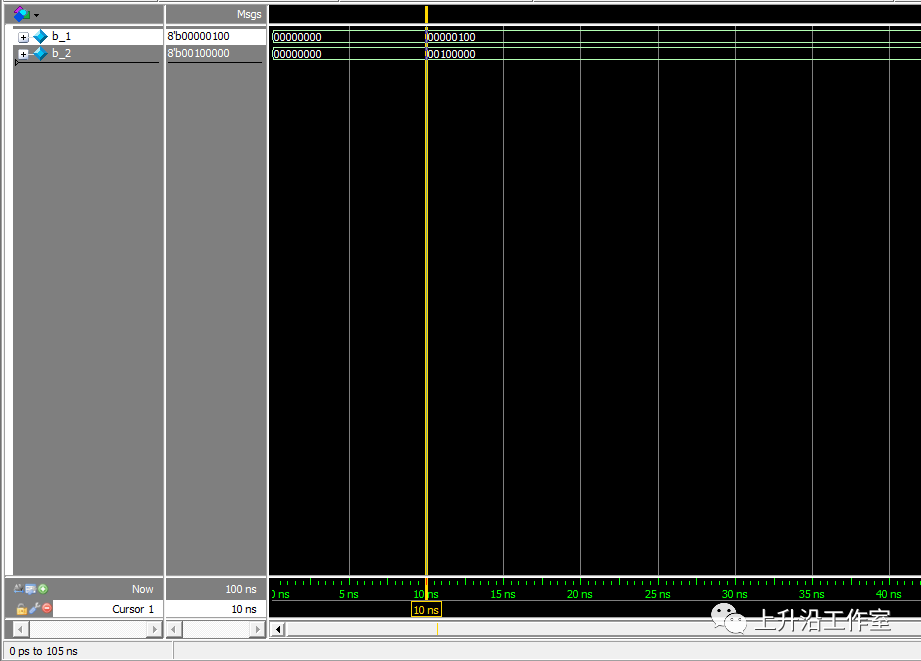

仿真结果如下:parameter times = 3;reg[7:0]b_1,b_2;initialbeginb_1 = 0;#10;b_1 = 8'b0000_0100;#10;endalways@(b_1)beginb_2 = b_1;repeat(times)beginb_2 = b_2 << 1;endend

在10ns的时候,b_1赋值为8’b0000_0100,这时候repeat语句触发,b_2变成了8’b0010_0000,可见b_2右移了三位,也就是repeat内的语句重复执行了3次。

-

“while”语句

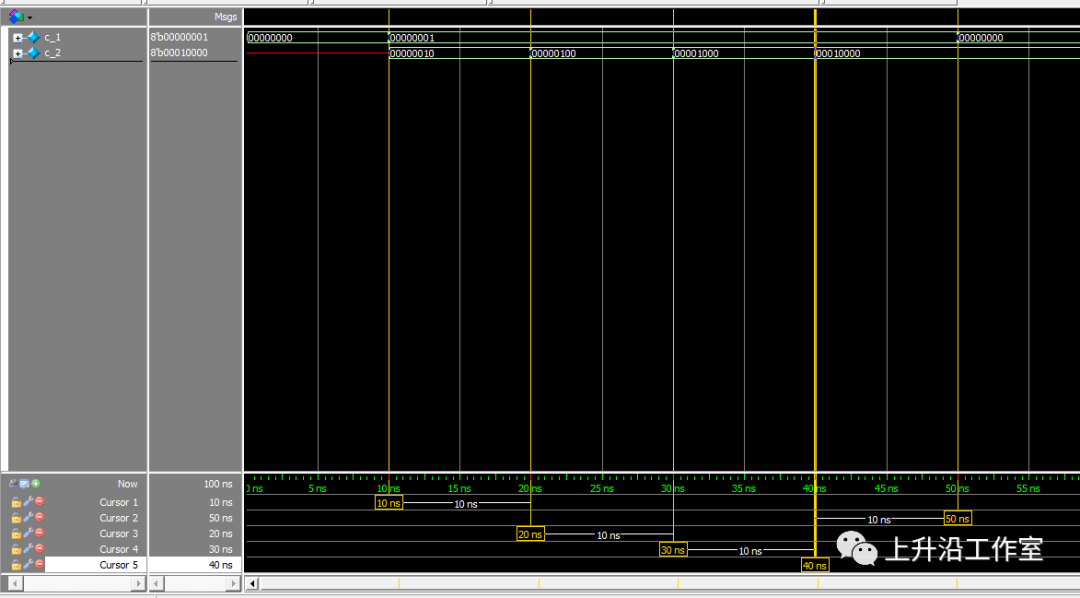

仿真结果如下:reg[7:0]c_1,c_2;initialbeginc_1 = 0;#10;c_1 = 1;c_2 = 8'b0000_0001;while(c_1)beginc_2 = c_2 << 1;#10;if(c_2 == 8'b0001_0000)c_1 = 0;elsec_1 = 1;endend

-

“for”语句

-

先求表达式1;

-

求解表达式2。若其值为真,则执行 for 语句中指定的内嵌语句,然后执行第3步;若表达式2值为假,则结束循环,转到第5步;

-

求解表达式3;

-

转回上面第2步继续执行;

-

循环结束,执行 for 语句下面的语句。

示例代码如下:

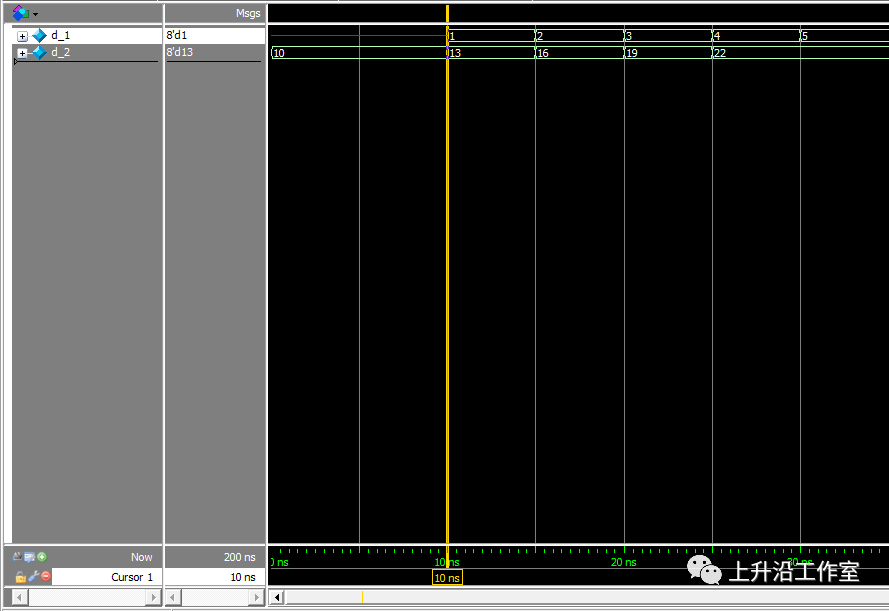

reg [7:0] d_1,d_2;initialbegind_2 = 10;#10;for(d_1=1;d_1<5;d_1=d_1+1)begind_2 = d_2 + 3;#5;endend

02

—

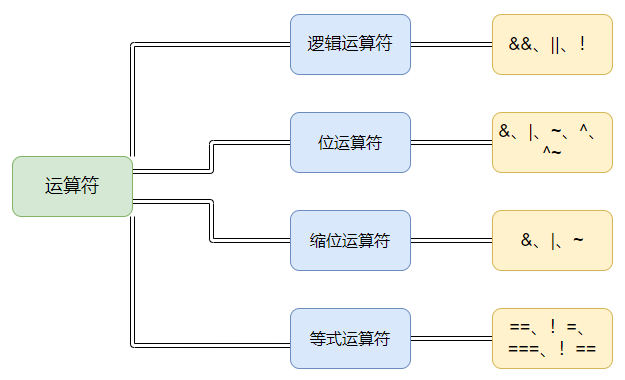

运算符

-

基本算术运算符

-

+ (加法运算符);

-

- (减法运算符);

-

* (加法运算符);

-

/ (除法运算符);

-

% (模运算符或者求余运算符,要求%两侧均为整型数据,结果取第一个操作数的符号位,-10%3的结果是-1,11%-3的结果是2);

-

赋值运算符

-

=;

-

<=;

-

关系运算符

-

> (大于);

-

>= (大于等于);

-

< (小于);

-

<= (小于等于);

-

== (等于);

-

!= (不等于);

-

=== (等于,可以比较含有X和Z的操作数,在仿真中用的比较多);

-

!== (不等于,可以比较含有X和Z的操作数,在仿真中用的比较多)。

-

逻辑运算符

-

&& (逻辑与);

-

|| (逻辑或);

-

! (逻辑非)。

-

条件运算符

?:

例子:y=x?a:b(当x为真时,y=a,当x为假时,y=b)。

-

位运算符

位运算符的操作数是几位,结果也是几位。

-

~ (取反);

-

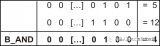

& (按位与);

-

| (按位或);

-

^ (按位异或,XOR,相同为0,不同为1);

-

^~ (按位同或,相同为1,不同为0);

-

~& (与非,先按与的操作,然后结果取反);

-

~| (或非,先按或的操作,然后结果取反)。

-

移位运算符

-

<< (左移,左移一位相当于乘2);

-

>> (右移,右移一位相当于除以2)。

-

拼接运算符

{s1,s2,s3,s4}:将两个或者多个信号拼接起来。

-

缩减运算符(一元简约运算符)

缩减运算符对单个操作数进行与、或、非递推运算,最后的结果是1位的二进制数。具体过程如下:

-

先将操作数的第1位和第2位进行与、或、非运算;

-

运算的结果与第3位进行与、或、非运算;

-

一次类推,知道最后一位。

审核编辑:郭婷reg [3:0] a;reg b;b = &a; 等同于 b = ((a[0]&a[1])&a[2])&a[3]。

-

Verilog

+关注

关注

28文章

1355浏览量

110841 -

C语言

+关注

关注

180文章

7618浏览量

138659

原文标题:Verilog基础知识学习笔记(三)

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

炼狱传奇-移位和位拼运算符之战

求一道MATLAB编程题。要求: 使用循环语句编程,但不能使用数组运算符和sum

Java基础之Java运算符

Bitwise 逻辑运算符进行设计

python运算符是什么

什么是逻辑运算符

Verilog逻辑设计中的循环语句和运算符

Verilog逻辑设计中的循环语句和运算符

评论