Step 1

首先,打开最新版本的Vivado(当前为2021.2):

1. 新建一个Vivado工程,将器件直接选定为board – VPK120。

2. 接着新加入一个以太网IP core,选好自己所需要的IP配置,本文以MRMAC IP为例,并在以太网IP的GT配置那页,选择GTM和156.25MHz时钟。

3. 然后就可以右键点击IP,选择Open IP Example Design…

Step 2

例子工程产生完毕之后,在工程的XDC文件里加入GT位置约束和参考时钟位置约束,示例如下:

set_property PACKAGE_PIN AF45 [get_ports gt_ref_clk_p]

set_property PACKAGE_PIN BG52 [get_ports {gt_rxp_in[0]}]

1. 这个参考时钟是VPK120板上自带的,可进行配置,产生不同频率的参考时钟。

2. 另外,VPK120板上有2个QSFP-DD光模块插槽,此处GT的(管脚)位置约束,正是为了将GT选在其中一个光模块插槽上面,方便之后的硬件上面连接使用。

Step 3

等该例子工程跑完综合,实现,并产生bit文件之后,请将PDI文件加载到你的VPK120里面:

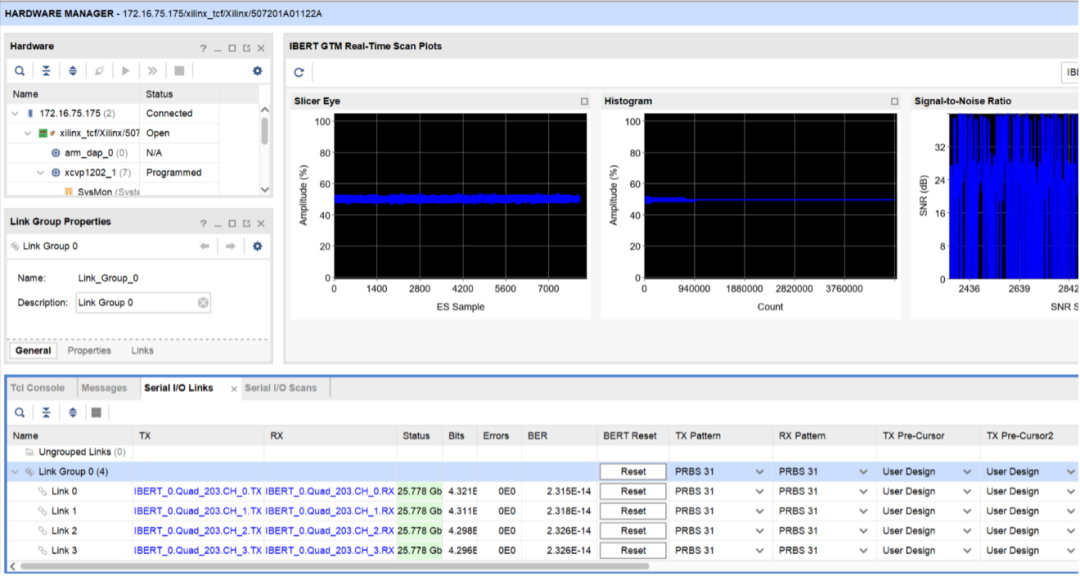

1. 工程上板之后,接下来第一步,我们要利用IP内部自带的in-system IBERT,先确认链路是否畅通,能正常工作。点击Serial I/O Link这一页里面的create links,将Quad_203里的4路GT全部添加为New Links。

a.全部设为Near-End PCS(如果外部光模块和光纤已经都接上了,此处可选None;建议先做Near-End PCS,再做None)。

b.TX和RX Pattern,全部设为PRBS31(一般8B10B数据应用选择PRBS7,而64B66B数据则选PRBS31)。

c.分别做下整个的TX Reset和RX Reset。

d.检查PLL锁定,线速率和TX/RXUSERCLK频率正确,Bits增加,Errors保持,以及BER不断减小,即可确认链路工作正常。

e.如果PLL无法锁定,请确认参考时钟频率是否已经设置正确,以及之前添加的GT和时钟位置约束是否已经正确起效。

f.如果PLL锁定,线速率也正确,但是误码不断增加,尤其是在loopback关闭的模式中,请先按照GT的调试过程,如调节TX预加重等,调好板上SI,确保没有误码。

2. 链路OK之后,将TX/RX Pattern改回User Design,并依次做一下TX Reset和RX Reset。然后我们就可以通过读取MRMAC内部寄存器,确认以太网的link是否已经能成功连接,起来工作了。

a.打开xsdb,然后connect。

b.再ta 1,选择Versal xcvp1202。

c.最后就可以读取MRMAC寄存器状态了,下面给出了一组读写寄存器的示例,在做了简单的复位后,直接读了下以太网的RX状态。

d.这里提供的是一组读写寄存器命令的示例,请按照自己的IP配置,读写相应的寄存器。寄存器具体定义,可以在mrmac_registers.csv文件里面找到(注意下面地址经过十六进制和十进制的转换)。

mwr -force 2752053252 0x00000FFF

mwr -force 2752053256 0x40000A24

mwr -force 2752053264 0x00000033

mwr -force 2752053260 0x00000C03

mwr -force 2752053456 0x00000000

mwr -force 2752057552 0x00000000

mwr -force 2752061648 0x00000000

mwr -force 2752065744 0x00000000

mwr -force 2752053252 0x00000000

mwr -force 2752053292 0x00000001

mwr -force 2752512000 0x00000F02

mwr -force 2752512000 0x00000002

mrd -force 2752577544

mwr -force 2752055108 0xFFFFFFFF

mwr -force 2752059204 0xFFFFFFFF

mwr -force 2752063300 0xFFFFFFFF

mwr -force 2752067396 0xFFFFFFFF

mrd -force 2752055108

mrd -force 2752059204

mrd -force 2752063300

mrd -force 2752067396

e.最后,可以得到正确结果如下,说明MRMAC已经link up了:

xsdb% mrd -force 2752055108

A4090744: 00010007

原文标题:如何在VPK120上实现MRMAC以太网IP

文章出处:【微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

-

以太网

+关注

关注

40文章

5460浏览量

172519 -

光模块

+关注

关注

77文章

1283浏览量

59197 -

Vivado

+关注

关注

19文章

815浏览量

66835

原文标题:如何在VPK120上实现MRMAC以太网IP

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

无法在XDC文件中设置maxdelay约束

关于XDC约束文件,你需要知道的几点

FPGA设计约束技巧之XDC约束之I/O篇(下)

如何在工程的XDC文件里加入GT位置约束

如何在工程的XDC文件里加入GT位置约束

评论