当今世界处于一个信息爆炸的时代,如何快速高效的处理信息,成为了信息技术领域研究的首要问题。结合光子计算的发展历史,光子将在未来信息处理领域扮演越来越重要的角色。基于马赫-曾德光学干涉仪(Mach-Zehnder; inter-ferometer, MZI)的可编程光子集成电路在人工智能,深度学习与神经网络等诸多需要巨大算力的领域均取得了极大的进展。

但是,随着光子集成电路(Photonics Integrated Circuit, PIC)规模的不断扩大,原本存在于每个原件中的微小制造误差,不断累积,最终会对系统的整体性能产生颠覆性的影响,譬如输出功率大幅降低。

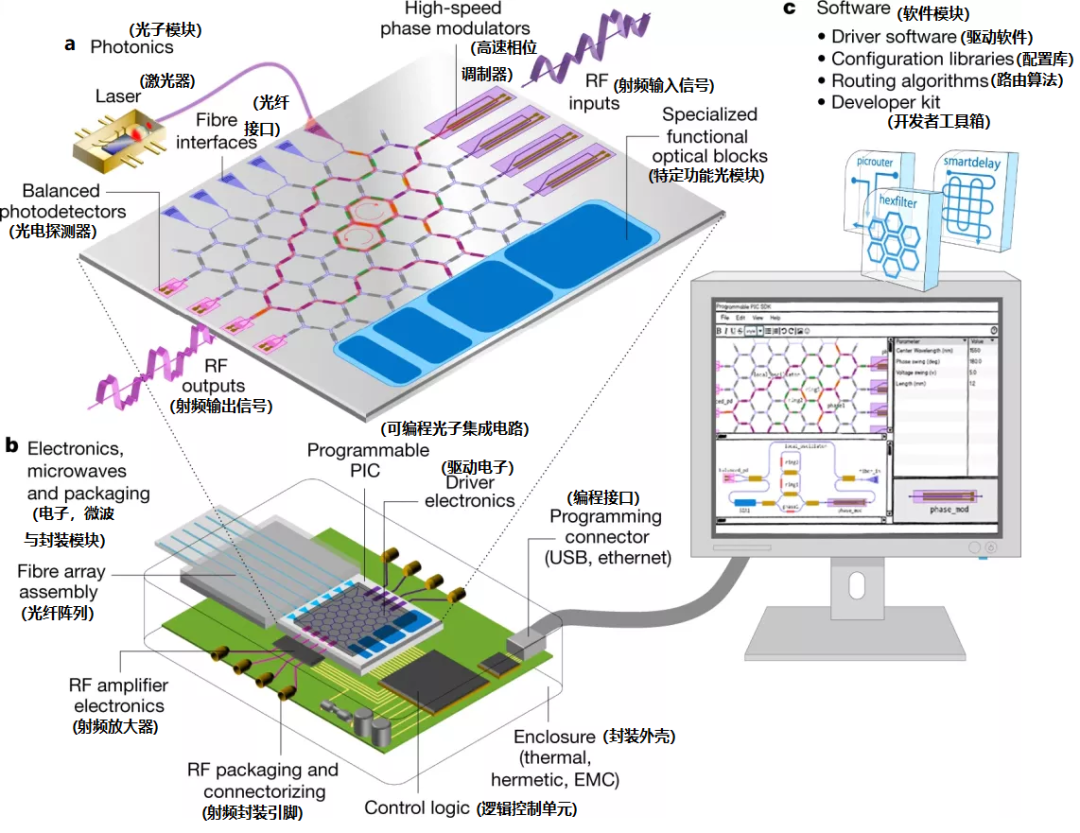

图 1:光子芯片(艺术效果图)

针对这一问题,来自美国麻省理工学院的 Dirk Englund 教授提出了一种在光子逻辑门内部的纠错方式,使得在现有制造工艺容差范围内,可将集成光子系统规模提升至数百个单元模块[1]。

面临挑战

可执行任意无源矩阵运算或滤波操作的可编程光子集成电路,也被称为光学 FPGA,其光子线路可以在制备后灵活地被软件所重构。这种系统具有速度快,耗能低等诸多优势,在量子通信,信号处理与人工智能等诸多领域有着广泛的应用[2]。

图 2:可编程光子电路示意图

图源:Nature / 图译:撰稿人 Cyan为应对更复杂的问题,光子系统也需提供更多算力,这意味着其规模也将进一步扩大。然而,随着 PIC 内部模块数量的增加,本存在于各模块内部的微小工艺误差,通过相互累积,将会对系统的整体性能产生巨大的打击。譬如,现代生产工艺下,分光器的正常误差容限约为 2%。但是,通过 Michael Y.-S. Fang 等人的研究发现,其设计的前馈光子电路在执行图像识别任务时,由于累计的模块微小缺陷,整个系统的准确率会有大幅下降。

为此,也有很多全局变量优化的办法被提出,例如非线性优化,梯度下降与原位后向传输法等。但是,这些优化方案都是极度消耗时间且很难随着 PIC的规模而扩展。此外,如若针对每一个芯片都做一次优化,这明显是极度低效的。

解决方案

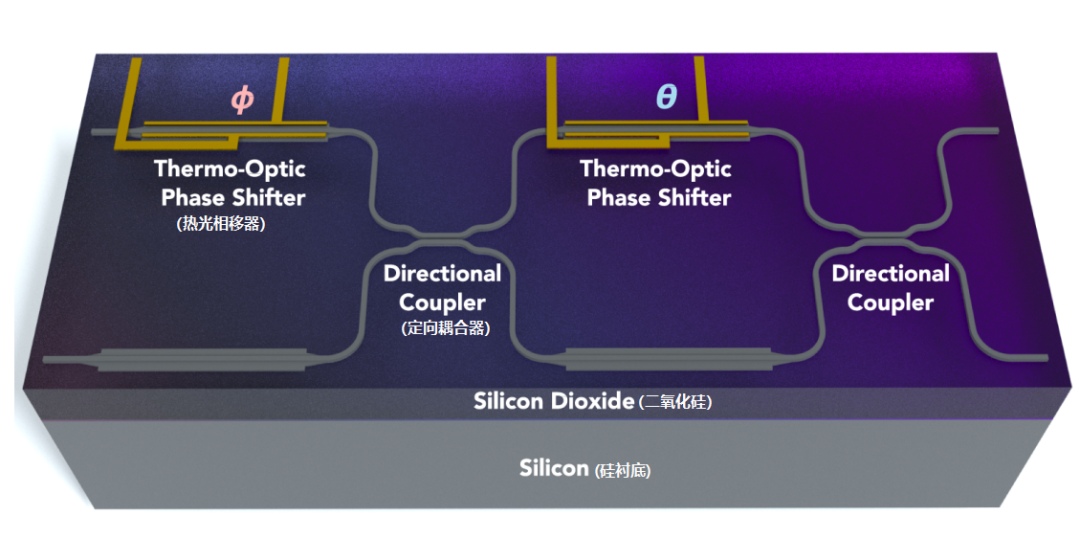

Dirk Englund 团队在可编程光子集成电路中,基于马赫-曾德干涉仪构成了最基本的纠错模块,其结构如图 3 所示。理想状态下,θ 与 φ 分别为 MZI 的两臂相移,以产生 50:50 的分光效果。但是由于工艺误差,将会引入相差 α 与 β,使得分光效果不准。通过如下步骤,分光误差将会得以矫正:

校准并检测出所有相移器的误差并建立查找表 (Look-UpTable)

根据计算法则,算出每个相移器在理想状态时的相移值 θ 与 φ

根据算法,对 θ 值进行分类

依据查找表,对 MZI 施加相移校准分量 φ’,实现完美 1:1 分光

图 3:马赫-曾德干涉仪 结构图图源:Optica

与其他解决方案相比,该方案具有如下优势:

灵活度高,只需一次硬件校准便可计算出任意幺正变换所需的配置参数

负载小且不需要额外的干涉仪或功率探测器

应用场景 为验证方案的有效性,特在两种经典可编程光子集成电路结构中(前向传输结构与循环网格结构),进行仿真验证,并做出效果对比。

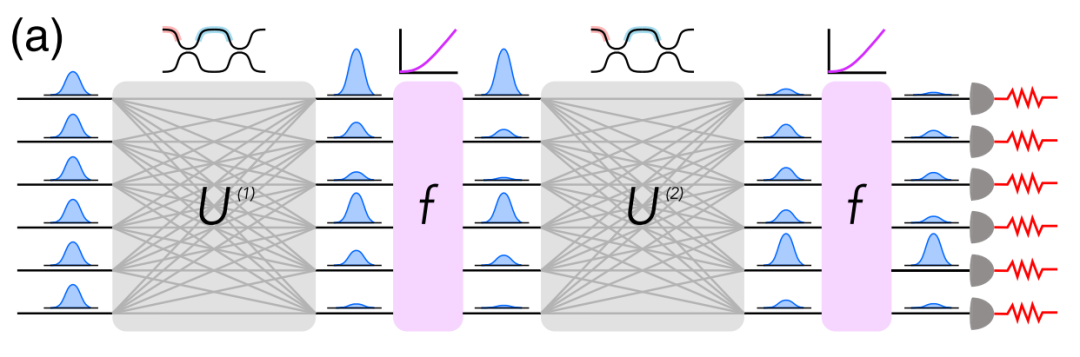

1. 光学神经网络

光学神经网络是可编程光子集成电路的重要应用场景之一,其结构如图 4 所示,本文通过 Neurophox Package 仿真了一个双层神经网络来执行 MNIST 库中的图像识别测试。

图 4:光学神经网络结构图图源:Optica

实验结果证明,在模块容差为 3% 时,小规模神经网络 (模块数为 36,64)的准确率可达 95%~96%。随着系统规模扩大至 144 或 256 个模块时,其准确率可以提升至 97%。但是,如果没有硬件校准辅助,系统准确率会骤减至 90%;而在保障正确率的前提下,硬件校准方案可使模块不均匀度容限达到 6%(实际工艺容限约为2%),这将大大降低对制造工艺的苛求。由此可见,硬件校准方案可以在工艺技术没有重大革新前,使得一个容纳数百个光模块的高精确度神经网络成为可能。

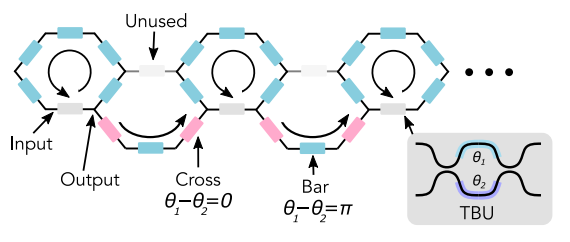

2. 可调谐式色散补偿

可编程光子集成电路的另一种典型结构便是循环网格结构。该结构可以构成有/无限响应滤波器 (FIR/IIR),而 Dirk 等人使用 IIR 构成了一个在传统通信链路以及量子密钥分配等诸多场景均有应用的可调谐色散补偿器,其结构如图 5 所示。

图 5:可调谐色散补偿器图源:Optica

实验结果与光子神经网络相似,由于累计误差而造成的相位偏差可以被硬件纠错方案所弥补,继而使得整个补偿器可以得到理想的色散分布。

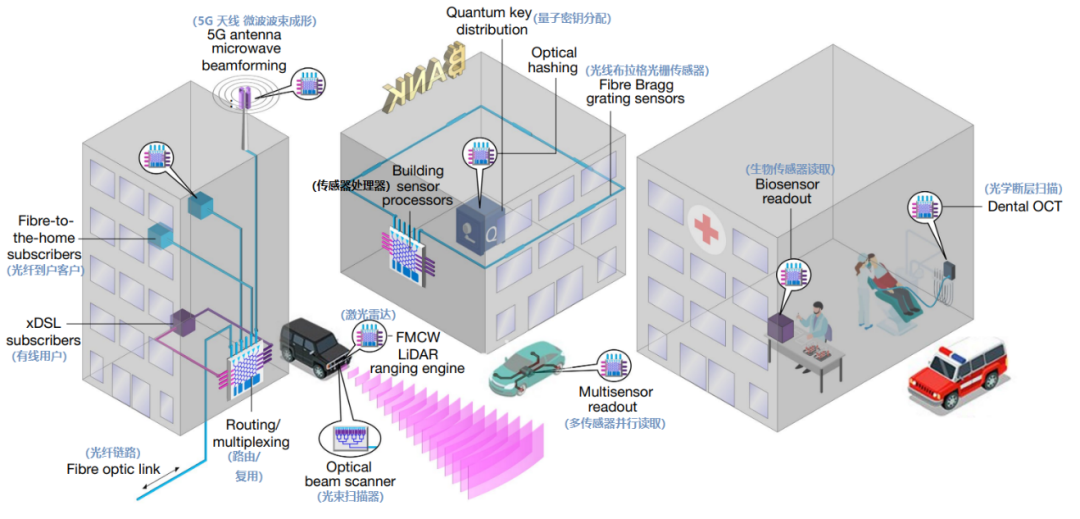

未来发展 可以预见未来光子集成电路,特别是可编程光子集成电路将会在家居,银行,医疗,驾驶等诸多应用场景发挥重要作用,如图 6 所示。为应对这些复杂场景中的挑战,大规模或超大规模光子集成电路系统或将不可避免。

图 6:光子芯片的应用场景图源:Nature / 图译:撰稿人 Cyan

综上,这种全新的硬件纠错方式与原有的优化方案相比,仅仅使用一次校准流程,便可灵活的实现任意的矩阵变换/计算。此外,通过对可编程光子电路中的两种典型结构(前向传递与循环网格结构)的仿真验证,不难发现,该方案不仅使得对制备工艺的要求大幅降低,还极大地减少了每个模块的训练开销。因此,该方案为可编程光子电路技术提供了新的扩展途径。

原文标题:可编程光子电路的“硬件纠错”

文章出处:【微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

电路

+关注

关注

172文章

5933浏览量

172459 -

可编程

+关注

关注

2文章

871浏览量

39847 -

硬件

+关注

关注

11文章

3345浏览量

66294

原文标题:可编程光子电路的“硬件纠错”

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

编程是一种思维方式,而代码是一种表现形式,硬件只不过是对思维方式的物理体现

急聘!FPGA逻辑设计部门经理

单片机的四种烧写方式是什么

一种安全的纠错网络编码

基于FPGA的检纠错逻辑算法的实现

用FPGA实现纠错编码的一种方法

一种模糊时态描述逻辑

一种基于FPGA的SDRAM设计与逻辑时序分析

一种在光子逻辑门内部的硬件纠错方式

一种在光子逻辑门内部的硬件纠错方式

评论