导读

CPU(中央处理器),也被称为微处理器,是计算机的心脏和/或大脑。本文让我们一起深入了解计算机的核心,以帮助我们高效地编写计算机程序。

以下为译文:

“工具通常比机器简单,通常用手来使用,而机器通常由动物或蒸汽动力驱动。”

——查尔斯·巴贝奇

计算机是一种机器,主要由电力驱动,但其灵活性和可编程性帮助实现了其作为一种工具的简单性。CPU是计算机的心脏和/或大脑。负责执行提供给它们的指令。它的主要任务是执行算术和逻辑运算,并将指令协调在一起。在深入到本文的主要部分之前,让我们先看看CPU的主要组成部分,以及它们的作用分别是什么。

1、CPU的两个主要组成部分

控制单元 — CU控制单元(CU)是CPU的一部分,它帮助协调指令的执行。它告诉CPU应该做什么。它的主要职责是根据指令,帮助激活连接CPU和计算机其他不同部件(包括ALU)的线路。控制单元是CPU的第一个接收处理指令的部件。

控制单元有两种类型:

硬接线控制单元。

微型可编程(微编程)控制单元。

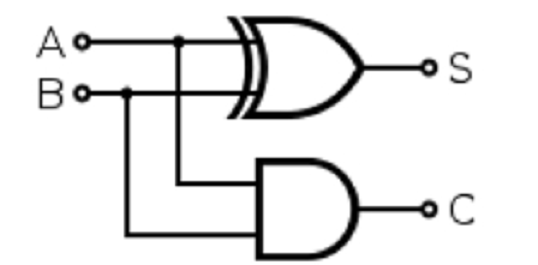

硬接线控制单元是一种硬件,它需要在硬件上进行更改以实现对其工作方式的修改,而微型可编程控制单元则可以进行编程以更改其工作方式。硬接线控制单元在处理指令方面更快,而微型可编程控制单元则更灵活。算术逻辑单元 — ALU算术逻辑单元(ALU),顾名思义,就是负责所有的算术和逻辑运算。算术逻辑单元执行加法运算,减法运算等操作。算术逻辑单元是由执行这些操作的逻辑电路或逻辑门组成。大多数逻辑门接受两个输入并产生一个输出。下面是一个半加法器电路的例子,它接受两个输入并输出结果。这里A和B是输入,S是输出,C是进位。

半加法器电路图

2、存储 - 寄存器和存储器

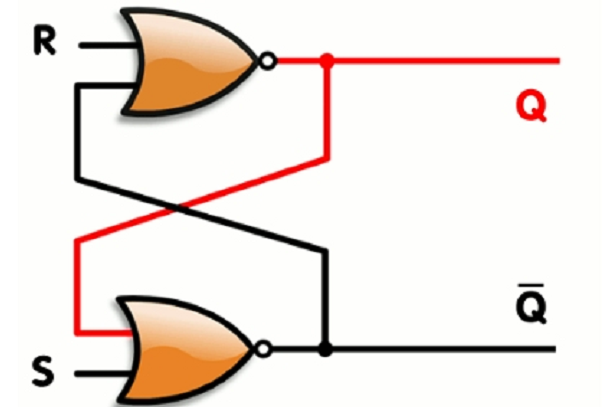

CPU的主要任务是执行提供给它的指令。在大多数情况下,为了处理这些指令,它需要数据。有些数据是中间数据,有些是输入,另一些是输出。这些数据连同指令一起存储在下列存储器中:寄存器寄存器是一组可以存储数据的小地方。寄存器是锁存器(Latches)的组合。锁存器也称为触发器(flip-flops),是存储1位信息的逻辑门的组合。锁存器有一条输入线,一条写入和输入线,和一条输出线。我们可以启用写入线对存储的数据进行更改。当写入线被禁用时,输出始终保持不变。

SR锁存器,由一对交叉耦合的或非门(NOR Gates)构成。CPU由寄存器来存储输出数据。由于是中间数据,它们被发送到主存储器(RAM)的速度会慢。这些数据被发送到由总线连接的其它寄存器。寄存器可以存储指令、输出数据、存储地址或任何类型的数据。存储器(RAM)RAM - 随机存取存储器是寄存器的集合,它们以优化的方式排列和压缩在一起,以便存储更多的数据。随机存取存储器(RAM)是易失性的,当我们关闭电源时,它存储的数据会丢失。由于RAM是用于读/写数据的寄存器的集合,因此RAM可以用于存储8位地址的输入、用于存储实际数据的数据输入,和用于储存最后的和锁存器一样工作的读写启用码。

3、什么是指令

指令是计算机可以执行的最小粒度运算。CPU可以处理各种类型的指令

指令类型包括:

算术运算指令,如加法和减法运算

逻辑运算指令,如逻辑与(AND)、逻辑或(OR)和逻辑非(NOT)运算

数据传送指令,如数据移动、输入、输出、加载和存储

程序控制指令,如条件/无条件转移指令(if…goto,goto),转子指令和转移指令(call,return)

通知CPU程序已结束的Halt指令

指令通过以下方式提供给计算机:使用汇编语言直接提供,或由编译器生成,或用某些高级语言解释给出。这些指令在CPU内部是硬连线的。算术和逻辑运算指令包括在ALU(算术逻辑单元)中,而程序控制指令由CU(控制单元)管理。通常在一个时钟周期(clock cycle)内,计算机可以执行一个指令,但是现代的计算机可以同时执行多个指令。计算机可以执行的一组指令称为指令集。

4、CPU时钟

时钟周期计算机的速度由其时钟周期(Clock cycle)衡量。它是指计算机每秒工作的时钟周期数。单个时钟周期非常小,大约250*10^(-12)秒。每秒时钟周期数越高,处理器速度越快。CPU时钟频率(clock rate)的测量单位为GHz(千兆赫兹)。1Ghz等于10 ⁹Hz(赫兹)。一赫兹意味着一秒钟。所以一千兆赫兹意味着每秒10 ⁹个时钟周期。时钟周期越小,CPU可以执行的指令数量越多。时钟周期等于时钟频率的倒数,而CPU时间=时钟周期数/时钟频率这意味着为了改进(减少)CPU时间,我们可以通过提高时钟频率,或优化我们提供给CPU的指令来减少指令需要的时钟周期的数量。一些处理器提供了提高时钟频率的能力,但由于这是一个物理变化,可能会出现过热,甚至冒烟/起火。

5、指令是如何执行的

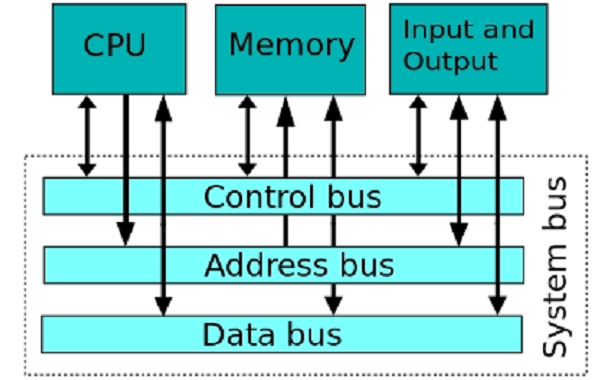

指令按顺序存储在随机存取存储器(RAM)上。对于一个假设的CPU指令,它由操作码(OP code)和存储器或寄存器地址组成。控制单元(CU)内有两个寄存器:用于加载指令操作码的指令寄存器(IR),和用于加载当前正在执行的指令地址的指令地址寄存器。CPU中还有其他寄存器,用于存储一个指令的最后4位的地址中存储的值。让我们以一组实现两个数字相加操作的指令为例。下面是这些指令及其说明:第一步 - LOAD_A 8该指令最初保存在RAM中,比如说指令<1100 1000>。它的前4位是操作码。这决定了这个指令要做什么。然后该指令被读取到控制单元的指令寄存器(IR)中。指令被译码为load_A,这意味着它需要加载地址1000中的数据,地址1000是存储在寄存器A中的指令的后4位。第二步 - LOAD_B 2与上面类似,它将内存地址2(0010)中的数据加载到CPU的寄存器B中。第三步 – ADD B A接下来的这条指令是把这两个数字相加。在这里,控制单元(CU)告诉算术逻辑单元(ALU)执行加法操作并将结果保存回寄存器A中。第4步 – STORE_A 23将结果保存回寄存器A中。这是一组非常简单的指令,实现了两个数字的相加操作。现在,我们成功地得到了两个数字相加的和值!总线CPU,寄存器,存储器和IO设备之间的所有数据都通过总线传输。要将刚才两数相加得到的和数保存到存储器中,CPU将存储器地址放入地址总线,将得到的结果(和数)放入数据总线,然后在控制总线中启用正确的信号。这样,数据在总线的帮助下被保存到存储器中。

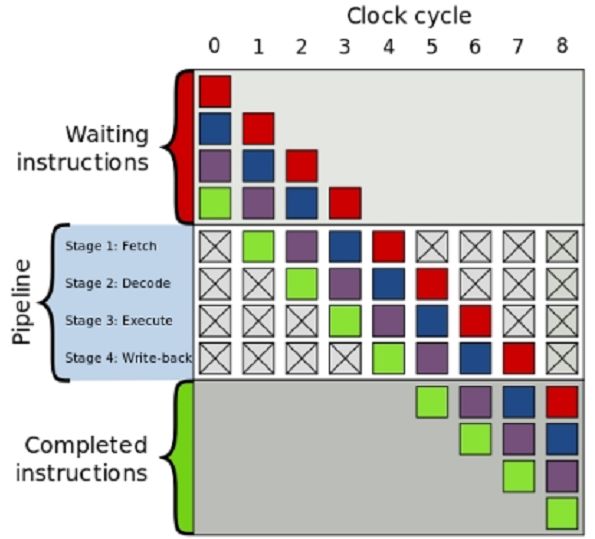

计算机系统总线缓存CPU还具有将指令预取到其缓存中的机制。我们知道,一个处理器可以在一秒钟内完成数百万条指令。这意味着从存储器(RAM)中获取指令所花费的时间比执行指令所花费的时间要多。所以CPU会预取一些指令和数据到其缓存中,以加快执行速度。如果缓存中的数据和操作内存中的数据不同,则将数据标记为脏位(dirty bit)。指令流水线现代CPU在指令执行中采用指令流水线技术实现取指(FI)、译码(DI)、执行(EI)的并行化。当一条指令完成“取指”后进入“译码”的同时,下一条指令就可以进行“取指”了,这样就提高了指令的执行效率。

指令流水线技术然而,当一条指令和另一条指令有依赖关系时,这种技术会产生问题。所以,指令流水线技术只能够让处理器以不同的顺序执行相互之间没有依赖关系的指令。多核计算机它基本上是有不同的CPU,但是有一些共享资源,比如缓存等。

6、性能

CPU的性能取决于它的执行时间。性能=1/执行时间假设一个程序执行需要20毫秒。CPU性能为1/20=0.05ms。相对性能=执行时间1/执行时间2影响CPU性能的因素是指令执行时间和CPU的时钟速度(时钟频率)。因此,为了提高程序的性能,我们要么提高CPU的时钟速度(时钟频率),要么减少程序中的指令数量。处理器的速度有限,现代多核计算机每秒可以支持数百万条指令。但是,如果我们编写的程序有太多的指令,就将导致整体性能的降低。大O符号(Big O notation)计算方法可以用来确定在给定输入的情况下CPU的性能将如何受到影响。为了尽可能地提高CPU的速度,很多优化工作已经在CPU中进行。而我们在编写任何程序时,都需要考虑如何尽可能地减少我们提供给CPU的指令数量,以提高计算机程序的性能。

原文标题:CPU 是如何工作的?

文章出处:【微信公众号:Imagination Tech】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

处理器

+关注

关注

68文章

19245浏览量

229596 -

cpu

+关注

关注

68文章

10850浏览量

211518 -

计算机

+关注

关注

19文章

7484浏览量

87841

原文标题:CPU 是如何工作的?

文章出处:【微信号:Imgtec,微信公众号:Imagination Tech】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

CPU(中央处理器)的组成部分及工作原理

CPU(中央处理器)的组成部分及工作原理

评论