作者:泛林集团高级副总裁兼刻蚀业务部总经理Vahid Vahedi

近日,泛林集团推出三款开创性的选择性刻蚀产品:Argos®、Prevos™和Selis®。

这些突破性产品旨在补充和扩展泛林集团行业领先的刻蚀解决方案组合,使芯片制造商能够以超高的选择性和埃米级的精度刻蚀和修改薄膜,以实现最先进的集成电路(IC)性能并加速其3D路线图。

在我分享泛林集团特有的选择性刻蚀方法之前,让我们先来了解一下,在3D时代创造下一代芯片所面临的复杂挑战。

对精度的需求

微缩(即缩小芯片中的微小器件,如晶体管和存储单元)从来都不是容易的事情,但要想让下一代先进逻辑和存储器件成为现实,就需要在原子级的尺度上创造新的结构。当处理这么小的维度时,可以变化的空间微乎其微。

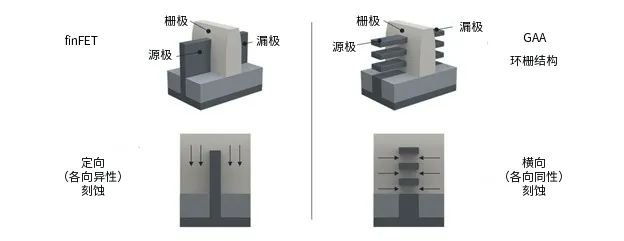

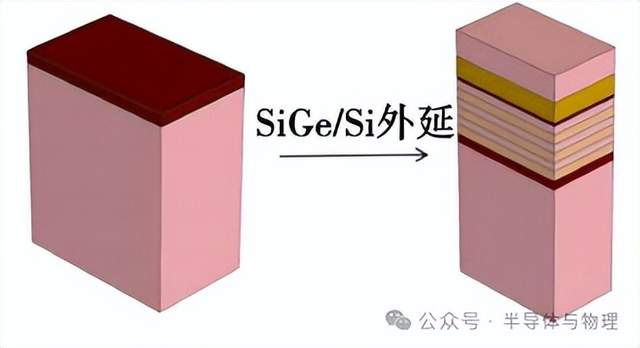

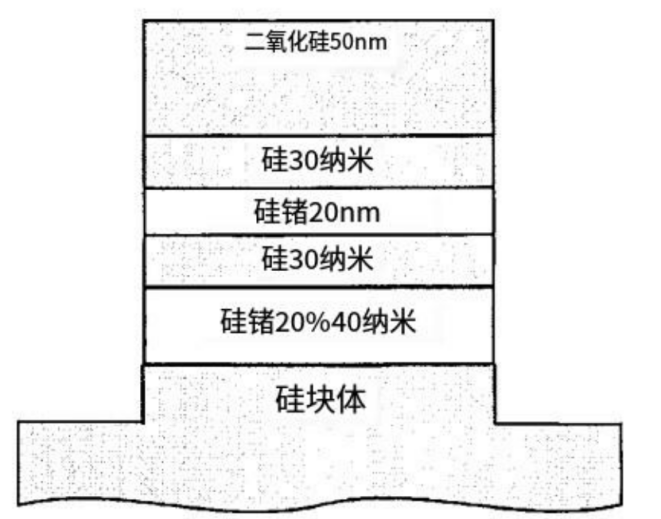

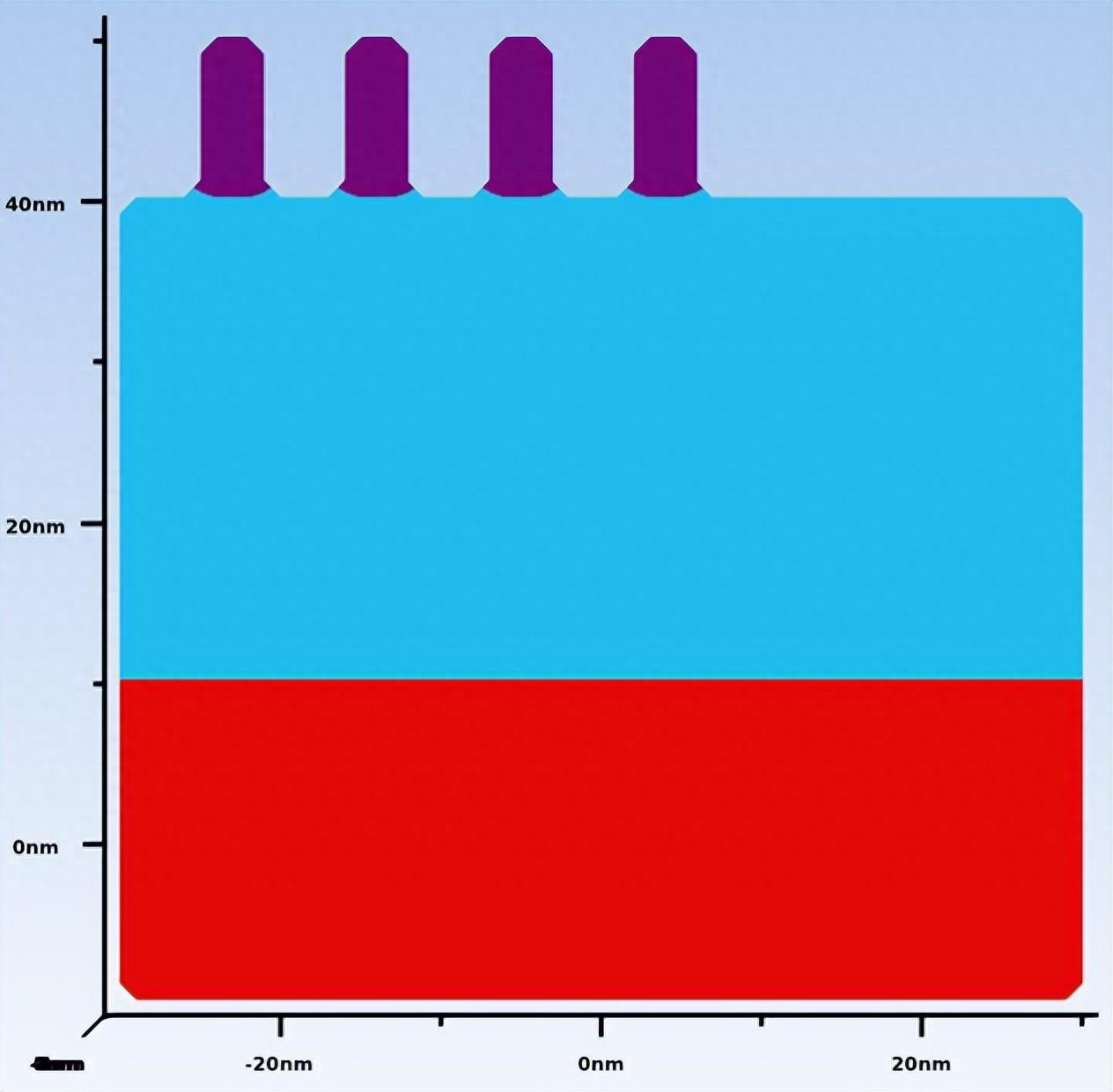

更为复杂的是,需要各向同性地、或者说在所有方向上均匀地去除材料。因此,为了芯片的更优性能而改变器件架构,就需要新的工艺。例如,在环栅(GAA)结构中,牺牲的SiGe层需要通过各向同性刻蚀来部分或全部去除,但又不能对相邻的硅层造成损失或破坏。

从finFET到GAA的过渡驱动了关键的各向同性选择性刻蚀要求

精密选择性刻蚀和表面处理

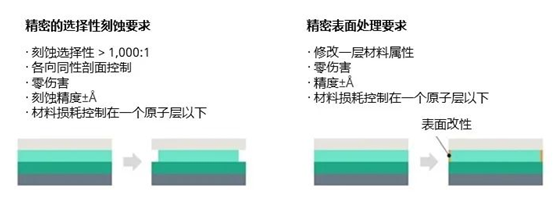

如下图所示,精密选择性刻蚀的挑战在下列四种材料示例中能够得到最好的呈现,在满足控制各向同性轮廓角的情况下,精确地刻蚀下图中的材料(绿色部分),而不刻蚀或损坏任何其他层。

精密表面处理需要对其中一层的材料属性进行修改,以保证在不损坏或修改其他层的情况下提高器件性能。

新材料需要精确的能量调谐

如今在创建器件结构时,一个比较常见的处理步骤是去除硅(Si)层,同时留下氧化硅(SiO2)层。在基于离子的刻蚀中,我们通过使用可以保护不需要被去除层的掩膜来控制去除哪些薄膜。

通过使用我们的选择性刻蚀产品,我们可以选择性地仅去除硅并留下氧化硅,方法是制造能量极低的刻蚀剂,其能量仅大于Si-Si键合能(3.4 eV)、但小于硅和氧(Si-O)键合能(8.3 eV),使其在相对较小的范围内(4.9 eV)。

然而,新材料的能量范围要小得多。例如,在GAA器件中仅去除SiGe层而不去除相邻的Si层需要在小于0.3 eV的范围内的能量调谐。

真正精确的选择性刻蚀需要先进的高分辨率能量调谐作为系统设计的基本部分。这种能力远远超过了传统“块状”刻蚀方法所支持的性能水平。此外,它需要增加步骤、工艺和腔室的复杂组合,以满足原子层精度的严格要求,这是泛林集团选择性刻蚀产品设计的核心。

新材料推动了对高分辨率能量调谐的需求

Argos、Prevos和Selis选择性刻蚀提升到新的水平

泛林集团全新的精密选择性刻蚀和表面处理设备组合有望加速芯片制造商的3D逻辑和存储路线图,这是半导体行业一次重大的进化式飞跃。

- Argos能提供革命性全新选择性表面处理方式,其创新的MARS™(亚稳态活性自由基源)可以产生非常温和的自由基等离子体,这是先进逻辑应用中高度选择性表面改性所必需的。

- Prevos采用化学蒸汽反应器,用于极低能量下高精度的选择性刻蚀。泛林集团开发了一种全新专有化学催化剂,专门用于要求极高选择性的应用,如天然氧化物突破、精密修整和凹槽。

- Selis通过使用低能量自由基源控制等离子体,将能量调谐提升到一个全新的水平。它还具有极低的能量处理模式,专为选择性必须超高的极端应用而设计,例如对于形成GAA结构非常关键的SiGe选择性刻蚀步骤。这个过程十分精确,Selis可以在不损坏关键硅层的前提下刻蚀SiGe层。

通过协作实现更大的创新

为了支持客户的3D路线图,我们需要在源技术、化学成分、材料科学和其他重要的腔室硬件设计方面进行大胆的新开发。我为泛林集团的团队感到非常自豪,他们让这些产品成为现实,其中包括一些顶级的技术专家,他们专注于开发源技术和颠覆性的腔室硬件设计;一群出色的化学家,他们致力于开发新的化学成分,以支持我们在刻蚀工艺和表面处理方面的创新方法。通过与客户、技术专家和产品团队的合作,他们已经在选择性刻蚀创新方面实现突破,这将使世界领先的芯片制造商得以提供下一代3D逻辑和存储设备。

近期会议

2022年5月24日,由ACT雅时国际商讯主办,《半导体芯科技》&CHIP China晶芯研讨会将在苏州·金鸡湖国际会议中心隆重举行!届时业内专家将齐聚姑苏,与您共探半导体制造业,如何促进先进制造与封装技术的协同发展。大会现已启动预约登记,报名链接:http://w.lwc.cn/s/ZFRfA3

关于我们

《半导体芯科技》(Silicon Semiconductor China, SiSC)是面向中国半导体行业的专业媒体,已获得全球知名杂志《Silicon Semiconductor》的独家授权;本刊针对中国半导体市场特点遴选相关优秀文章翻译,并汇集编辑征稿、国内外半导体行业新闻、深度分析和权威评论、产品聚焦等多方面内容。由雅时国际商讯(ACT International)以简体中文出版、双月刊发行一年6期。每期纸质书12,235册,电子书发行15,749,内容覆盖半导体制造工艺技术、封装、设备、材料、测试、MEMS、IC设计、制造等。每年主办线上/线下 CHIP China晶芯研讨会,搭建业界技术的有效交流平台。

-

刻蚀

+关注

关注

2文章

190浏览量

13145 -

刻蚀工艺

+关注

关注

2文章

38浏览量

8443 -

泛林集团

+关注

关注

0文章

58浏览量

11810

发布评论请先 登录

相关推荐

如何提高湿法刻蚀的选择比

SiGe与Si选择性刻蚀技术

选择性沉积技术介绍

过电流保护的选择性是靠什么来实现的

物联网行业中3D打印工艺——SLS(选择性激光烧结)工艺

泛林集团推出第三代低温电介质蚀刻技术Lam Cryo 3.0,助力3D NAND迈向千层新纪元

泛林集团推出第三代低温介质蚀刻技术Lam Cyro 3.0

交流二元继电器如何具有相位选择性和频率选择性

泛林集团与印度签署备忘录,提供虚拟化软件、芯片制造及代工服务培训

锗化硅(SiGe)和硅(Si)之间的各向同性和选择性蚀刻机制

泛林集团韩国公司业务总裁变更,面临日电竞争与与P的合作挑战

SystemVue可以计算带有频率选择性的链路的IIP3吗?

泛林集团推开创性的选择性刻蚀解决方案 加速实现3D

泛林集团推开创性的选择性刻蚀解决方案 加速实现3D

评论