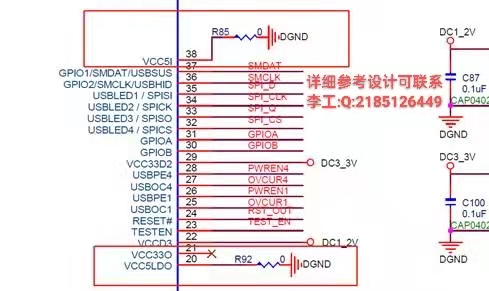

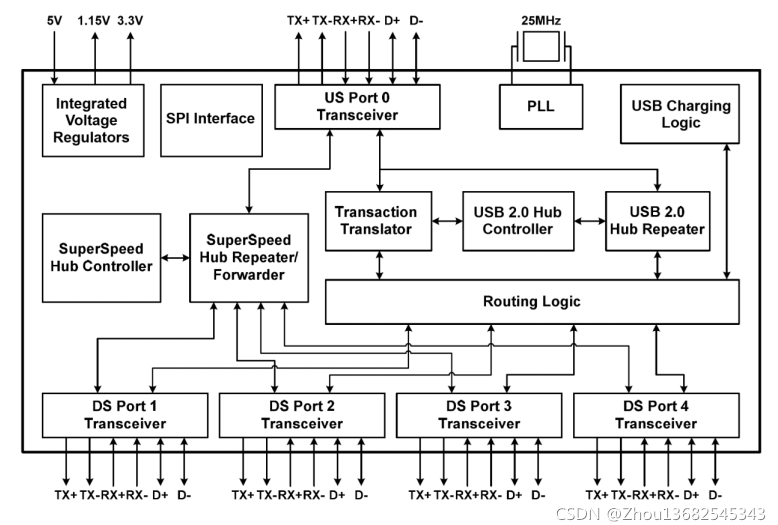

相对于VL817C0以及VL817B0来说,VL817S使用外部供电不需要接入5V,HUB 5V 请参考参考设计接地。内部3.3 LDO输出请悬空。1。2V LX和FB请悬空。如下所示,详见参考设计。

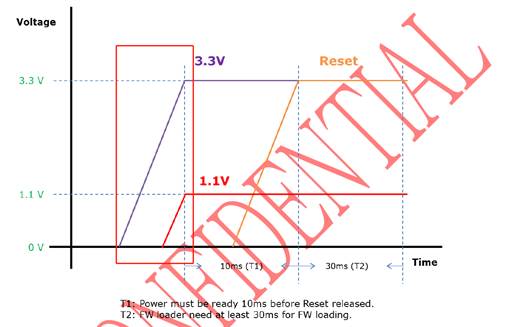

1、3.3V和1.2V之间的时序要求是怎么样的?

下图是VL817(S) 上电时序。参考线路中有增加不上件0。1uF调整时序。

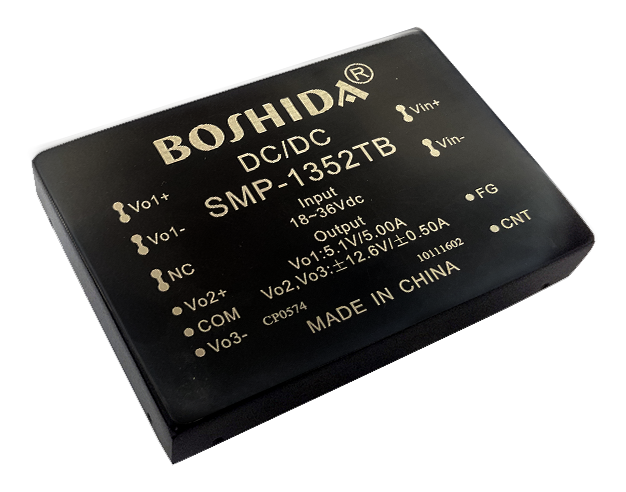

2,各电源的纹波要求是怎么样的?

没有特别要求。DC-DC基本都可以满足纹波要求

3、817B0/C0和817S这三款芯片的对比测试数据以及产品替换,可根据你们

的数据来评估重点测试内容及注意事项

内部测试目前来说OK,可进行PIN TO PIN D迭代代替

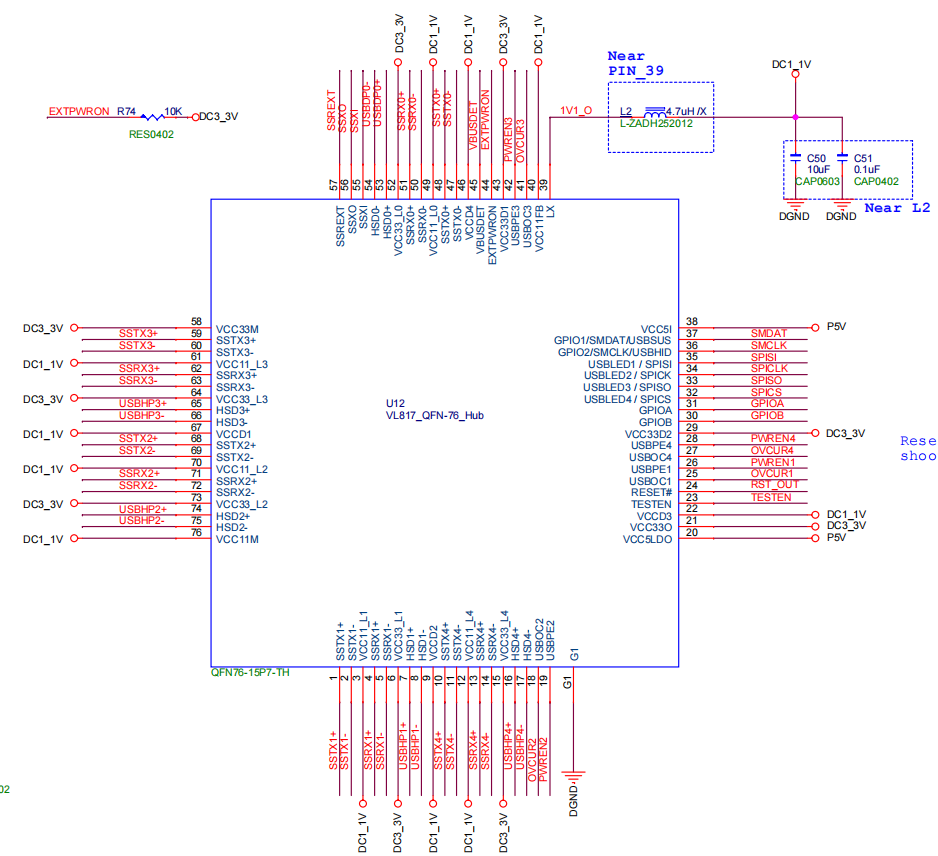

4、需要提供LAYOUT指导说明文件或者参考的PCB文件

请对比VL817B0/C0规格书以及相关原理图,结合以上更改参数进行对照修改。

VL817相关原理图:

VL817 Power On Sequence上电时序:

1.1V 和3.3V 理论上需要同时起来,误差需保证两个电压上电间隔超过1mS

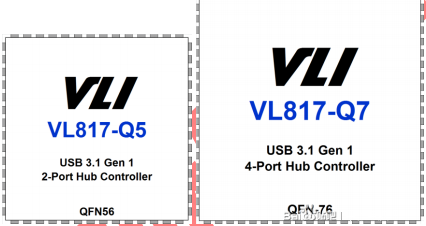

以上即是VL817S与其他型号相同之处,但是总的来说:

1. VL817 C0/B0 与VL817S pin to pin 的产品

2. VL817 C0/B0与 VL817S均为独立FW

3. VL817 S为VL817C0//B0的进阶版本

4. VL817S采用外置LDO供电,

并且VL817-Q7S(A1)性价比更高。

审核编辑:汤梓红

-

芯片

+关注

关注

458文章

51419浏览量

428636 -

控制

+关注

关注

4文章

1017浏览量

122818 -

hub

+关注

关注

1文章

119浏览量

41992

发布评论请先 登录

相关推荐

USB3.0 HUB芯片《VL817-Q7S》威锋HUB芯片

BJT与其他半导体器件的区别

Orin芯片与其他芯片对比

NAND Flash与其他类型存储器的区别

肖特基二极管与其他二极管的区别

PLC如何与其他设备进行通信

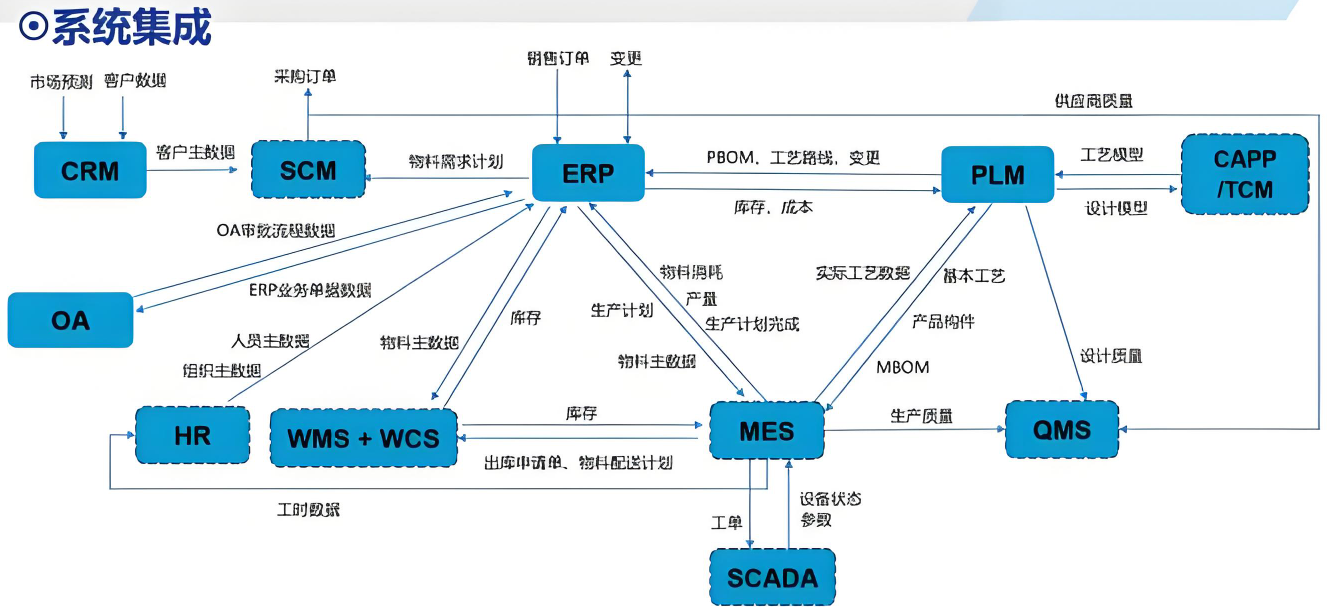

MES管理系统与其他系统的集成

817光耦和2501光耦区别 2501光耦可以代替pc817吗

TLP521与PC817的区别

pc817光耦ABC档有什么区别

如何实现MES系统与其他系统的集成?

DC电源模块与其他电源模块的区别与优势

HUB控制芯片VL817S与其他型号的区别及改动

HUB控制芯片VL817S与其他型号的区别及改动

评论