对于设计者来说,当然希望我们设计的电路的工作频率(在这里如无特别说明,工作频率指FPGA片内的工作频率)尽量高。我们也经常听说用资源换速度,用流水的方式可以提高工作频率,这确实是一个很重要的方法,今天我想进一步去分析该如何提高电路的工作频率。

我们先来分析下是什么影响了电路的工作频率。我们电路的工作频率主要与寄存器到寄存器之间的信号传播时延及clock skew有关。在FPGA内部如果时钟走长线的话,clock skew很小,基本上可以忽略, 在这里为了简单起见,我们只考虑信号的传播时延的因素。信号的传播时延包括寄存器的开关时延、走线时延、经过组合逻辑的时延(这样划分或许不是很准确,不过对分析问题来说应该是没有可以的),要提高电路的工作频率,我们就要在这三个时延中做文章,使其尽可能的小。

我们先来看开关时延,这个时延是由器件物理特性决定的,我们没有办法去改变,所以我们只能通过改变走线方式和减少组合逻辑的方法来提高工作频率。

1.通过改变走线的方式减少时延。以altera的器件为例,我们在quartus里面的timing closure floorplan可以看到有很多条条块块,我们可以将条条块块按行和按列分,每一个条块代表1个LAB,每个LAB里有8个或者是10个LE。它们的走线时延的关系如下:同一个LAB中(最快) < 同列或者同行 < 不同行且不同列。

我们通过给综合器加适当的约束(不可贪心,一般以加5%裕量较为合适,比如电路工作在100Mhz,则加约束加到105Mhz就可以了,贪心效果反而不好,且极大增加综合时间)可以将相关的逻辑在布线时尽量布的靠近一点,从而减少走线的时延。(注:约束的实现不完全是通过改进布局布线方式去提高工作频率,还有其它的改进措施)

2.通过减少组合逻辑的减少时延。上面我们讲了可以通过加约束来提高工作频率,但是我们在做设计之初可万万不可将提高工作频率的美好愿望寄托在加约束上,我们要通过合理的设计去避免出现大的组合逻辑,从而提高电路的工作频率,这才能增强设计的可移植性,才可以使得我们的设计在移植到另一同等速度级别的芯片时还能使用。

我们知道,目前大部分FPGA都基于4输入LUT的,如果一个输出对应的判断条件大于四输入的话就要由多个LUT级联才能完成,这样就引入一级组合逻辑时延,我们要减少组合逻辑,无非就是要输入条件尽可能的少,这样就可以级联的LUT更少,从而减少了组合逻辑引起的时延。

我们平时听说的流水就是一种通过切割大的组合逻辑(在其中插入一级或多级D触发器,从而使寄存器与寄存器之间的组合逻辑减少)来提高工作频率的方法。比如一个32位的计数器,该计数器的进位链很长,必然会降低工作频率,我们可以将其分割成4位和8位的计数,每当4位的计数器计到15后触发一次8位的计数器,这样就实现了计数器的切割,也提高了工作频率。

在状态机中,一般也要将大的计数器移到状态机外,因为计数器这东西一般是经常是大于4输入的,如果再和其它条件一起做为状态的跳变判据的话,必然会增加LUT的级联,从而增大组合逻辑。以一个6输入的计数器为例,我们原希望当计数器计到111100后状态跳变,现在我们将计数器放到状态机外,当计数器计到111011后产生个enable信号去触发状态跳变,这样就将组合逻辑减少了。

上面说的都是可以通过流水的方式切割组合逻辑的情况,但是有些情况下我们是很难去切割组合逻辑的,在这些情况下我们又该怎么做呢?

状态机就是这么一个例子,我们不能通过往状态译码组合逻辑中加入流水。如果我们的设计中有一个几十个状态的状态机,它的状态译码逻辑将非常之巨大,毫无疑问,这极有可能是设计中的关键路径。那我们该怎么做呢?还是老思路,减少组合逻辑。我们可以对状态的输出进行分析,对它们进行重新分类,并根据这个重新定义成一组组小状态机,通过对输入进行选择(case语句)并去触发相应的小状态机,从而实现了将大的状态机切割成小的状态机。在ATA6的规范中(硬盘的标准),输入的命令大概有20十种,每一个命令又对应很多种状态,如果用一个大的状态机(状态套状态)去做那是不可想象的,我们可以通过case语句去对命令进行译码,并触发相应的状态机,这样做下来这一个模块的频率就可以跑得比较高了。

总结:提高工作频率的本质就是要减少寄存器到寄存器的时延,最有效的方法就是避免出现大的组合逻辑,也就是要尽量去满足四输入的条件,减少LUT级联的数量。我们可以通过加约束、流水、切割状态的方法提高工作频率。

原文标题:如何提高FPGA的运行速度

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21729浏览量

603032 -

电路

+关注

关注

172文章

5905浏览量

172152 -

频率

+关注

关注

4文章

1496浏览量

59214

原文标题:如何提高FPGA的运行速度

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

labview通过myrio采样 采样频率过低 该如何提高

工作接地按工作频率而采用的几种接地方式

请教如何提高rkvdec的工作频率?

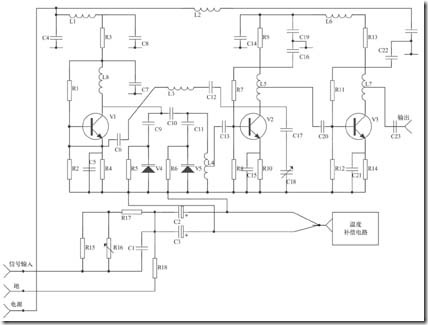

提高变容二极管调频电路频率稳定度的温度补偿方法

该如何提高电路的工作频率

该如何提高电路的工作频率

评论