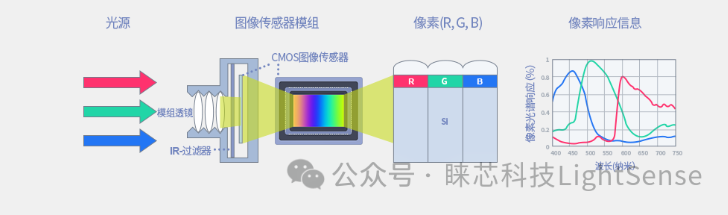

CMOS图像传感器是近些年发展较快的一种新型图像传感器。CMOS图像传感器具有体积小、成本低、重量轻、功耗低、易于控制等优点,已经广泛应用于各种图像采集系统中。机载CMOS成像系统是基于CMOS图像传感器的一种适用于机载应用环境的图像采集系统。可有效解决机载复杂环境下常规工业相机的各种缺陷和应用问题,满足市场的应用需求。FPGA逻辑设计是车载CMOS成像系统的关键设计,本文将探讨关于的CMOS图像传感器的FPGA逻辑设计。

什么是FPGA逻辑设计?

FPGA逻辑设计是本成像系统的工作重点,针对选用的CMOS传感器的技术特点,对各个功能模块进行了设计和优化。FPGA的逻辑设计实现了CMOS传感器的数据采集、图像处理、接口变换等逻辑功能。

FPGA逻辑设计的实现

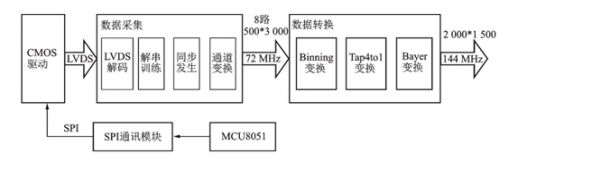

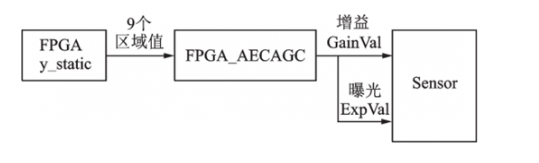

(1)图像采集逻辑设计。图像采集逻辑设计主要包括CMOS图像传感器的驱动设计和传感器原始输出数据的采集与转换设计。图像采集逻辑设计流程框图如图1所示。

图1图像采集逻辑设计流程框图

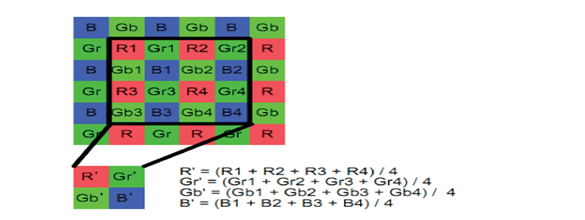

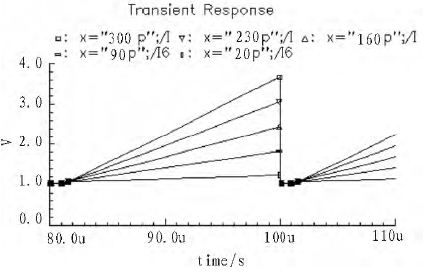

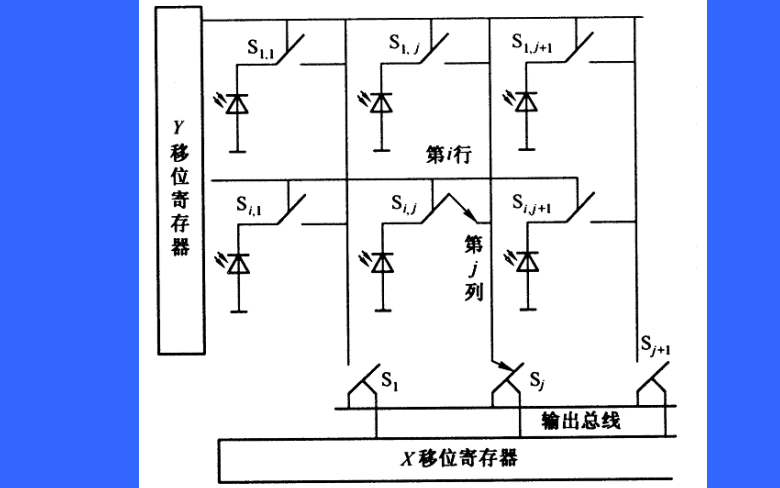

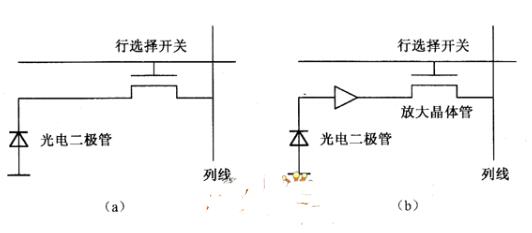

SPI通讯模块Spi_fast_com完成对CMOS的初始化配置,选用了4000×3000矩阵的输出模式,输出10位的LVDS数据。通过Sensor_deser传感器数据采集模块,实现数据流的串行移位解码[3],产生同步控制信号和8路的10bit数据流,数据采集部分包括了LVDS解码、解串训练、同步发生、通道变换等逻辑设计。数据转换中,Binning变换主要实现对传感器数据的均值处理和分辨率调整,图2为Binning算法的基本原理示意。

图2Binning算法原理示意图

Tap4to1变换主要实现4行数据(500点)到标准行长度(2000点)的合并。Bayer变换主要实现Bayer数据域到RGB数据域的转换。由于Bayer数据域中,每个像素单元仅采集单个颜色数据(R,B,Gr/Gb),Bayer变换过程中,使用临近像素单元的其他分量进行近似替代,根据不同的中心坐标,选用不同的替代模板。

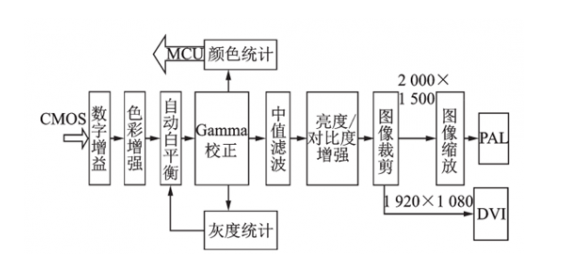

(2)图像处理逻辑设计。图像处理逻辑设计主要完成对采集后数据的图像处理,涉及的图像处理算法包括:数字增益、色彩增强、自动白平衡、Gamma校正、颜色/灰度统计、中值滤波、亮度/对比度增强、图像裁剪、图像缩放。图3为图像处理逻辑设计流程框图。

图3图像处理逻辑设计流程框图

各个图像处理算法均采用流水线式设计,合理优化算法结构,降低资源占用,保证了图像处理算法的实时性。针对流程中的图像缩放需求,设计了不依托外部存储单元的图像缩放核(基于内部行buffer结构),有效缩小系统硬件规模。

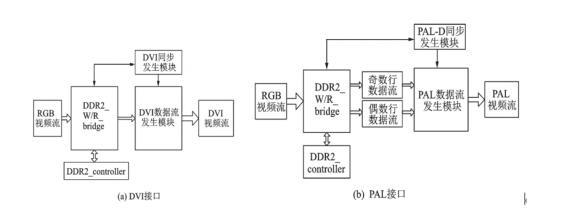

(3)图像接口逻辑设计。图像接口逻辑设计包括高清数字DVI接口和标清模拟PAL接口的逻辑驱动设计,实现成像系统最终显示画面的输出。对于数字DVI接口,需要产生标准的1080P数字信号,逻辑设计包括DDR2的多端口桥接设计和DVI驱动控制设计[5]。图4(a)为DVI接口数据流发生示意图。

图4接口数据流设计流程框图

DVI的同步发生模块控制数据流的同步时序,从DDR2缓存区中读取相应区域的数据,数据流发生模块接收数据后,同步生成DE、HS、VS等同步信号,产生标准的DVI视频流。经DVI编码电路编码后,产生标准DVI输出。对于模拟PAL接口,需对逐行的RGB数据进行转换,按PAL制式输出视频流。采用DDR2缓存(P2I转换)+PAL数据处理的纯逻辑方案,实现输出数据流的重构。逻辑设计主要包括多端口DDR2读写桥接设计和PAL驱动控制设计。基本设计框图如图4(b)。相比数字视频输出显示的DDR2操作,PAL制式输出视频流在DDR2读出操作上有所差别。

(4)自动曝光逻辑设计。在不同环境照度下,成像系统需要控制不同的曝光时间并调节增益系数,以获取合适的图像数据。自动曝光与增益算法即系统对曝光和增益的控制算法,对算法进行了设计开发,对全场景进行了区域分割,分别进行信息统计,算法能够根据场景的统计结果自动完成调整。图5为自动曝光和增益的基本原理图。

图5自动曝光和增益的基本原理图

自动曝光、增益算法总的调节过程可描述为:需要降亮度时,先调增益,再调曝光时间;提高亮度时,先调曝光时间,再调增益。

小结:

将来些年内,基于CMOS图像传感器的影像产品将达到50%以上,很有可能到时CMOS图像传感器将取代CCD而成为行业市场的新宠。由此可见,CMOS摄像机的市场前景非常广阔。CMOS图像传感器还可应用于数字静态摄像机和医用小型摄像机等。

-

FPGA

+关注

关注

1631文章

21806浏览量

606645 -

图像传感器

+关注

关注

68文章

1925浏览量

129750 -

CMOS图像传感器

+关注

关注

10文章

220浏览量

27808

发布评论请先 登录

相关推荐

CMOS图像传感器电路设计

CMOS图像传感器简议

新型CMOS图像传感器设计

IBM进军CMOS图像传感器

CMOS图像传感器的原理参数和CCD图像传感器有什么区别等资料概述

cmos图像传感器结构_cmos图像传感器市场

CMOS图像传感器的FPGA逻辑设计解析

CMOS图像传感器的FPGA逻辑设计解析

评论