前言

随着集成电路尺寸的缩小,以及集成电路工作速率的不断攀升,数据通信网络、微处理器、存储等产品的高速IO接口已经达到几十甚至上百GHz并对静电防护(ESD)越来越严格。然而,较大的ESD防护网络拥有高量级的电容,这对于接口带宽非常不利。是否能通过一种有效的方案,在不减少ESD电容的情况下,有效提升高速接口的带宽呢?

高速接口市场概况

随着市场对5G、大型数据中心、人工智能领域需求的持续增长,要实现超量数据的传输,必然要用到高速接口,这带动了高速接口需求的井喷。 另外,在Memory、MCU、GPU、FPGA等应用领域,传统的高速接口还不能满足现有的传输需求,其能耗、速率还有很大的提升空间,56G高速接口已开始投产,112G高速接口的研发设计也已启动。 与此同时,Foundry的先进工艺节点不断精进突破至7nm、5nm,为高速接口速率提升在物理层面提供了可行性。众多设计公司投入到各种高速接口IP开发中,希望背靠先进工艺,能够让自家高速接口IP应用于集成电路大系统中。

高速接口带宽提升的设计仿真挑战

1.IO接口电容对带宽的恶化

为优化高速接口高频段的信号损耗,设计者通常会采用高灵敏度接收器及均衡器。然而,这些增加的电路模块不可避免地增大了系统功耗,因此我们希望能够找到办法尽可能减小这些IO接口的电容量。 接口电容主要是由ESD防护网络贡献,但是,较大的电压防护裕度导致ESD电容不宜设计得太小。另外,金属互联线和有源器件寄生电容都对IO接口电容带来不利影响,因此设计中的最大挑战在于如何不断减小这些接口电容,或者规避这些影响。

2.传统宽带提升方案的不足

传统的带宽提升方案是Inductive Peaking,即在负载端串接一个片上电感。受电感感抗随频率增加的影响,总的串联阻抗(RD+jwL)也会随频率增加,这样迫使大量电流流经负载电容,实现增益宽带一致性,从而提升工作带宽。 不过这种方案在高频时会有明显的阻抗不连续和回波损耗较差的问题,间接的又拉低了整个3dB工作带宽。目前Inductive Peaking方案最大能提升带宽1.8倍,如果要保证良好带内平坦度,最大只能提升带宽1.6倍,因此带宽提升仍有不足。

3.T-coil带宽提升方案设计难度

对于高速IO接口的带宽提升方案,业界用的比较先进的方案是利用T-coil片上无源器件来实现。不过这种技术的原理及公式推导在2003年才公布于众,很多设计人员还不是很了解。而且T-coil无源器件共有4个指标参数,在设计仿真时,很多设计人员无从下手,不清楚如何设计优化这些关键参数。

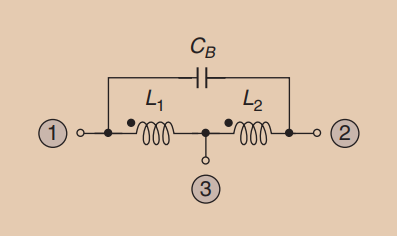

芯和T-coil带宽提升设计仿真解决方案 芯和半导体针对高速IO接口带宽提升的问题,提供了对应的解决方案,即通过设计及仿真片上无源T-coil结构,最大限度地对接口电路实现阻抗、提升3dB带宽。 如图1所示,T-coil是双端口桥式-T网络的一种特例。它由两个互相耦合的电感(两个电感常常对称设计),和一个桥接电容(和电感进行并联谐振,进一步提升带宽)组成,实际设计中还要考虑两个电感的耦合因子、线上插损等因素。 当某个负载加到T-coil电路时,从节点1或2处看到的阻抗比较特殊;同时这两个节点到节点3(一般连接负载电容)的传输函数(Vout/Vin)特性也比较有研究价值。

图1 T-coil拓扑图

1.T-coil参数理论分析

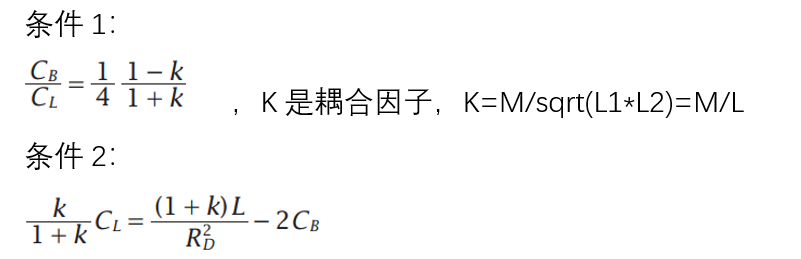

芯和半导体已从设计理论层面对T-coil器件进行大量分析积累,T-coil的关键设计指标是自感L1、L2,耦合系数K,桥接电容Cb。因此首先要对这四个指标对应的等式方程有充分地理解,才能有的放矢地进行器件综合优化。 T-coil传递函数如图2所示,是一个四阶函数,包括2个零点和4个极点(从分子的二次方程和分母的四次方程可看出)。其中,M是L1和L2之间的互感。

图2 T-coil带宽提升系统的传递函数

假设L1=L2=L,并且选择好L的值,使得传递函数中分母的两个零点和分子中2个极点抵消掉。L值的选择,就是要满足下面两个条件式子,如下:

通过两个条件带入四阶传递函数,可以用两个极点抵消2个零点,得到一个二阶传递函数,其方程如下:

芯和半导体通过多次仿真验证并得出结论:当使用阻尼系数ξ=0.866进行计算时,得到T-coil方案能提升2.72倍带宽,而Inductive peaking方案仅提升1.6倍带宽。很显然,采用T-coil的优势巨大。

2.T-coil高效仿真建模

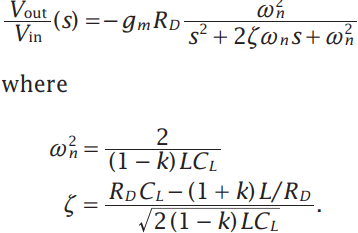

芯和半导体提供了基于神经网络算法的无源器件优化平台iModeler,它内建了丰富的无源器件参数化模板,其中包含了T-coil版图结构。在iModeler软件中调用T-coil模板后,设计者可以进行各种物理尺寸参数化扫描,然后利用4种参数的EM公式进行器件多指标优化。 图3是基于iModeler的T-coil优化流程图,设计者在选择T-coil模板时,也可根据需要添加shielding、dummy等版图结构。

图3 Xpeedic-iModeler的T-coil器件优化流程

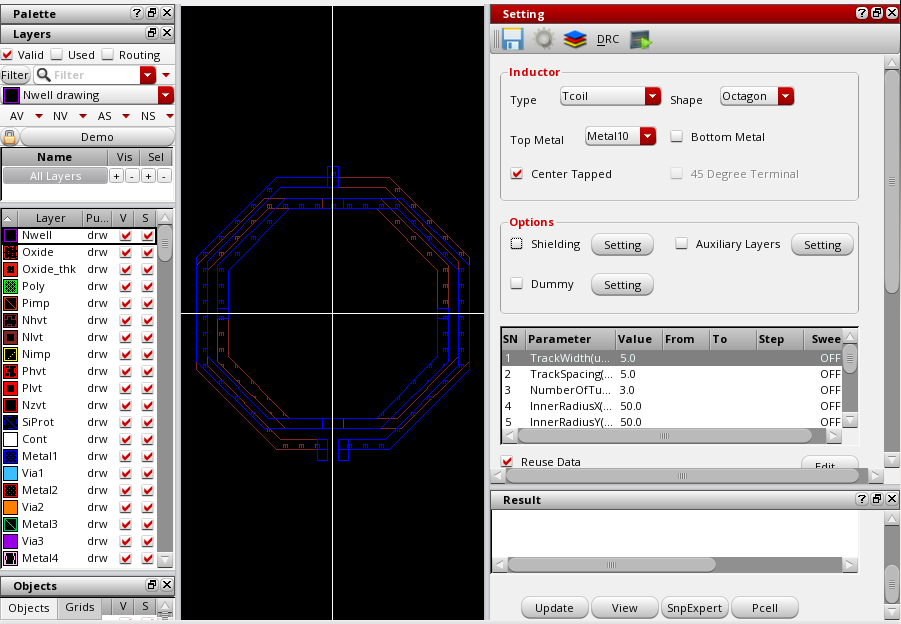

iModeler软件集成于Cadence的Virtuoso环境中,设计人员能快速调用仿真建模流程。通过选择期望的T-coil器件,扫描多个物理尺寸,设计师能得到多个拓扑结构的S参数模型,如下图4界面所示。

图4 T-coil优化扫描界面

3.T-coil仿真后处理

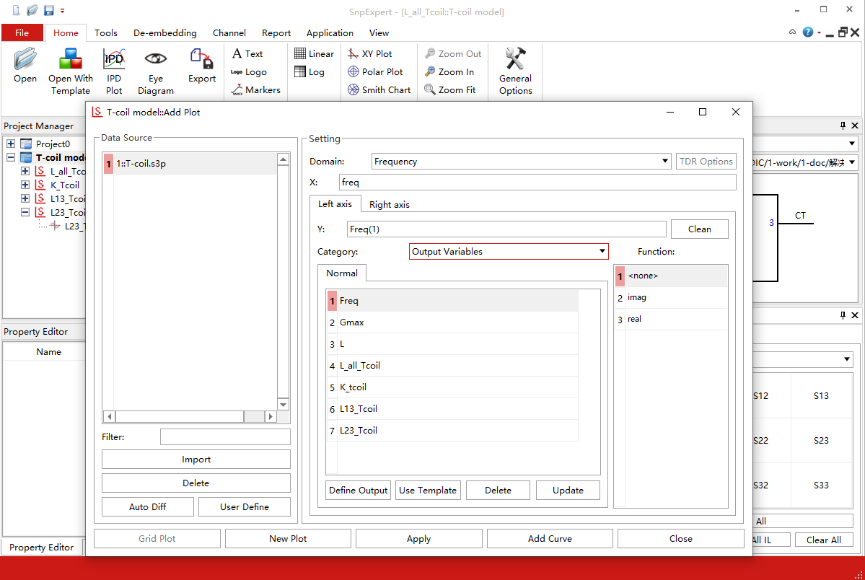

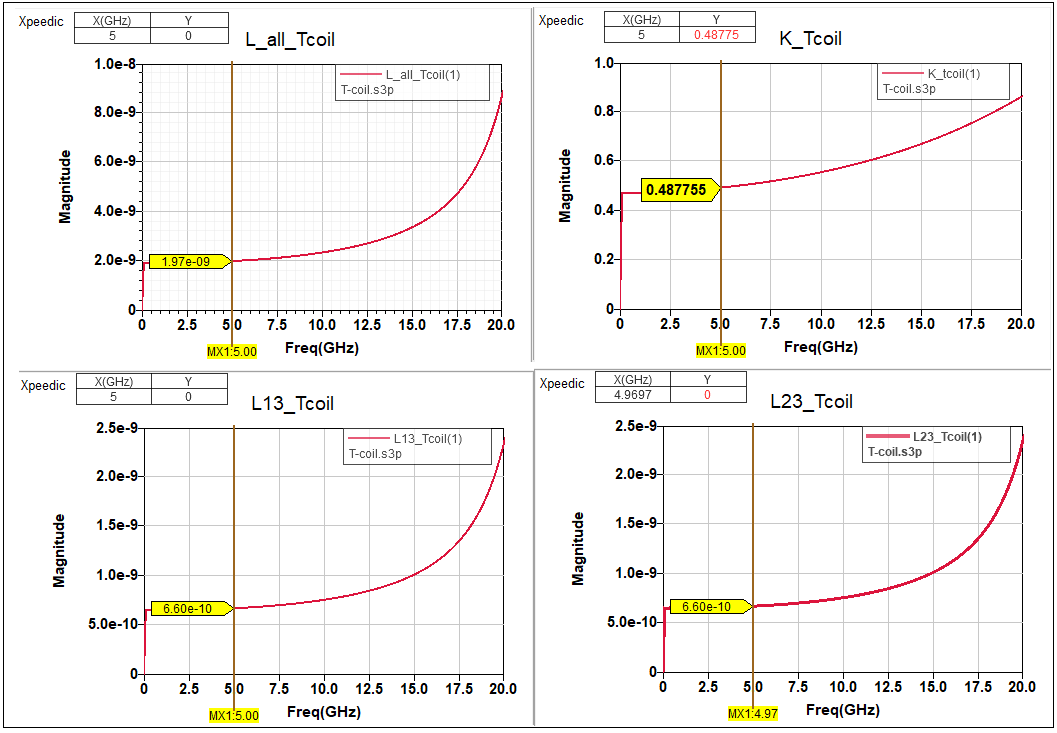

在进行T-coil仿真设计过程中,设计师需要利用电磁场公式对T-coil模型进行迭代分析,观察仿真结果是否满足指标要求。 芯和半导体提供了强大的S参数后处理软件SnpExpert,它内置了丰富的EM公式,通过这些T-coil公式可以快速分析仿真曲线是否符合要求。

图5 内置公式编辑

图6 快速绘制结果曲线

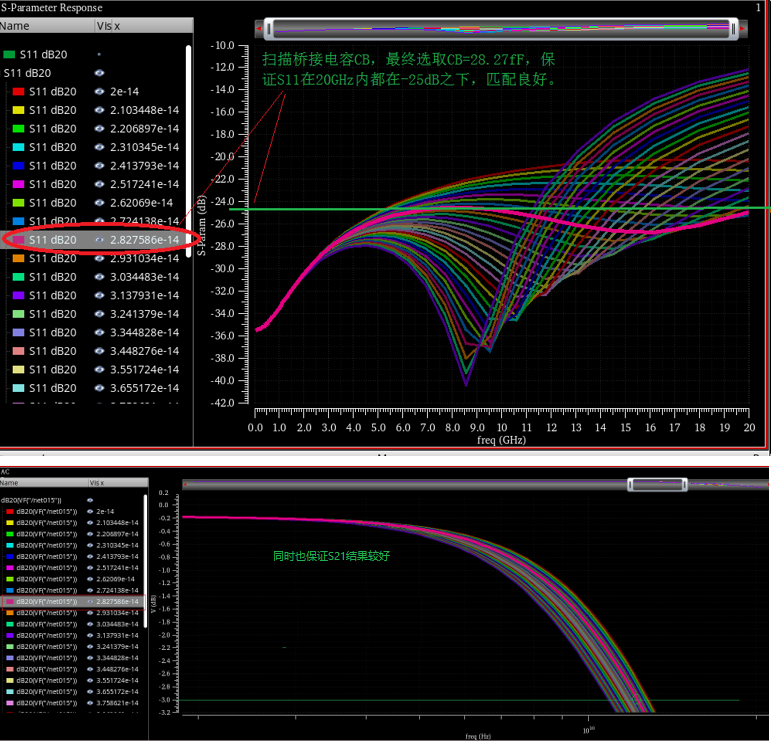

4.桥接电容扫描

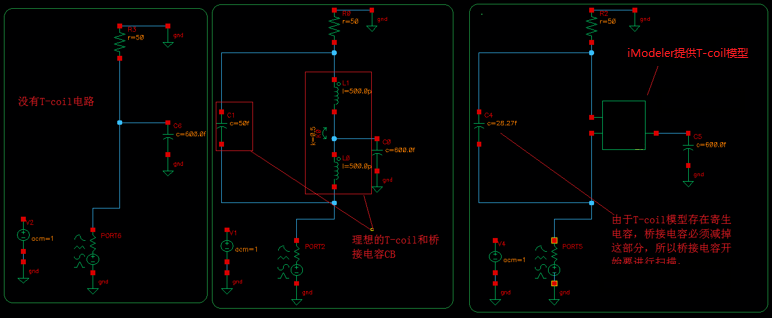

芯和半导体提供的iModeler软件,在完成T-coil设计仿真建模后,能够将T-coil模型同步到Cadence电路设计和仿真环境中。为了验证T-coil方案的效果,我们分别搭建了理想和实际电路进行验证。 理想电路:T-coil和桥接电容Cb都是按照理想元器件进行设置。 实际电路:T-coil是电磁场仿真生成的模型。由于T-coil模型中已经存在线圈间耦合电容,所以桥接电容Cb要扣除这部分影响,否则结果有偏差。因此需要对Cb进行变量扫描,来找出最优值。 图7从左到右展示了三种验证电路,分别为无T-coil原始电路、含理想T-coil电路、基于仿真模型T-coil电路进。

图7 T-coil验证

图8是对实际电路中桥接电容Cb的扫描结果,分别为输入端的S11(上图)和负载电容处的3dB带宽(下图)。图中可见,不同桥接电容对应的S参数曲线,需要根据插损和回损图选择最优的结果。

图8 扫描结果

总结

本文首先从高速接口切入,讲述了负载电容对工作带宽的负面影响,并探讨了带宽提升有哪些途径,接着对T-coil的参数公式进行推导,从理论的角度提出了最优的T-coil解决方案。最后使用芯片无源器件建模软件iModeler进行方案的实例验证。如果还想对接口电路性能做进一步优化,设计者可以参考更为详细的文档,从电路层面进行调整,然后再用iModeler进行模型实现,并按照这种思路反复迭代直至满足指标。

审核编辑 :李倩

-

电容

+关注

关注

99文章

5997浏览量

150021 -

高速接口

+关注

关注

1文章

44浏览量

14762 -

无源器件

+关注

关注

5文章

193浏览量

23548

原文标题:【解决方案】高速接口利用T-coil的带宽提升解决方案

文章出处:【微信号:Xpeedic,微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

dp接口适配器常见问题及解决方案

高速公路监测解决方案是怎样的

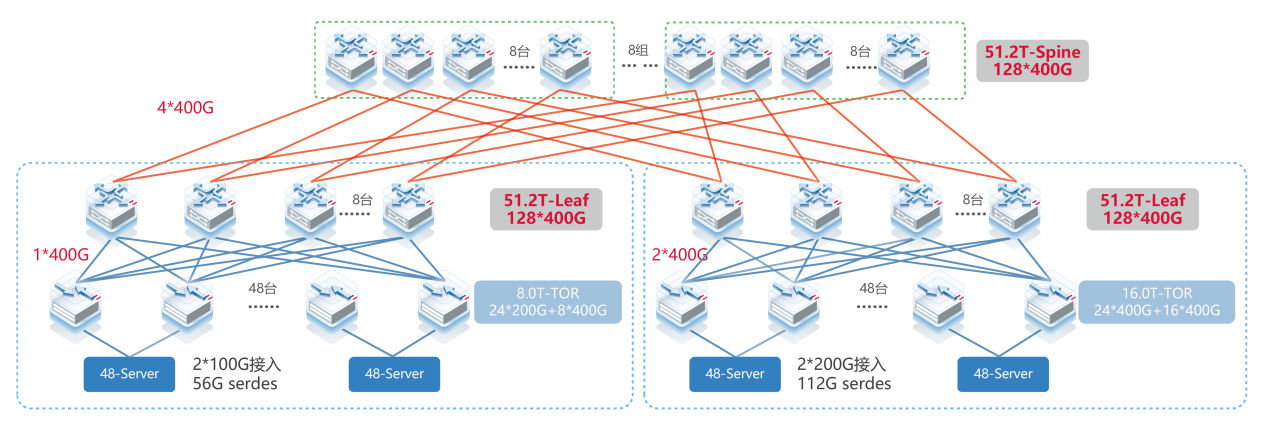

51.2T交换机网络解决方案

TPD4E110 4通道保护解决方案,用于超高速(高达6GBPS)接口数据表

TPD2E009高速(6 Gbps)差分接口双通道ESD解决方案

高速接口利用T-coil的带宽提升解决方案

高速接口利用T-coil的带宽提升解决方案

评论